A Soft Commutated Neutral-Point-Clamped (npc) Inverter

advertisement

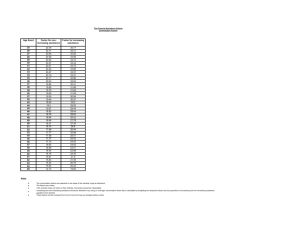

A Soft Commutated Neutral-Point-Clamped (NPC)Inverter: Theory and Experimentation Xiaomiiig Yuan and Ivo Barbi Power Electronics Institute, Federal University of Santa Catarina P.O.Box: 5 1 19, CEP: 88040-970, Florianopolis-SC-BRAZIL Fax: (55)4823 15422; Tel: (55)4823 19204; E-mail: ivo@inep.ufsc.br Abstract - A soft commutation circuit aimed to substitute for the conventional snubber in GTO NPC inverter is presented in this paper. The sniall rating lossless auxiliary branch creates soft switching conditions for the main devices without having to subject them to extra voltagehrrent spikes or any modulation constraints. Hence it allows for considerable extension of the power range and the frequency range of the main installation. Operation, analysis, and designing of the circuit as well as the experimental results from a prototype are detailed in the paper. 1. INTRODUCTION In the recent decade, GTO NPC (Neutral-Point-Clamped) inverter [I] has been finding growing applications in traction and stationary drive areas, due to mainly the expanded capacity with existing devices without problematic series association of devices [2]-[3]. The power and in particular frequency range of such installation, however, have been meeting with a bottleneck introduced by the snubber network required [3]. Aside froin the derating of devices dealing with voltage/current spikes arising froin the turn-on/turn-off snubber interactions, the switching frequency range is especially limited to 300Hz-500Hz due to the significant snubber loss, which is proportional to the switching frequency operated and more than proportional to the power processed in the main installation. Regenerative snubber leads to improvements to the extent allowed by the complexity of the recovery choppers [4], while device derating remains demanded. In addition, the series reactor in the turn-on path and the polarizing diode in the turn-off path cause extra onstate loss and turn-off spike that further offset its attractions. In the meanwhile, a few zero voltage switching schemes have been developed for the two-level high power inverter over the past decade, which promises superior performance over the conventional snubber. Among which the Auxiliary Resonant Commutated Pole (ARCP) [5]-[7] has been mostly applauded in the literature for its sinal1 rating auxiliary circuitry and full PWM capability. However, the current transducers required €or load current and resonant inductor current monitoring give rise to cost and reliability problems [SI. Simplified control [9] aiming to get rid of the “boost” stage [7] and the current transducers results in considerable loss. Zero voltage switching is therefore lost. 0-7803-4340-9/98/$10.000 1998 IEEE. Such siinplification, however, is obtainable with the True-PWM-Pole scheme [lO]-[l I]. Instead of using the center-tap capacitor for ;acquiring the auxiliary voltage source for the resonance, a auto-transformer is installed in the TruePWM-Pole with which a higher value can be synthesized that guarantees zero voltage switching regardless of the losses. Several previous publications have associated the NPC inverter with soft switching techniques. Besides the early thyristorized three-state inverter [ 121 which works actually with zero current switching, zero voltage switching achieved with resonant DC link [13] and ARCP [14] have also been investigated. The auxiliary devices in [12] and [14], however, are subject to higher blocking voltage than the main devices, which suggests a potential shortcoming of the proposals. This paper deals with using the True-PW-Pole as an alternative of conventional snubber for the NPC inverter. With the assistance of the small rating lossless auxiliary circuitry, zero voltage switching is achieved with the main devices without imposing any modulation constraints or any extra control complexities. Auxiliary devices block yet the same voltage as the main devices. 11. CIRCUIT PROPOSED AND ITS OPERATION The circuit proposed is shown in Fig.1 consisting of the NPC main circuit and two auxiliary branches. The first auxiliary branch (Sa,, Sa,:) assists the commutation of the first switching cell (S,, S,) and forms the first resonant pole; whereas the second auxiliary branch (Sa2, S,,) assists the commutation of the second switching cell (S2, S,) and forms the second resonant pole. The inner parallel capacitors (Cr3, C,) installed across the clamping diodes (Dc,, D,;) mitigate the over-voltage problem across the inner main switches (S2, S,> which is resulted mainly from the discharging of the clamping path inductances during turn-off processec, of the inner switches. When these inductances are neglected, the two switching cells and therefore the two resonant poles can be regarded decoupled and independent from each other. The operation of one pole is analogous to the other. 537 Fig.1. The proposed soft coinmutated NPC inverter, consisting of a main NPC circuit and two auxiliary branches. (N,=N,'=kN,=kN,', k<1/2, C,,=C,=C,,=C, =C,, L,,,=L,,=LJ Table I. Switching State of the Main NPC Inverter step1 (tn-tl): Circuit steady state. D,+D, carries the load current. Output voltage VA0=VdC/2. step2 (t,-t2): Turn-on S,, and turn-off SI at t, simultaneously, which initiates conduction of Dal, magnetization of LrI3and current decreasing in D,. Voltage of kV,,/2 is reflected on N, setting-up a voltage source of V,,(I-k)/2 forcing the resonance followed. step3 (t2-t3): D, is blocked at t, when i,,,, rises to the load current level. After which C,, is charged while C,, is discharged. step4 (t3-t,): C,, is fully discharged to vdc/2 at t,. D,, begins conduction. And S, gating signal is released. step5 (t,-t,): L,,, current reaches load current at t,, after which S,+D,, begins carrying current. step 6 (t5-t6):Current through/voltage across N, extinguish at t,. S,+D,, carries the full load current. Sa, gating signal can be withdrawn. Circuit then reaches another steady state. And the output voltage V,,=O. Process(d): Negative commutation: load current, S,+D,, to D,+D, step7 (t6-t7): Turn-on Sa, and turn-off S, at t6 simultaneously which causes conduction of Da3. Voltage of kVdJ2 is ON ON OFF OFF therefore established on N2 resulting in a voltage source of OFF ON ON OFF Vdc(1-k)/2 forcing the resonance. Load current moves from According to the switching state of the main NPC inverter S,+D,, to D, charging C,, and discharging Crl. shown in Table I, when the first pole is active, the second step8 (t,-t8): C,, gets fully discharged at t, after which current pole will be at rest (S, ON, S, OFF and V,,=V&, VCr2=O). flowing in C,, and C,, transfers immediately to D,. SI gating signal is then released. Four commutation processes can hence be distinguished: step9 (t8-t9):Voltage acrosdcurrent through L,,, dies out at t,, from which instant D,+D, carries the full load current. S, (a) Positive load current, D,,+S, to S,+S, commutation; gating signal can then be withdrawn. Circuit arrives at the (b) Positive load current, Sl+S, to Dc,+S, commutation; original steady state. Output voltage v,o=vdc/2. ( c ) Negative load current, D,+D, to S,+D,, commutation; (d) Negative load current, S3+Dc2to D,+D, commutation. The operation step diagrams and the relevant theoretical waveforms are illustrated in Fig.2 and Fig.3 respectively. For simplicity, only commutation details for processes (c) This process can also be represented in a phase plane as and (d) are detailed in the following. For which the next shown in Fig.4. assumptions are made first: 0 -W2 (a) NPC neutral potential is stable during normal operation. Load current is constant during the commutation interval. (b) Main switch turn-off and auxiliary switch turn-on happen at the same instant. Main switch turn-on signal is released when the detected voltage from the voltage monitor installed for each main switch declines to zero. Auxiliary switch conduction duration covers the whole commutation interval. (c) Auto-transformer ratio is set to ensure the pole voltage swinging to the rail value during the commutation. Process(c): Negative commutation: load current, D,+D, to S,+D,, To summarize, in the proposed circuit, the main switches work with soft turn-on (zero voltage switching) and snubbed turn-off, while the main diodes (freewheeling and clamping) work with soft tum-off (zero current switching) and hard turn-on. Unlike the case in the conventional snubber where the snubbing capacitance is limited by the snubber loss, the parallel capacitance in the present case can be optimized for the switch tum-off loss. However, the main diode is characteristic of snap-on which is similar to the system assisted with conventional snubber. The loss accrued in such process is dependent on the property of the diode itself. In the meantime, all the auxiliary devices including both switches and diodes work with soft turn-off (zero current 538 I A Step 1: to-ti step 2: t,-t, Step 4: t,-t, step 5: t,-t, I I step 3 : t2-t3 ' I Step 7: &-t, step 8: t7-tR ~ I step 9: t8-t9 Fig.2. Operation step diagrams for coinmutation processes (c) and (d): D,+D, to S,+Dc, and S,+Da to D,+D,. t .~ . I . . * . Fig.3. Theoretical waveforms for commutation processes (c) and (d) during a switching period. (4 Equations (1) and (2) are graphically shown in Fig.S(a)(b). Fig.4. Phase plane of the resonance between L,,, and C,,/C, for cominutation processes ( c ) and (d). 0 05 I 2 I 5 25 3 ~~ I1.d (a) diode to switch commutation switching). Moreover, despite of the bridge configuration of the auxiliary devices, the turn-on of these devices are actually snubbed by the resonant inductor. Upon turn-on of a auxiliary switch, the opposite freewheeling diode carries no current and therefore its reverse recovery contribution can be neglected. Auto-transformer excitation are reset to zero after each commutation and causes no magnetic accumulation. In particular, the extra freedom in synthesizing the auxiliary voltage source for the resonance offered by the autotransformer greatly simplifies the control. 0 0t.w 2017 11 5 I I 5 2 25 ‘Isad @)switch to diode Commutation 111. COMMUTATION ANALYSIS The following assumptions are made in the analysis: e Resonant frequency wo=-- 1 d2C4’ - resonant impedance Unit current ;= i z,/ ( r ~ ~ ~ / unit 2 ) , voltage unit time I = coot. Fig.5. Variations of commutation durations t,, and tar,with load current and auto-transformer ratio. . B. Resonant Inductor Peak Current Stress V=V/(V&/~), For diode to switch commutation, the unit value of the resonant inductor peak current iLrplis expressed by (3): (3) A. Total Commutation Duration For diode to switch commutation, the unit value of the commutation duration t s 1 = t 5 - t 1 is given (l): For switch to diode commutation, the unit value ofthe total cominutation duration t R 6 = t g - t g is given by (2): F~~ switch to diode commutation, the unit value of the can be expressed by (4): resonant inductor peak current Auxiliary switch peak current during diode to switch - - (isapp,) and switch to diode (is,,,) represented by ( 5 ) and ( 6 ) : 540 commutations are then (5) Equations ( 3 ) and (4) are graphically shown in Fig.G(a)(b). where: 3 65 1125 26 iLlpl 2075 =(/- 5, 155 -G)/k I025 n r "1 n I 25 2 The above relationships are shown in Fig.7(a)(b). The resonant inductor RMS current is then given in (9): 3 IIh"d (a) diode to switch cominutation (9) The auxiliary switch RMS current during diode to switch and switch to diode commutation are given by (1 0) and (1 1): i 0 I, 1 I I' 2 2, Sunrni s ' bml k'iLrnrms -- (b) switch to diode commutation * -o- Fig.6. Variations of the resonant inductor peak currents with load current and auto-transformer ratio. C. Resonant Inductor RA4S Current Stress I k=ll.3,T=911 k=ll4, T=9O h=O 5 , T=90 h=ll3, T=45 h=11.4, T=45 Lmnns The resonant inductor RMS current stress over switching -~ period resulted from diode to switch commutation j , , , , , , can be given by (7): 2 I i iond (7) (a) Diode to switch commutation where: ' Lmmms k I-k L , = (=+ J E ) i k L, = 7r - U cos(-) Similarly, the resonant inductor RMS current resulted from switch to diode commutationi,,m,,, is given by (8): ' land (b) Switch to diode commutation Fig.7. Variations of resonant inductor RMS currents with load current, auto-transformer ratio and switching period. 541 IV. DESIGN METHODOLOGY counting on the inherent self-balancing mechanism 1171. Specifications and parameters are given in Table 11: A. Auto-Transformer Ratio k Table 11. Prototype specifications and parameters P0=3.2kW, Vdc=720V,VO=14OV. 10=22.8A. I Specifications: I To ensure zero voltage switching in the presence of losses (device conduction loss, resonant inductor loss and resonant capacitor loss etc.), auto-transformer ratio k should meet (12): - Parameters: 1 -(1-k)--vdc 2 Where 'dc 2--vdc 4 e=* I< 4 4Q (12) 2 and R represents the equivalent resistance in n (13) 8Q I Four IGBT modules (SKMSOGB123D,1200V/50A) are employed as the main and auxiliary switches. Eight ultra-fast HFA30TA60C (600V/30A) diodes work as the auxiliary diodes. Two storage capacitors C , and C, each rated at 360V/33OOuF form the center tap. Output second order filter: Lf=6.5mH, Cf=12uF (not shown). the resonance loop. Equation (12) can be simplified to (13): - 1 k<----- k=0.45, T=155uS, C1=0.luF, L1=15uH, T,,=15uS, T,, =25uS. Fig.8 shows the three level output of the inverter. Fig.9 shows the output voltage and current after filtering. Fig.lO(a)(d) show the typical four commutation processes. B. Resonant Frequency oo The resonant frequency can be set by optimizing the RMS stress of the auxiliary switch according to Fig.7(a) based on the switching frequency of the system. C. Resonant Capacitor C, and Resonant Inductor Lr The resonant capacitor should be optimized for the main switch turn-off loss[l5]. Based on the resonant frequency and the resonant capacitance, the resonant inductance is decided. 100VIDiv; 200uSIDiv Fig.8. The three level output of the NPC inverter. D.Auxiliary Switch Gating Signal Width Tsa and Minimum P WM ON/OFF Time T p p y ~ The minimum width of the auxiliary switch gating signal must be set above the maximum value of the commutation duration. In the same sense, the minimum PWM ON/OFF time (t& in Fig.3) should also be set above this value. 100VIDiv; 2OAiDiv; SmSiDiv Fig.9. Output voltage/current after filtering. E. Rating of the Auxiliary Switch Due to the zero current switching in the auxiliary circuitry and due also to the high switching frequency with respect to the thermal inertia of the device, the rating of the auxiliary switch could be chosen according to (10). However, auxiliary switch peak current decided by (5) should not exceed the device peak output current rating. (a) Positive load current, Dcl to SI commutation V. EXPERIMENTAL RESULTS The experimental IGBT half bridge prototype employs a sinusoidal modulating signal and two vertically shifted carriers for the main circuit modulation [16]. The neutral potential is not actively controlled and instead is stabilized 542 IOOViDiv JAIDiv, IOuSlDiv (b) Positive load current, SI to Dcl commutation The proposed technique is especially suitable for some high power advanced applications such as high speed drive or active filter contributing to reduce the losses and extend the power and frequency range. REFERENCES (c) Negative load cunent, S3 to D1 coininntation IOOVIDiv, SNDIV, IOuSIDiv (d) Negative load current, D1 to S 3 commutation Fig 10 Four typical commutation processes of the first resonant pole. Fig.11 shows the auxiliary switch voltage and resonant inductor current waveforms at load current iload=8A. For switch to diode commutation, with a theoretical commutation duration of 4.6uS and a resonant peak current of 17.5A, the experimental values are 4. IUS and 14SA respectively. For diode to switch commutation, with a theoretical commutation duration of 7.3uS and a resonant peak current of 32.5A, the experimental values are 7uS and 27A respectively. U U - J 100ViDiv. lONDiv, 2OuSiDiv Fig.11. Auxiliary switch voltage and resonant inductor current VI. CONCLUSIONS From the theoretical and experimental studies reported above, the following conclusions are drawn: The proposed technique guarantees soft commutation of the main circuitry as well as the auxiliary circuitry without incurring any voltage/current spikes over the main device. The proposed technique assumes no modulation limitation except for a small duty cycle loss comparable to that required by the conventional snubber. The parallel capacitor arrangement enhances the control of the main device voltage, whereas the auxiliary branch arrangement allows also tight control o f the auxiliary device voltage. Validity of the theoretical analysis is proved. [I] A. Nabae, I. Takahashi and H. Akagi, “A new neutral point clamped PWM inverter”, Rec. of IEEE Ind. App. Society Annual Meeting, pp.761-766, 1980. [2] H. Stemmler, “Power electronics in electric traction applications”, Rec. of Int. Conf. on Ind. Electronics, Control and Instrumentation, pp.2126, 1995. [3] H. Stemmler and P.Guggenbach, “Configurations of high power voltage source inverter drives”, Rec. of European Power Electronics and App. Conf., pp.7-14, 1993. [4] H. Okayama and T. Tsuchiya, “A novel regenerative snubber circuit for three-level GTO inverters”, Mitsubishi Electric ADVANCE, pp.24-26, June 1997. [5] G. Bingen, “Utilisation de Transistors a fort courant et tension elevee”, Rec. of European Power Electronics and App. Conf., pp.1.15-1.20, 1987. [6] W. McMurray, “Resonant snubbers with auxiliary switches”, IEEE Trans. on Ind. App., pp. 355-362, Vo1.29, No.2, 1993. [7] R. W. De Doncker and J. P. Lyons, “The auxiliary resonant commutated pole inverter”, Rec. of IEEE Ind. App. Society Annual Meeting, pp. 1228-1235, 1990. [8] K. Iida et al, “The influence of the conducting inductance in the auxiliary resonant commutated pole inverter”, Record of IEEE Powei Electronics Specialists Conf., pp. 1238-1245, 1997. [9] H. J. Beukes, J. H. R. Enslin and R. Spee, “Integrated active snubber for high power IGBT moodules”, Rec. of IEEE Power Electronics Specialists Conf., pp.161-167, 1997. [IO] I. Barbi and D. C. Martins, “A True-PWM Zero voltage switching pole with very low additional RMS current stress”, Rec. of IEEE Power Electronics Speciafists Conf., pp.261-267, 1991. [ l l ] L. L. Erhartt, K. Edelmoser, M. Sedlacek and F. C. Zach, “A novel low-loss switching method for converters using turn-off power switches (IGBTs, GTOs)”, Rec. of European Power Electronics and Applications Conf., pp. 46-5 1, 1993. [12] J. Holtz and S. Stadtfeld, “An economic very high power PWM inverter for induction motor drives”, Rec. of European Power Electronics and App. Conf., pp.375-380, 1985. [I31 W. Yi and G. H. Cho, “Novel snubberless three-level GTO inverter with dual quasi-resonant DC-link”, Rec. of IEEE Power Electronics Specialists Conf., 1993, pp.880-884. [14] J . G. Cho, J. W. Baek, D. W. Yo0 and C. Y. Won, “Three level auxiliary resonant commutated pole inverter for high power applications”, Rec. of IEEE Power Electronics Specialists Conf., pp. 1019-1026, 1996 [15] R. L. Steigerwald, R. W. De Doncker and M. Kheraluwala, “A comparison of high power DC-DC soft switched converter topologies”, IEEE Trans. on Ind. App., Vol. 32, No. 5, pp.1139-1145, Sep./Oct. 1996. [I 61 A. Rufer, “An aid in the teaching of multilevel inverters for high power applications”, Rec. of IEEE Power Electronics Specialists Conf., pp.347-352, 1995. [I71 G. Scheuer and H. Stemmier, “Analysis of a three level VSI neutral point control for fundamental frequency modulated SVC applications”, Rec. of 6th International Conference on AC and DC Transmission, London, March 1996. 543