Cryogenics 49 (2009) 615–619

Contents lists available at ScienceDirect

Cryogenics

journal homepage: www.elsevier.com/locate/cryogenics

Fixed-gain CMOS differential amplifiers with no external feedback for a wide

temperature range

Vratislav Michal a, Geoffroy Klisnick b, Gérard Sou b, Michel Redon b, Alain J. Kreisler a,*, Annick F. Dégardin a

a

b

Laboratoire de Génie Electrique de Paris, SUPELEC/LGEP; CNRS/UMR 8507; UPMC Univ Paris 06; Univ Paris Sud 11; Gif-sur-Yvette, France

Laboratoire d’Electronique et d’Electromagnétisme, UPMC Univ Paris 06/L2E/EA 2385; Paris; France

a r t i c l e

i n f o

Article history:

Received 31 July 2008

Received in revised form 28 November 2008

Accepted 27 December 2008

Keywords:

D. Cryoelectronics

Fixed-gain amplifiers

CMOS

D. Instrumentation

a b s t r a c t

We present original CMOS amplifiers designed for the DC to 10 MHz frequency range and operating in the

70–380 K temperature range. Aimed applications concern readout circuitry to be associated with THz

bolometric pixels (either high-Tc superconducting or uncooled semiconducting), which require accuracy,

low noise and low power consumption. Two designs are described that both exhibit high fixed-gain

(40 dB) in a feedback-free architecture, which is based on a new low-transconductance composite transistor for an accurate control of this gain. Both amplifiers have been realized in a regular 0.35 lm CMOS

process and tested in the 4.2–380 K temperature range, exhibiting good agreement between designed

and measured characteristics.

Ó 2009 Elsevier Ltd. All rights reserved.

1. Introduction

The most simple and widespread approach to design a fixedgain differential-input amplifier consists in using an operational

amplifier, the gain being set by an external resistive feedback network. This common approach follows from well-known reasons

such as accurate gain setting, for instance. On the other hand, the

use of feedback can lead to limitations, e.g. slower transient response (slew rate) and frequency bandwidth reduction, arising

from frequency compensation that ensures stability of the

closed-loop amplifier [1]. Moreover, this conventional design with

operational amplifier can introduce additional noise generated by

the feedback network.

A feedback-free architecture, as used by Comer [2], would allow

avoiding these effects. Besides, for a differential-input amplifier,

avoiding feedback resistances leads to very high input impedance

which in a regular approach would require an instrumentation

amplifier. However, the absence of feedback is paid by degradation

of some parameters, such as the linearity or output resistance.

The pros and cons should indeed be considered specifically for a

given application. Being concerned with readout circuitry for

bolometer arrays (either high-Tc superconducting or uncooled

semiconducting), our requirements were: differential-input, high

gain accuracy over a wide temperature range, high input impedance, low noise and low power consumption. These led us to

* Corresponding author. Tel.: +33 (0)1 69 85 16 51/16 33; fax: +33 (0)1 69 41 83

18.

E-mail address: Alain.Kreisler@supelec.fr (A.J. Kreisler).

0011-2275/$ - see front matter Ó 2009 Elsevier Ltd. All rights reserved.

doi:10.1016/j.cryogenics.2008.12.014

consider a feedback-free architecture, with the gain set in the

structure itself.

In the following, variable temperature measurements of MOS

transistor parameters to improve our design tools will be presented in Section 2. The low-transconductance composite transistor structure, which is at the heart of our approach, will be

discussed in Section 3. Two amplifier architectures will be presented: amplifier with the gain set by transistor geometry, taking

advantage of the generally excellent matching properties of CMOS

devices (Section 4) and linearized amplifier with temperature compensation of voltage gain (Section 5). For each architecture, experimental results of CMOS circuits realized in a regular CMOS

0.35 lm process are also included.

2. MOS transistor temperature behaviour

Let us briefly examine the temperature behaviour of a MOS

transistor which allows to optimize the amplifier presented in Section 5, in the 70–380 K temperature range. The drain current of an

NMOS transistor in the saturation region is classically given by:

ID ¼

lC OX W

2

L

ðV GS V TH Þ2 ;

ð1Þ

where l is the effective low field surface mobility, COX the gate

oxide capacitance, W/L the device width to length ratio, VGS the

transistor gate-source input voltage and VTH the threshold voltage

referenced to the source. We also define the gain factor

KP(P,N) = lCOX and the transistor gain b = l COX W/L. The two temperature-dependent parameters are:

616

V. Michal et al. / Cryogenics 49 (2009) 615–619

α2

Table 1

Parameters of PMOS 100 lm/10 lm transistor fabricated in 0.35 lm CMOS process.

KPP (lA/V2)

Type/temperature

6

Simulation/296 K

Measurement/296 K

Measurementa/77 K

a

20.67 10

21.63 106

72.43 106

:

1

VTH (V)

0.965

0.953

1.405

Simulation results at 77 K are not presented as the accuracy was insufficient.

iD

the effective low field surface mobility referred to l (T0), the

mobility at room temperature T0 [3,4]:

lðTÞ ¼ lðT 0 ÞðT=T 0 Þx ;

i3

i4

ð2Þ

the threshold voltage:

V TH ðTÞ ¼ V TH ðT 0 Þ½1 þ aTH ðT T 0 Þ;

ð3Þ

1

α1

:

where aTH is the threshold voltage thermal coefficient:

aTH ¼ V 1

TH ðdV TH =dTÞ:

From (1)–(3), the general first order temperature model for the saturated NMOS transistor is obtained as (with KPN defined at T0):

ID ¼

K PN

T

T0

2

x

W

½V GS V TH ðT 0 Þ ð1 þ aTH ðT T 0 ÞÞ2 :

L

3. Design approach

3.1. Classical approach for fixed-gain amplifier design

One example of a fixed voltage gain amplifier currently designed in CMOS technology is the common source amplifier with

the driving transistor TD of the N-channel type for instance and

the load (diode connected) transistor TL of the P-channel type.

The voltage gain GV of this amplifier can then be written using

the well-known transconductance ratio as [3]:

sffiffiffiffiffiffiffiffi sffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi

V OUT

g

K PN

W D =LD

¼ mD ¼ ;

V IN

g mL

K PP

W L =LL

a1 ¼ ðW 4 =L4 Þ=ðW 3 =L3 Þ; and a2 ¼ ðW 1 =L1 Þ=ðW 5 =L5 Þ:

ð7Þ

The drain current ID of T1 can be then written as:

ð5Þ

Results from measurements performed at room and low temperatures and simulation at room temperature (BSIM3 model) on a

PMOS transistor (W = 100 lm/L = 10 lm) are collected in Table 1.

The thermal coefficients were extracted using (2)–(4) as: x = 0.90,

aTH = 2.163 mK1 and dVTH/dT = 2.06 mV K1.

GV ¼

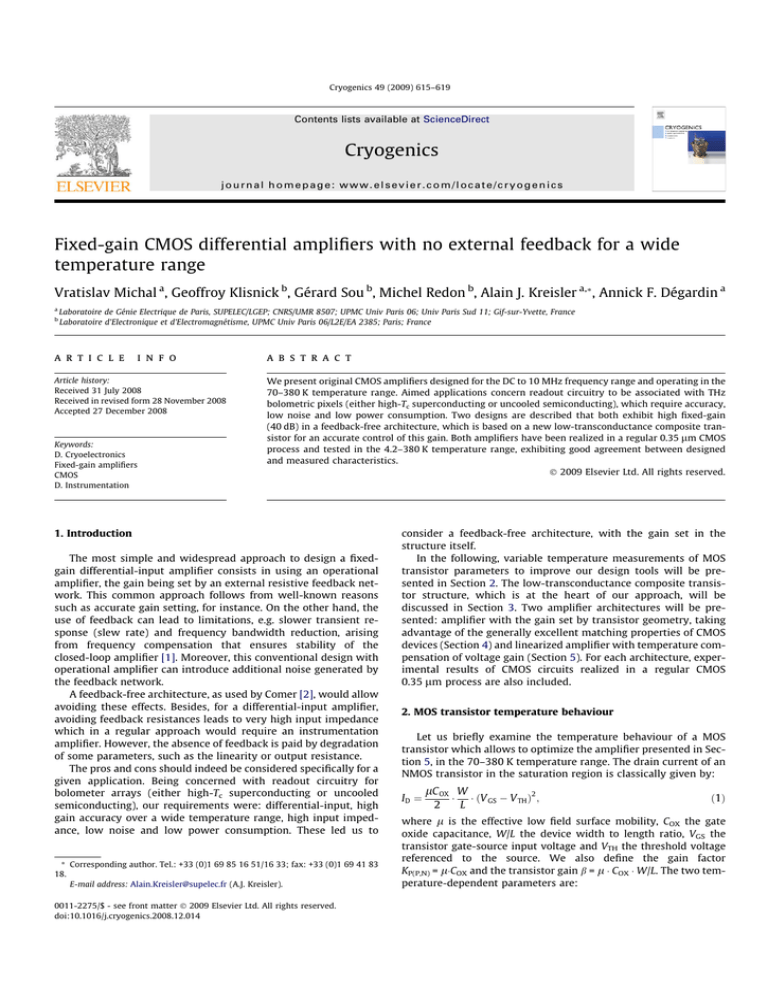

Fig. 1. Low-transconductance composite transistor.

ð4Þ

ð6Þ

where KPN, WD/LD, KPP and WL/LL refer to the TD and TL transistors,

respectively. We can see that GV is fixed only by transistor dimensions and by the KPN/KPP ratio, which is in fact related to the ratio

of electron to hole mobilities [3]. The gain therefore depends on

accurate transistor dimension ratios, whereas the KPN/KPP ratio

introduces some uncertainty. In this way, only a fixed-gain of a

few dB can be realized with reasonable transistor dimensions [2].

ID ¼ a1 a2 g m2 V OUT ;

ð8Þ

where VOUT = VGS2. The equivalent transconductance g 0m is given by:

g 0m

¼

sffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi

W

a1 a2 2 K PP 2 ID :

L2

pffiffiffiffiffiffiffiffiffiffi

We can see that the equivalent transconductance g 0m of Fig. 1 composite transistor may be decreased by choosing the product a1a2

lower than unity.

4. First design: differential folded cascode amplifier with fixedgain

4.1. Fixed-gain amplifier concept

One way to remove the KPN/KPP factor from Eq. (6) is to make it

equal to unity, which can be performed by using driving and load

transistors both of the same channel type. This can be achieved in a

simple way by using a differential folded cascode structure [3]. As

shown in Fig. 2, the amplifier consists of input differential pair

transistors TD, the cascode transistors TC, the low-g 0m composite

load (T1–T5) and the bias current sources IB and IM. The differential-input pair acts as a voltage controlled current source delivering

the output current IL proportional to VIN = VIN+ VIN. The load current IL can be written as:

VDD

IB

3.2. New approach: low-gm composite MOS load transistor

T1

vIn+

The key idea of the design is to increase the fixed voltage gain

by a composite load transistor (Fig. 1) exhibiting a low equivalent

transconductance g 0m . This realization is, in fact, equivalent to a Pchannel type diode-connected MOS transistor with very low value

of W/L. The circuit is based on the current scaling technique using

two current mirrors connected in the local feedback loop [3,5,6].

The equivalent transconductance g 0m can be determined from

the ID/VOUT relationship. The drain current of T2 (gm2 VGS2) is decreased by means of two current mirrors T3–T4 and T5–T1, with

scaling factors a1 and a2, respectively:

ð9Þ

vInTD

ID

IM

T2

V OUT

TD

TC

V BIAS

T5

TC

V BIAS

IL

IM

T3

T4

VSS

Fig. 2. Differential folded cascode amplifier with fixed-gain using the low-transconductance composite transistor (T1–T5).

617

V. Michal et al. / Cryogenics 49 (2009) 615–619

IL ¼ IM ID ;

ð10Þ

which becomes IL = IM IB/2 for VIN = 0.

By large-signal analysis, it can be deduced that:

1

8

ID ¼

qffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi

pffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi 2

4I0 bD V 2IN þ bD V IN :

ð11Þ

For a1 = a2 a and according to (1), the DC operating point of VOUT

is given by:

V OUT

sffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi

2

L2

I :

a K PðT2Þ W 2 L

1

¼ V DD V THðT2Þ ð12Þ

Measured parameter

Amplifier Section 4

Amplifier Section 5

Supply DC voltage

Quiescent current Iq

3 dB Bandwidth

Input noise @ 290 K

Input noise @ 77 K

Gain @ 290 K

D(Gain) 270–390 K

Gain error @ 77 K

THDc @ VOUT = 0.3 VPP

4.1–5.5 V

2.1 mA

10 MHz (GBWa = 1 GHz)

5 nV/Hz½

2 nV/Hz½

39.85 dB

0.12 dB

1.2 dB

1%

3.6–5.5 V

1.3 mA

4 MHz @ 5 Vb

5 nV/Hz½

3 nV/Hz½

39.3 dB @ 5 Vb

0.5 dB @ 4 Vb

1.3 dB @ 4 Vb

0.03%

a

b

The AC voltage gain GV1 can be calculated as:

GV1

Table 2

Measured parameters for both integrated amplifiers (0.35 lm CMOS).

c

dV OUT dV OUT dIL

¼

¼

:

dV IN

dIL dV IN

Gain-bandwidth product.

Supply DC voltage.

Total harmonic distortion.

ð13Þ

By plotting ID vs. VIN (Fig. 3), a nearly perfect straight line is obtained for small values of VIN in spite of the complicated expression

(11). As dIL/dVIN exhibits an almost constant value in the considered

input voltage range, the curvature of the amplifier DC characteristic

is therefore mainly due to dVOUT/dIL, which is inversely proportional

to the square root of IL according to (12), as also shown in Fig. 3.

Thus the voltage gain can be written as:

sffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi sffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi

1

W D =LD

IB

:

GV1 ðV IN Þ ¼

2a

W 2 =L2

2IL ðV IN Þ

ð14Þ

We observe that for an operating point fixed by VIN, the AC voltage

gain is only fixed by the accurate transistor dimension ratios and

depends no longer on KPN/KPP as in (6). The DC characteristic is inversely proportional to the square root of IL, which is fully acceptable for small-signal operation.

4.2. Fixed-gain amplifier characterization

The integrated version of Fig. 2 amplifier has been realized in a

regular 0.35 lm CMOS technology. The measured frequency response is flat with 40 dB gain achieving 10 MHz (290 K) and

17 MHz (77 K) bandwidth (3 dB) and bias current 2.1 mA

(Fig. 4, Table 2).

5. Second design: differential folded-cascode amplifier with

low-transconductance linear CMOS load

dI D

≈ const .

dVIN

400

2

40dB

1

375

VOUT= f (VIN)

(Measured )

0

350

-20

-10

0

10

DC output voltage (V)

Drain current I D (µA)

5.1. Linearized fixed-gain amplifier

The design of the second amplifier ensures wide temperature

operation with DC characteristic linear in a large dynamic range.

This latter feature is obtained by making dVOUT/dIL independent

of IL (i.e VOUT proportional to IL – see Fig. 3, dID/dVIN being constant

as already mentioned). Such a linear VOUT/IL characteristic can be

realized by using two diode-connected mutually biased transistors

T1 and T2 (Fig. 5). Fig. 5 shows also an auxiliary current source IAUX,

the value of which is chosen so that I0 = 0 when VIN = 0. The expression of I0 is given by:

I0 ¼ ðIM ID Þ IAUX :

20

DC input voltage (mV)

Fig. 3. ID vs. VIN quasi-linear characteristic computed from (11), for W = 2360 lm,

L = 2 lm, IB = 750 lA and IM = 400 lA; measured DC VOUT vs. VIN characteristic

compared to 40 dB voltage gain at VIN = 0 V (dashed line).

ð15Þ

We can now determine the I–V characteristic of the composite load

in Fig. 5 by solving the nodal equation:

b1

b

ðV DD V OUT jV TH1 jÞ2 ¼ 2 ðV OUT V TH2 Þ2 þ I0 :

2

2

ð16Þ

100

40

VDD

Voltage gain (dB)

77K

-60dB/

dec

20

50

20

10

290K

5.0

0

77K

-20

100

10

4

10

6

10

8

Input noise level (nV/Hz ½ )

-3dB

1.0

Frequency (Hz)

Fig. 4. Measured AC voltage gain and input noise at 290 K and 77 K for Fig. 2 fixedgain amplifier.

IB

I AUX

T

P-type

Low g m

composite

transistor

(Fig. 1)

1

In-

In+

TD

I0

TD

I1

I

2

ID

V BIAS

V BIAS

IL

IM

IM

IAUX =IM -

IB

2

T2

V OUT

Low g m

composite

transistor

(Fig. 1)

N-type

Linear low g

m

CMOS load

Fig. 5. Principle of the linearized temperature-compensated differential folded

cascode amplifier.

V. Michal et al. / Cryogenics 49 (2009) 615–619

The complicated expression of output voltage resulting from (16)

can be simplified by assuming identical transistor parameters

(b1 = b2 b, |VTH1| = VTH2 VTH) so that:

V OUT

V DD

I0

¼

;

2

b ðV DD 2V TH Þ

ð17Þ

showing the VOUT vs. I0 linear dependence, as well as VOUT DC operating point being VDD/2 for VIN = 0. To fulfil conditions b1 = b2 and

|VTH1| = VTH2 exactly, both T1 and T2 must have the same channel

(e.g. P) polarity (e.g. T2 must be inverted). Such an inversion can

be performed by a transformation circuit containing one voltage inverter and one current mirror. Fig. 6 shows the implementation of

this inversion provided by TM1, TM2, TI1 and TI2. To reach accurate

matching of both low gm composite transistors (T1–T5 and

T 01 T 05 ), the current mirror is realized with two identical N transistors TM1 and TM2 and the voltage inverter with two identical P transistors TI1 and TI2. To cancel the bulk effect, the substrate of TI2 must

be connected to its source, thus providing an accurate and constant

gain (1) in the whole dynamic range. The large signal voltage gain

can be determined by derivation of (16), (17), and (11):

GV2

1

¼

2a

sffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi 1

W D pffiffiffiffiffiffiffiffi W 2

K PP

IB ðV DD 2jV THP jÞ

:

LD

L2

ð18Þ

We can see that the voltage gain depends on the bias current IB

and power supply voltage VDD, as well as the transistor width to

length ratios, threshold voltage VTHP and gain factor KPP. It depends

no longer on voltage VIN.

The experimental response (Fig. 7) shows a very good agreement with simulated characteristics. This is due to (18), where

the sensitivity function SGIB ;K PP is naturally low. Hence, to achieve

high voltage gain accuracy, some care through design should be taken, simply by using long channel transistors (>2 lm).

50

Voltage gain (dB)

618

40

30

4.0V

4.4V

5.0V

20

10

0

~0

100

200

300

400

Temperature (K)

Fig. 8. For the second amplifier design (Figs. 5 and 6) and various VDD voltage

values, measured voltage gain as a function of temperature.

5.2. Temperature dependence of the voltage gain

To analyze the temperature dependence of the voltage gain, Eq.

(18) can be rewritten as:

C

;

GV2 ðTÞ ¼ pffiffiffiffiffiffiffiffiffiffiffiffiffiffi

K PP ðTÞ ðV DD 2 jV TH ðTÞjÞ

ð19Þ

where C is a constant term representing the temperature independent parameters: transistor dimensions (W/L ratios) and bias current IB. From (2) and (3), which give the temperature dependence

of KPP and VTH, (19) can be rewritten to explicit this dependence as:

C

:

GV2 ðTÞ ¼ rffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi

x

T

½V DD 2 jV TH ðT 0 Þj ð1 þ aTH ðT T 0 ÞÞ

K PP ðT 0 Þ T 0

ð20Þ

VDD

T1

T’1

T5

T’5

TI1

T2

I0

P

V OUT

T’2

TI2

T3

T4

TM1

P

TM2

T’3

T’4

V SS

Fig. 6. Linear symmetrical CMOS load following the differential folded cascode.

50

dV out

dV in

1

dB

(measured)

40

0

30

Measured

-1

Voltage gain (dB)

DC Output voltage (V)

2

20

6. Conclusion

Simulated

-2

-30

The parameters from Table 1 have been used to determine the

circuit behaviour in the whole 77–300 K temperature range. The

fact that (20) depends on VDD provides an interesting way to control

and balance the thermal GV2(T) characteristic. Indeed, computed

gain from (20) exhibits a better flatness in the 270–380 K range

for VDD = 5 V than for VDD = 4 V. However, the global performances

of the circuit in the 77–380 K temperature range are better at

VDD = 4 V (1.3 dB gain error at 77 K) than at VDD = 5 V (2.5 dB gain

error at 77 K). The voltage gain has been measured in the 4.2–

390 K temperature range (Fig. 8), exhibiting good agreement with

(20), namely around 300 K and 77 K where the parameters x and

aTH were experimentally determined (Section 2). Around 100 K,

however, some deviation from (20) could be noticed that can be

attributed to simplification in (5), where x and aTH have been considered as constant through the whole temperature range [4].

The achieved performances (Table 2) of both amplifiers can be

favourably compared with room temperature operational or

instrumentation amplifiers [7]. For instance, our feedback-free

40 dB voltage gain CMOS amplifier with 10 MHz bandwidth (Section 4) is realized with very low quiescent current. The high

impedance output nodes have to be buffered by an appropriate

voltage follower respecting the required properties of amplifiers

(e.g. linearity for amplifier in Section 5).

-20

-10

0

10

20

30

10

DC input voltage (mV)

Fig. 7. Measured and simulated DC VOUT/VIN transfer characteristic and voltage gain

of Fig. 5 amplifier with Fig. 6 linear load, for VDD = 5 V, T = 290 K and Iq = 1.3 mA.

In this paper, we proposed two original designs for high fixed

voltage gain CMOS amplifiers allowing the room temperature

and cryogenic operations. Both designs are based on a low-transconductance composite transistor as amplifier loads and contains

no passive elements (resistors, capacitors) in the structure.

V. Michal et al. / Cryogenics 49 (2009) 615–619

Experimental results for 0.35 lm CMOS ASICs exhibit very good

features that can present an interest for potential scientific using,

as well as for a large production. The relatively small final die size

(150 200 lm), with rather small consumption, makes it interesting as versatile analog block in VLSI design or as discrete integrated

circuit. Our targeted application of the amplifiers concerns the

readout circuitry associated with high-Tc superconducting [8]

and room temperature [9] bolometric detectors.

Acknowledgements

This research project has been supported by a Marie Curie Early

Stage Research Training Fellowship of the European Community’s

Sixth Framework Programme under Contract No. MEST-CT-2005020692.

References

[1] See for instance Calleja H. An approach to amplifier frequency compensation.

IEEE Trans Educat 2003;46(1):43–9.

619

[2] Comer DT. A wideband integrated circuit amplifier for fixed-gain application.

Analog Integrat Circ Signal Process 1996;11(3):243–51.

[3] Baker RJ, Harry LW, Boyce DE. CMOS circuit design, layout and simulation. IEEE

press series on microelectronic systems. Wiley-Interscience; 1998 [ISBN 07803-3416-7].

[4] Selberherr S, Langer E. Low temperature MOS device modeling. In: Proceedings

of the IEEE workshop on low temperature semiconductor electronics, August

1989. p. 68–72.

[5] Peterson KD, Geiger RL. Area/bandwidth tradeoffs for CMOS current mirrors.

IEEE Trans Circ Syst 1986;CAS-33(6):667–9.

[6] Kinget P, Steyart M, Van der Spiegel J. Full analog CMOS integration of very large

time constants for synaptic transfer in neural networks. Analog Integrat Circ

Signal Process 1992;2(4):281–95.

[7] See for instance: Analog devices website, section ‘‘differential and

instrumentation amplifier”, www.analog.com. See also: Švindrych Z, Janů Z,

Soukup F, Tichý R. Cryogenics 2008;48:160–5.

[8] Kreisler AJ, Dégardin AF, Aurino M, Péroz Ch, Villégier JC, Beaudin G., et al. New

trend in terahertz detection: high Tc superconducting hot electron bolometer

technology may exhibit advantages vs. low Tc devices. In: Proceedings of the

IEEE international microwave symposium, June 2007. p. 345–8.

[9] Longhin M, Kreisler AJ, Dégardin AF. Semiconducting YBCO thin films for

uncooled terahertz imagers. Mater Sci Forum 2008;587–588:273–7.