ES330 Laboratory Experiment No. 2 NMOS Common

advertisement

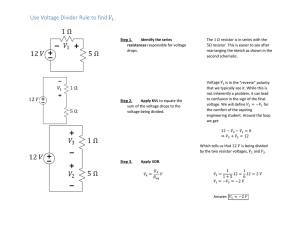

ES330 Laboratory Experiment No. 2 NMOS Common-Source Amplifier [Reference: Section 7.5.1 of Sedra/Smith (pages 467-469)] Objectives: 1. Design the amplifier for voltage gain AV to be at a minimum of -4 (V/V) and choose resistor values of RD and RS by calculation. 2. Measure the voltage gain of the amplifier to see how it compares with calculated voltage gain. Display waveforms on an oscilloscope. 3. Measure the output resistance RO of the amplifier looking into the output port. Materials: 1. Breadboard 2. One NMOS transistor – ALD1106PBL 3. Three large 47 microfarad capacitors 4. Several resistors of various values (two resistors are 10 k in value) 5. Jumper wires for use on breadboard 6. Function generator, digital multimeter and oscilloscope Circuit Schematic: 1 Circuit Parameters: The parameters of the circuit are listed in the table below. Component Value CC1, CC2 and CE 47 F each NMOS ALD1106PBL V+ = (-V_) 8 volts (nominal) Resistors RG and RL 10 k each Not specified in the table are values for the source resistor RS and drain resistor RD. These you will determine using design goals, namely, the drain current and the voltage gain of the amplifier. The minimum voltage gain AV of the amplifier is to be at least -4 (V/V) – the minus sign indicates that a common-source MOSFET amplifier is inverting (i.e., introduces a 180 degree phase shift). Furthermore, we want the DC drain current ID to equal 2 milliampere (1 mA). The design goals are AV -4 (V/V) and ID = 2 mA Transistor Parameters: Caution: MOSFET devices are ESD sensitive (electrostatic sensitive) and can easily be destroyed by handling – be sure to discharge or ground yourself before handling these sensitive devices. The gate electrode is the most sensitive. Note also that the maximum voltage that can be applied to VDS and VGS is +10.6 volts – exceeding this voltage can burn out the NMOS transistor. Our designated voltage supply voltages settings are 8 volts. Nominal parameters for the ALD1106PBL NMOS transistor can either be measured (using the transistor you select with the method suggested in appendix II), or roughly estimated from the ALD1106 Data Sheet. The Data Sheet is reproduced in the Appendix I. The threshold voltage Vt of the ALD1106 is listed as being typically 0.7 volt in the Data Sheet (Note: This is a coincidence with the VBE assumption used with a silicon bipolar transistor). In general, data from a Data Sheet should generally use nominal values rather than the minimum or maximum values. For output resistance ro to be used in a small-signal model assume that it is about 40 k (we have no better value to work with). Determining RS and RD: The value of ID is set by choosing RS at ID = 2 mA. NMOS transconductance gm is gm 2I D . VGS Vt 2 The gate node is essentially at ground potential (i.e., 0 volts) because gate current IG is for all practical purposes is zero. The AC voltage gain AV is then given by AV gm RD ro RL The value of resistor RD gives you control the voltage gain because it is in parallel with ro and RL. The other constraint on resistor RD is that the drain-source voltage must be large enough to keep the transistor in the saturated region of operation and also allow for an adequate voltage swing along the load line. In other words, be sure to watch the Q-point location in setting the bias point (ID, VDS) the transistor. Note: There are two load lines in this amplifier because of the coupling capacitor CC2 – the DC load line which excludes RL and the AC load line where the effective load resistance is RD, ro and RL all in parallel. DC Operating Point Analysis: First, sketch a DC schematic circuit. The three large capacitors are all open circuits for DC analysis purposes. Also, the signal generator assumes no role in the DC analysis. Begin by determining the values of IG, IS and ID using the IS = ID = 2 mA. Supply V_ = - 8 volts. A. What is the gate current? IG = _____ mA B. Determine the value of the overvoltage VOV and RS which establish ID = 2 mA (approximately). Remember that VGS = VOV + Vt by definition. Some assumptions may be necessary. Gate-source voltage VGS = ______ volts; C. Estimate the transconductance gm. Overvoltage VOV = ______ volts; gm = ______ mmhos (or milli-siemens or mA/V) D. Now we can estimate the value of the source resistor RS. RS = ______ ohms AC Analysis: Next we want to determine VDS and RD. Sketch the AC small-signal circuit. The largevalued capacitors now become short circuits (i.e., the capacitors will have negligible impedance at higher frequencies). Also, the power supply connections are assumed to be AC grounds. A. What happens to the source resistor RS in the AC analysis? B. Let vi be the small-signal voltage at the gate node of the transistor and vsig is the small-signal voltage of the signal generator. You should recognize that the signal generator is shown in its 3 Thévenin equivalent circuit. Be sure to check to see what the resistance Rsig is for the signal generator (or function generator). Estimate of vi/vsig = ______ (Is it unity? If yes, why is it unity?) C. Derive an expression for voltage gain AV = vo/vi, where vo is the output voltage as defined in the schematic circuit on page 1. Find a value for resistor RD giving a voltage gain greater than AV = -4 (V/V). Be sure that this value of RD also gives an acceptable value for VDS allowing for a reasonable AC voltage swing range at the output. What value of VDS do you calculate? VDS = _______ volts D. Now that you have a value of resistor RD, calculate the output resistance Ro at the output node as defined in the schematic circuit on page 1. Ro = _______ ohms Prototyping: You have reached the point where you will prototype the circuit with the resistor values you determined. It will look something like the photograph below. Be sure to ground pin 4 of the DIP package is grounded to avoid back-gate bias issues (remember we don’t want a floating substrate when using MOSFET devices). Be sure to keep lead lengths short to prevent oscillations. 4 Measurements: Make the following measurements: A. Using a digital multimeter, measure the DC voltages at the gate (VG), source (VS) and drain (VD) nodes of the transistor. B. Using a function generator set its sinusoidal “peak-to-peak” amplitude at 10 mVpk-pk with a frequency of 1,000 Hz (i.e., 1 kHz). This is the small-signal voltage vi. Now measure the amplifier’s output peak-to-peak voltage vO and this determines its midband voltage gain AV. C. Using an oscilloscope display the vO and vi waveforms versus time t. Are they sinusoidal in form? D. Measure the output resistance Ro. You can do this by replacing the 10 k RL load resistor with say a 1 Meg resistor and again measuring the voltage gain. This gives a maximum voltage gain value. By adjusting (i.e., lowering) the value of RL we can find a value of RL such that the voltage gain is one-half the value you found with the 1 Meg resistor. That particular value of RL is equal to the output resistance Ro. E. Increase the sinusoidal “peak-to-peak” amplitude of the function generator to a level where the output sinusoidal waveform shows a large amount of waveform distortion. Describe what you see with respect to the distorted waveform’s shape. Post-Measurement Exercise: A. Take your calculated values of VGS and VDS from your the DC bias and compare these values to those you measured. How do they compare with the calculated values? B. Compare the measured and the calculated voltage gain values. Explain the difference. C. Compare your measured and calculated output resistance values. APPENDIX I – ALD1106 Data Sheet 5 6 7 APPENDIX II – Measuring threshold voltage Vt of NMOS Transistor The configuration shown below is a simple circuit that can be used to measure the threshold voltage Vt and the value of VOV at ID = 2 mA. It requires a “current meter” (i.e., digital multimeter) in the drain branch and a variable voltage source to vary the applied gate-to-source voltage. The source node is grounded and serves as our voltage reference. Resistor RD is present for current limiting to protect the circuit (it could be a 1 k resistor, for example). Just be sure RD is not too large (Why?). Starting from VGS = 0, slowly increase VGS until a current ID just begins to flow (say, 10 microamperes). That yields Vt. Further slowly increase VGS until current ID equals 2 mA. This gives VOV at ID = 2 mA. Now you have two parameters useful for setting the NMOS transistor’s operating point. 8