If parameter is not given, you can model parameter to

advertisement

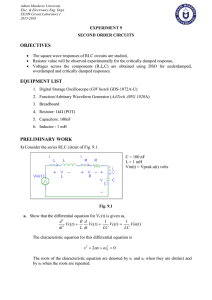

[If parameter is not given, you can model parameter to specific character (ex r01, gm1.)] 1. We wish to design the circuit of Fig. 1 for a drain current of 1mA. If W/L = 20/0.18, compute R1 and R2 such that the input impedance is at least 20kΩ. (𝛍𝛍𝐧𝐧 𝐂𝐂𝐨𝐨𝐨𝐨 = 𝟐𝟐𝟐𝟐𝟐𝟐𝟐𝟐𝟐𝟐/𝐕𝐕 𝟐𝟐 , 𝛌𝛌 = 𝟎𝟎, 𝐕𝐕𝐭𝐭 = 𝟎𝟎. 𝟒𝟒𝟒𝟒) VDD=1.8 V 500Ω R1 M1 R2 <Figure 1> 2. Assuming the MOSFET is in saturation, calculate the Rout and Rin of the circuit below. (𝛌𝛌 ≠ 𝟎𝟎) VDD RL Rout Vb M1 Rin RS <Figure 2> 3. Assuming the MOSFET is in saturation, calculate the small-signal voltage gain of the circuit. (𝛌𝛌 ≠ 𝟎𝟎) VDD RD RS Vout Vin M1 <Figure 3> 4. The NMOS transistor in the CS amplifier shown in Figure 4 has Vt=0.7V, VA=50V. (a) Neglecting the Early effect, verify that the MOSFET is operating in saturation with 𝑾𝑾 ID=0.5mA, VOV=VGS-Vt=0.3V. What must the MOSFET’s kn (=𝛍𝛍𝐧𝐧 𝐂𝐂𝐨𝐨𝐨𝐨 ) be? What is the dc 𝑳𝑳 voltage at the drain? (b) Find Rin and Gain. (c) If vsig is a sinusoid with a peak amplitude vpeak, find the maximum allowable value of vpeak for which the transistor remains in saturation. What is the corresponding amplitude of the output voltage? (d) What is the value of resistance RS that needs to be inserted in series with capacitor CS in order to allow us to double the input signal vpeak? What output voltage now results? 5V 300kΩ 5kΩ Vo CC2 120kΩ CC1 Vsig M3 200kΩ Rin <Figure 4> CS 2kΩ 5kΩ 5. The PMOS transistor in the CS amplifier of Figure 5 has Vt=-0.7V, VA=∞. (a) Select a value for RS to bias the transistor at ID = 0.3mA and |VOV|=|VGS-Vt|=0.3V. Assume vsig to have a zero dc component. (b) Select a value for RD that results in Av=-10 V/V. (c) If vsig is a sinusoid with a peak amplitude vpeak, find the largest vpeak that the amplifier can handle while remaining in the saturation region. What is the corresponding signal at the output? (d) If to obtain reasonably linear operation, vpeak is limited to 50mV, what value can RD be increased to while maintaining saturation-region operation? What is the new value of Av? 2.5V RS CS Rsig Vsig M3 RD -2.5V <Figure 5> Vo CC