Freescale Semiconductor

Technical Data

Document Number: MCIMX27EC

Rev. 1.8, 1/2013

i.MX27 and i.MX27L

Package Information

Plastic Package

Case 1816-01

(MAPBGA–404)

Case 1931-04

(MAPBGA-473)

i.MX27 and i.MX27L

Data Sheet

Multimedia Applications

Processor

1

Introduction

The i.MX27 and i.MX27L (MCIMX27/MX27L)

multimedia applications processors represents the next

step in low-power, high-performance application

processors. Unless otherwise specified, the material in

this data sheet is applicable to both the i.MX27 and

i.MX27L processors and referred to singularly

throughout this document as i.MX27.

Ordering Information

See Table 1 on page 4 for ordering information.

1.

2.

3.

4.

The i.MX27L does not include the following features:

ATA-6 HDD Interface, Memory Stick Pro, VPU:

MPEG-4/ H.263/H.264 HW encoder/decoder, and

eMMA (PrP processing, CSC, deblock, dering).

Based on an ARM926EJ-S™ microprocessor core, the

i.MX27/27L processor provides the performance with

low power consumption required by modern digital

devices such as the following:

• Feature-rich cellular phones

• Portable media players and mobile gaming

machines

• Personal digital assistants (PDAs) and wireless

PDAs

© Freescale Semiconductor, Inc., 2008-2012. All rights reserved.

5.

6.

7.

Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1. Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.2. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.3. Ordering Information . . . . . . . . . . . . . . . . . . . . . . 4

Functional Description and Application Information . . . . 4

2.1. ARM926 Microprocessor Core Platform . . . . . . . . 4

2.2. Module Inventory . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.3. Module Descriptions . . . . . . . . . . . . . . . . . . . . . . . 9

Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.1. Power-Up Sequence . . . . . . . . . . . . . . . . . . . . . . 35

3.2. EMI Pins Multiplexing . . . . . . . . . . . . . . . . . . . . . 35

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . 40

4.1. i.MX27/iMX27L Chip-Level Conditions . . . . . . . . 40

4.2. Module-Level Electrical Specifications . . . . . . . . 43

4.3. Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . 54

Package Information and Pinout . . . . . . . . . . . . . . . . 109

5.1. Full Package Outline Drawing (17 mm × 17 mm) 109

5.2. Pin Assignments (17 mm × 17 mm) . . . . . . . . . 110

5.3. Full Package Outline Drawing (19 mm × 19 mm) 129

5.4. Pin Assignments (19 mm × 19 mm) . . . . . . . . . 130

Product Documentation . . . . . . . . . . . . . . . . . . . . . . . 150

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Introduction

•

•

Portable DVD players

Digital cameras

The i.MX27/MX27L processor features the advanced and power-efficient ARM926EJ-S core operating at

speeds up to 400 MHz, and is optimized for minimal power consumption using the most advanced

techniques for power saving (for example, DPTC, power gating, and clock gating). With 90 nm technology

and dual Vt, the i.MX27/MX27L device provides the optimal performance vs. leakage current balance.

The performance of the i.MX27/MX27L processors are both boosted by an on-chip cache system, and

features peripheral devices, such as an MPEG-4, H.263, an H.264 video codec (up to D1—720 x 486—@

30 FPS), LCD, eMMA_lt, and CMOS Sensor Interface controllers.

The i.MX27/MX27L processors supports connections to various types of external memories, such as

266-MHz DDR, NAND Flash, NOR Flash, SDRAM, and SRAM. The i.MX27/MX27L devices can be

connected to a variety of external devices using technology, such as high-speed USBOTG 2.0, the

Advanced Technology Attachment (ATA), Multimedia/Secure Data (MMC/SDIO), and CompactFlash.

NOTE

The i.MX27L does not support the ATA-6 HDD interface.

1.1

Features

The MX27/MX27L processors are targeted for video and voice over-IP (V2IP) and smart remote

controllers. It also provides low-power solutions for any high-performance and demanding multimedia

and graphics applications.

The systems include the following features:

• Multi-standard video codec (i.MX27 only)

— MPEG-4 part-II simple profile encoding/decoding

— H.264/AVC baseline profile encoding/decoding

— H.263 P3 encoding/decoding

— Multi-party call: one stream encoding and two streams decoding simultaneously

— Multi-format: encodes MPEG-4 bitstream, and decodes H.264 bitstream simultaneously

— On-the-fly video processing that reduces system memory load (for example, the

power-efficient viewfinder application with no involvement of either the memory system or the

ARM CPU)

• Advanced power management (i.MX27/27L)

— Dynamic process and temperature compensation

— Multiple clock and power domains

— Independent gating of power domains

• Multiple communication and expansion ports

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

2

Freescale Semiconductor

Introduction

1.2

Block Diagram

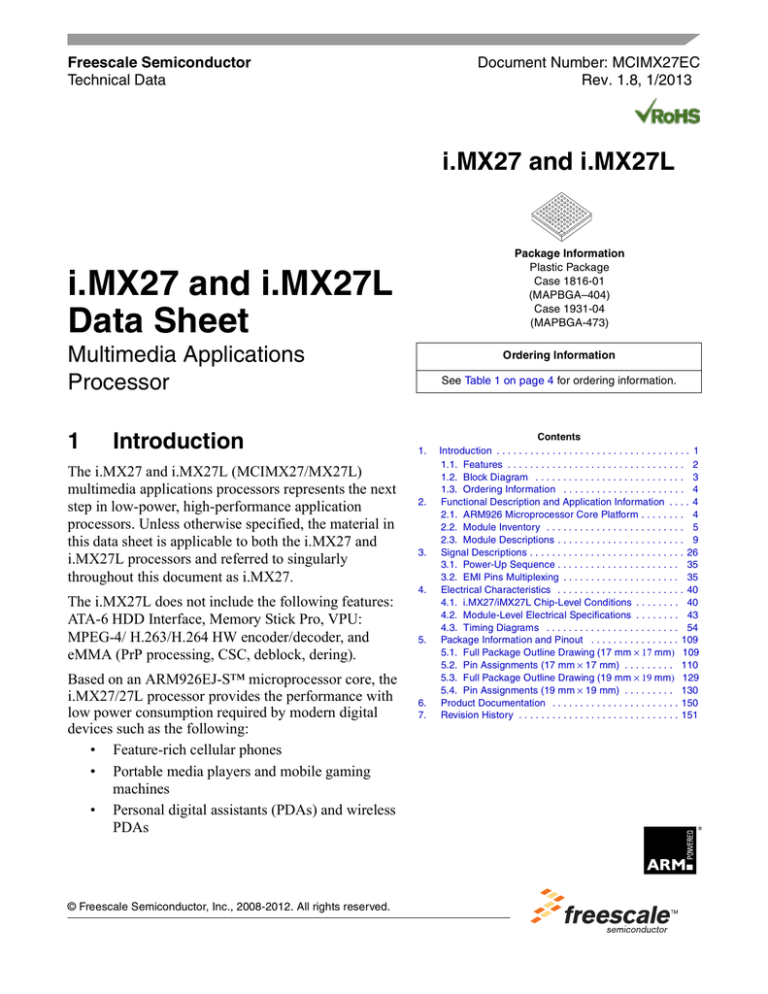

Figure 1 shows the i.MX27 simplified interface block diagram.

DDR/

SDRAM

NOR/NAND

Flash

LCD Display

LCDC

SLCDC

M3IF

SDRAMC

NFC

WEIM

PCMCIA/CF

iROM

10/100

ETH XVR

Security

AP Peripherals

AUDMUX

CSI

SSI (2)

CSPI (3)

AHB Switch Fabric

VRAM

Camera

ARM926

Platform

I2C (2)

UART (6)

ARM926EJ-S

L1 I/D cache

USBOTG HS

1-Wire

AITC

FEC

ETM9

ATA

SDHC (3)

eMMA-lt

MSHC

GPIO

JTAG

Audio/Power

Management

SAHARA2

RTIC

SCC

Video Codec

CRM

PWM

DMA

KPP

IIM

Application Processor Domain (AP)

JTAG

Timers

WDOG

GPT (6)

RTC

IrDA

XVR

Bluetooth

WLAN

USBOTG

XVR

MMC/SDIO

Keypad

Access

Conn.

Note: The i.MX27L does not support the following:

• ATA-6 HDD Interface

• Memory Stick Pro

• VPU: MPEG-4/.263/H.264 HW encoder/decoder

• eMMA (PrP processing, CSC, deblock, dering)

Figure 1. i.MX27/MX27L Simplified Interface Block Diagram

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

3

Functional Description and Application Information

1.3

Ordering Information

Table 1 provides ordering information for the MAPBGA, lead-free packages.

Table 1. Ordering Information

2

2.1

Device

Temperature

Package

MCIMX27VOP4A

–20° C to +85° C

1816-01

MCIMX27LVOP4A

–20° C to +85° C

1816-01

MCIMX27MOP4A

–40° C to +85° C

1931-04

MCIMX27LMOP4A

–40° C to +85° C

1931-04

MCIMX27VJP4A

–20° C to +85° C

1816-01

MCIMX27LVJP4A

–20° C to +85° C

1816-01

MCIMX27MJP4A

–40° C to +85° C

1931-04

MCIMX27LMJP4A

–40° C to +85° C

1931-04

Functional Description and Application Information

ARM926 Microprocessor Core Platform

The ARM926 Platform consists of the ARM926EJ-S processor, ETM9, ETB9, a 6 × 3 Multi-Layer AHB

crossbar switch (MAX), and a “primary AHB” complex.

• The instruction bus (I-AHB) of the ARM926EJ-S processor is connected directly to MAX Master

Port 0.

• The data bus (D-AHB) of the ARM926EJ-S processor is connected directly to MAX Master Port 1.

Four alternate bus master interfaces are connected to MAX Master Ports 2–5. Three slave ports of the

MAX are AHB-Lite compliant buses. Slave Port 0 is designated as the “primary” AHB. The primary AHB

is internal to the platform and has five slaves connected to it: the AITC interrupt module, the MCTL

memory controller, and two AIPI peripheral interface gaskets. Slave Ports 1 and 2 of the MAX are referred

to as “secondary” AHBs. Each of the secondary AHB interfaces is only accessible off platform.

The ARM926EJ-S processor supports the 32-bit and 16-bit ARM Thumb instruction sets, enabling the

user to trade off between high performance and high-code density. The ARM926EJ-S processor includes

features for efficient execution of Java byte codes, providing Java performance similar to the just-in-time

(JIT) compiler—which is a type of Java compiler—but without the associated code overhead.

The ARM926EJ-S processor supports the ARM debug architecture and includes logic to assist in both

hardware and software debugging. The ARM926EJ-S processor has a Harvard cached architecture and

provides a complete high-performance processor subsystem, including the following:

• An ARM9EJ-S integer core

• A Memory Management Unit (MMU)

• Separate instruction and data AMBA AHB bus interfaces

• ETM and JTAG-based debug support

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

4

Freescale Semiconductor

Functional Description and Application Information

The ARM926EJ-S processor provides support for external coprocessors enabling floating-point or other

application-specific hardware acceleration to be added. The ARM926EJ-S processor implements ARM

architecture version 5TEJ.

The four alternate bus master ports on the ARM926 Platform, which are connected directly to master ports

of the MAX, are designed to support connections to multiple AHB masters external to the platform. An

external arbitration AHB control module is needed if multiple external masters are desired to share an

ARM926 Platform alternate bus master port. However, the alternate bus master ports on the platform

support seamless connection to a single master with no external interface logic required.

A primary AHB MUX (PAHBMUX) module performs address decoding, read data muxing, bus

watchdog, and other miscellaneous functions for the primary AHB within the platform. A clock control

module (CLKCTL) is provided to support a power-conscious design methodology, as well as

implementation of several clock synchronization circuits.

2.1.1

Memory System

The ARM926EJ-S complex includes 16-Kbyte Instruction and 16-Kbyte Data caches. The embedded

45-Kbyte SRAM (VRAM) can be used to avoid external memory accesses or it can be used for

applications. There is also a 24-Kbyte ROM for bootstrap code.

2.2

Module Inventory

Table 2 shows an alphabetical listing of the modules in the i.MX27/MX27L multimedia applications

processors. A cross-reference to each module’s section and page number goes directly to a more detailed

module description for additional information.

Table 2. Digital and Analog Modules

Functional

Grouping

Brief Description

Section/

Page

Block Mnemonic

Block Name

1-Wire®

1-Wire Interface

Connectivity

Peripheral

The 1-Wire module provides bi-directional communication

between the ARM926EJ-S and the Add-Only-Memory EPROM

(DS2502). The 1-Kbit EPROM is used to hold information

about battery and communicates with the ARM926 Platform

using the IP interface.

2.3.1/9

AIPI

AHB-Lite IP

Interface

Module

Bus Control

The AIPI acts as an interface between the ARM Advanced

High-performance Bus Lite. (AHB-Lite) and lower bandwidth

peripherals that conforms to the IP Bus specification, Rev 2.0.

2.3.2/10

AITC

ARM9EJ-S

Interrupt

Controller

Bus Control

AITC is connected to the primary AHB as a slave device. It

generates the normal and fast interrupts to the ARM926EJ-S

processor.

2.3.3/10

ARM926EJS

ARM926EJ-S

CPU

The ARM926EJ-S (ARM926) is a member of the ARM9 family

of general-purpose microprocessors targeted at multi-tasking

applications.

2.3.4/10

ATA

Advanced

Technology(AT)

Attachment

Connectivity

Peripheral

The ATA block is an AT attachment host interface. It interfaces

with IDE hard disc drives and ATAPI optical disc drives.

2.3.5/11

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

5

Functional Description and Application Information

Table 2. Digital and Analog Modules (continued)

Section/

Page

Block Mnemonic

Block Name

Functional

Grouping

AUDMUX

Digital Audio

Multiplexer

Multimedia

Peripheral

CRM

Clock and

Reset Module

CSI

CMOS Sensor

Interface

Multimedia

Interface

The CSI is a logic interface which enables the i.MX27/MX27L

processors to connect directly to external CMOS sensors and

a CCIR656 video source.

2.3.8/12

CSPI

Configurable

Serial Peripheral

Interface (x3)

Connectivity

Peripheral

The i.MX27/MX27L processors have three CSPI modules.

CSPI is equipped with two data FIFOs and is a master/slave

configurable serial peripheral interface module, allowing the

i.MX27/MX27L processors to interface with both external SPI

master and slave devices.

2.3.9/13

DMAC

Direct Memory

Access

Controller

Standard

System

Resource

eMMA_lt

eMMA_lt

H/W

Accelerator

Functions

EMI

External

Memory

Interface

ESDRAMC

Enhanced

SDRAM

Controller

External

Memory

Interface

FEC

Fast Ethernet

Controller

Connectivity

Peripheral

The FEC performs the full set of IEEE 802.3/Ethernet

CSMA/CD media access control and channel interface

functions. The FEC supports connection and functionality for

the 10/100 Mbps 802.3 media independent interface (MII). It

requires an external transceiver (PHY) to complete the

interface to the media.

2.3.13/15

GPIO

General

Purpose I/O

Module

Pins

The GPIO provides 32 bits of bidirectional, general purpose

I/O. This peripheral provides dedicated general-purpose pins

that can be configured as either inputs or outputs.

2.3.14/16

GPT

General

Purpose Timer

Timer

Peripheral

The GPT is a multipurpose module used to measure intervals 2.3.15/16

or generate periodic output.

I2C

Inter IC

Communication

Connectivity

Peripheral

The I2C provides serial interface to control the sensor interface 2.3.16/17

and other external devices. Data rates of up to 100 Kbits/s are

supported.

Brief Description

The AUDMUX interconnections allow multiple, simultaneous

audio/voice/data flows between the ports in point-to-point or

point-to-multipoint configurations.

Clock and

The CRM generates clock and reset signals used throughout

Reset Control the i.MX27/MX27L processors and also for external

peripherals.

2.3.6/11

2.3.7/12

2.3.10/13

The DMAC of the i.MX27/MX27L processors provides 16

channels supporting linear memory, 2D memory, FIFO and

end-of-burst enable FIFO transfers to support a wide variety of

DMA operations.

eMMA_lt consists of a PreProcessor and PostProcessor, and

provides video acceleration. The PrP and PP can be used for

generic video pre and post processing such as scaling,

resizing, and color space conversions.

Memory

The EMI includes

Interface (EMI) • Multi-Master Memory Interface (M3IF)

• Enhanced SDRAM/MDDR memory controller (ESDRAMC)

• PCMCIA memory controller (PCMCIA)

• NAND Flash Controller (NFC)

• Wireless External Interface Module (WEIM)

2.3.11/13

—

The ESDRAMC provides interface and control for synchronous 2.3.12/15

DRAM memories for the system.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

6

Freescale Semiconductor

Functional Description and Application Information

Table 2. Digital and Analog Modules (continued)

Functional

Grouping

Block Mnemonic

Block Name

IIM

IC Identification

Module

Security

JTAGC

JTAG Controller

Debug

KPP

Keypad Port

LCDC

Brief Description

Section/

Page

The IIM provides an interface for reading—and in some cases, 2.3.17/17

programming, and overriding identification and control

information stored in on-chip fuse elements.

Contact your Freescale Semiconductor sales office or

distributor for additional information on SCC, RTIC, IIM,

SAHARA2

The JTAGC provides debug access to the ARM926 core,

built-in self-test (BIST), and boundary scan test control.

2.3.18/17

Connectivity

Peripheral

The KPP is used for key pad matrix scanning or as a general

purpose I/O. This peripheral simplifies the software task of

scanning a keypad matrix.

2.3.19/17

Liquid Crystal

Display

Controller

Multimedia

Interface

The LCDC provides display data for external gray-scale or

color LCD panels.

2.3.20/17

M3IF

Multi-Master

Memory

Interface

External

Memory

Interface

The M3IF controls memory accesses from one or more

masters through different port interfaces to different external

memory controllers ESDCTL/MDDRC, PCMCIA, NFC, and

WEIM.

2.3.21/18

MAX

Multi-layer AHB

Crossbar Switch

Bus Control

The ARM926EJ-S processor’s instruction and data buses and 2.3.22/18

all alternate bus master interfaces arbitrate for resources via a

6 × 3 MAX. There are six fully functional master ports (M0–M5)

and three fully functional slave ports (S0–S2). The MAX is

uni-directional. All master and slave ports are AHB-Lite

compliant.

MSHC

Memory Stick

Host Controller

Connectivity

Peripheral

The MSHC is placed in between the AIPI and the customer

memory stick to support data transfer from the i.MX27 device

to the customer memory stick.

Note: The i.MX27L does not support the MSHC feature

2.3.23/19

NFC

NAND Flash

Controller

External

Memory

Interface

The NFC is a submodule of EMI. The NFC implements the

interface to standard NAND Flash memory devices.

2.3.24/19

PCMCIA

Personal

Computer

Memory Card

International

Association

External

Memory

Interface

The PCMCIA host adapter module provides the control logic

for PCMCIA socket interfaces, and requires some additional

external analog power switching logic and buffering.

2.3.25/20

PLL

Phase Lock

Loop

PWM

Pulse-Width

Modulator

Clock and

The two DPLLs provide clock generation in digital and mixed

Reset Control analog/digital chips designed for wireless communication and

other applications.

Timer

Peripheral

The PWM has a 16-bit counter and is optimized to generate

sound from stored sample audio images. It can also generate

tones.

2.3.26/20

2.3.27/20

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

7

Functional Description and Application Information

Table 2. Digital and Analog Modules (continued)

Functional

Grouping

Section/

Page

Brief Description

Block Mnemonic

Block Name

RTC

Real Time Clock

Timer

Peripheral

RTIC

Run-Time

Integrity

Checkers

Security

The RTIC ensures the integrity of the contents of the peripheral 2.3.29/21

memory and assists with boot authentication.

Contact your Freescale Semiconductor sales office or

distributor for additional information on SCC, RTIC, IIM,

SAHARA2

SAHARA2

Symmetric/

Asymmetric

Hashing and

Random

Accelerator

Security

SAHARA2 is a security co-processor which forms part of the 2.3.30/21

Platform Independent Security Architecture (PISA), and can be

used on cell phone baseband processors or wireless PDAs.

Contact your Freescale Semiconductor sales office or

distributor for additional information on SCC, RTIC, IIM,

SAHARA2

SCC

Security

Controller

Module

Security

The SCC is a hardware component composed of two

blocks—the Secure RAM module, and the Security Monitor.

The Secure RAM provides a way of securely storing sensitive

information. The Security Monitor implements the security

policy, checking algorithm sequencing, and controlling the

Secure State.

Contact your Freescale Semiconductor sales office or

distributor for additional information on SCC, RTIC, IIM,

SAHARA2

SDHC

Secured Digital

Host Controller

Connectivity

Peripheral

The SDHC controls the MMC (MultiMediaCard), SD (Secure 2.3.32/21

Digital) memory, and I/O cards by sending commands to cards

and performing data accesses to and from the cards.

SLCDC

Smart Liquid

Crystal Display

Controller

Multimedia

Interface

The SLCDC module transfers data from the display memory

buffer to the external display device.

SSI

Synchronous

Serial Interface

Multimedia

Peripheral

The SSI is a full-duplex, serial port that allows the chip to

2.3.34/22

communicate with a variety of serial devices, such as standard

codecs, digital signal processors (DSPs), microprocessors,

peripherals, and popular industry audio codecs that implement

the inter-IC sound bus standard (I2S) and Intel AC97 standard.

UART

Universal

Asynchronous

Receiver/

Transmitter

Connectivity

Peripheral

2.3.35/23

The UART provides serial communication capability with

external devices through an RS-232 cable or through use of

external circuitry that converts infrared signals to electrical

signals (for reception) or transforms electrical signals to signals

that drive an infrared LED (for transmission) to provide low

speed IrDA compatibility.

The RTC module provides a current stamp of seconds,

minutes, hours, and days. Alarm and timer functions are also

available for programming. The RTC supports dates from the

year 1980 to 2050.

2.3.28/20

2.3.31/21

2.3.33/22

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

8

Freescale Semiconductor

Functional Description and Application Information

Table 2. Digital and Analog Modules (continued)

Functional

Grouping

Brief Description

Section/

Page

Block Mnemonic

Block Name

USB

Universal Serial

Bus–2 Host

Controllers and

1 OTG

(On-The-Go)

Connectivity

Peripherals

2.3.36/23

The i.MX27/MX27L processors provide two USB Host

controllers and one USBOTG of which:

• USB Host 1 is designed to support transceiverless

connection to the on-board peripherals in Low Speed and

Full Speed mode, and connection to the ULPI

(UTMI+Low-Pin Court) and Legacy Full Speed transceivers

• USB Host 2 is designed to support transceiverless

connection to the Cellular Modem Baseband Processor

• The USBOTG controller offers HS/FS/LS capabilities in Host

mode and HS/FS in device mode. In Host mode, the

controller supports direct connection of a FS/LS device

(without external hub). In device (bypass) mode, the OTG

port functions as gateway between the Host 1 Port and the

OTG transceiver.

Video Codec

Video Codec

Hardware

Acceleration

Video Codec module supports full duplex video codec with 25 2.3.39/25

fps VGA image resolution, integrates H.264 BP, MPEG-4 SP

and H.263 P3 video processing standard together.

WDOG

Watchdog Timer

Module

Timer

Peripheral

2.3.37/24

The WDOG module protects against system failures by

providing a method for the system to recover from unexpected

events or programming errors.

WEIM

Wireless

External

Interface

Module

External

Memory

Interface

The Wireless External Module (WEIM) handles the interface to 2.3.38/25

devices external to chip, including generation of chip selects,

clock and control for external peripherals and memory. It

provides asynchronous and synchronous access to devices

with SRAM-like interface.

2.3

Module Descriptions

This section provides a brief text description of all the modules included in the i.MX27/MX27L devices,

arranged in alphabetical order.

2.3.1

1-Wire Module

The 1-Wire module provides bi-directional communication between the ARM926 core and the Add-Only

Memory EPROM, DS2502. The 1-Kbit EPROM holds information about the battery and communicates

with the ARM926 Platform using the IP interface. Through the 1-Wire interface, the ARM926 acts as the

bus master while the DS2502 device is the slave. The 1-Wire peripheral does not trigger interrupts; hence

it is necessary for the ARM926 to poll the 1-Wire to manage the module. The 1-Wire uses an external pin

to connect to the DS2502. Timing requirements are met in hardware with the help of a 1 MHz clock. The

clock divider generates a 1 MHz clock that is used as a time reference by the state machine. Timing

requirements are crucial for proper operation, and the 1-Wire state machine and the internal clock provide

the necessary signal. The clock must be configured to approximately 1 MHz. You can then set the 1-Wire

register to send and receive bits over the 1-Wire bus.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

9

Functional Description and Application Information

2.3.2

AHB-Lite IP Interface Module (AIPI)

The AIPI acts as an interface between the ARM Advanced High-performance Bus Lite. (AHB-Lite) and

lower bandwidth peripherals conforming to the IP bus specification Rev 2.0. There are two AIPI modules

in i.MX27/MX27L processors.

The following list summarizes the key features of the AIPI:

• All peripheral read transactions require a minimum of two system clocks (R-AHB side) and all

write transactions require a minimum of three system clocks (R-AHB side).

• The AIPI supports 8-bit, 16-bit, and 32-bit IP bus peripherals. Byte, half word, and full word reads

and writes are supported.

• The AIPI supports multi-cycle accesses by providing 16-bit to 8-bit peripherals operations and

32-bit to both 16-bit and 8-bit peripherals operations.

• The AIPI supports 31 external IP bus peripherals each with a 4-Kbyte memory map (a slot).

2.3.3

ARM926EJ-S Interrupt Controller (AITC)

The ARM926EJ-S Interrupt Controller (AITC) is a 32-bit peripheral that collects interrupt requests from

up to 64 sources and provides an interface to the ARM926EJ-S core. The AITC includes software

controlled priority levels for normal interrupts.

The AITC performs the following functions:

• Supports up to 64 interrupt sources

• Supports fast and normal interrupts

• Selects normal or fast interrupt request for any interrupt source

• Indicates pending interrupt sources via a register for normal and fast interrupts

• Indicates highest priority interrupt number via register. (Can be used as a table index.)

• Independently can enable or disable any interrupt source

• Provides a mechanism for software to schedule an interrupt

• Supports up to 16 software controlled priority levels for normal interrupts and priority masking

• Can single-bit disable all normal interrupts and all fast interrupts. (Used in enabling of secure

operations.)

2.3.4

ARM926EJ-S Platform

The ARM926EJ-S (ARM926) is a member of the ARM9 family of general-purpose microprocessors

targeted at multi-tasking applications. The ARM926 supports the 32-bit ARM and 16-bit Thumb

instructions sets. The ARM926 includes features for efficient execution of Java byte codes. A JTAG port

is provided to support the ARM Debug Architecture, along with associated signals to support the ETM9

real-time trace module. The ARM926EJ-S is a Harvard cached architecture including an ARM9EJ-S

integer core, a Memory Management Unit (MMU), separate instruction and data AMBA AHB interfaces,

separate instruction and data caches, and separate instruction and data tightly coupled memory (TCM)

interfaces. The ARM926 co-processor, instruction TCM, and data TCM interfaces will be tied off within

the ARM926 Platform and will not be available for external connection.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

10

Freescale Semiconductor

Functional Description and Application Information

The ARM926EJ-S processor is a fully synthesizable macrocell, with a configurable memory system. Both

instruction and data caches will be 16 kbytes on the platform. The cache is virtually accessed and virtually

tagged. The data cached has physical tags as well. The MMU provides virtual memory facilities which are

required to support various platform operating systems such as Symbian OS, Windows CE, and Linux. The

MMU contains eight fully associative TLB entries for lockdown and 64 set associative entries. Refer to

the ARM926EJ-S Technical Reference Manual for more information.

2.3.5

Advanced Technology Attachment (ATA)

The Advanced Technology Attachment (ATA) host controller complies with the ATA/ATAPI-6

specification. The primary use of the ATA host controller is to interface with IDE hard disc drives and

Advanced Technology Attachment Packet Interface (ATAPI) optical disc drives. It interfaces with the ATA

device over a number of ATA signals.

This host controller supports interface protocols as specified in ATA/ATAPI-6 standard, as follows:

• PIO mode 0, 1, 2, 3, and 4

• Multiword DMA mode 0, 1, and 2

• Ultra DMA modes 0, 1, 2, 3, and 4 with bus clock of 50 MHz or higher

• Ultra DMA mode 5 with bus clock of 80 MHz or higher

Before accessing the ATA bus, the host must program the timing parameters to be used on the ATA bus.

The timing parameters control the timing on the ATA bus. Most timing parameters are programmable as a

number of clock cycles (1 to 255). Some are implied. All of the ATA device-internal registers are visible

to users, and they are defined as mirror registers in ATA host controller. As specified in ATA/ATAPI-6

standard, all the features/functions are implemented by reading/writing to the device’s internal registers.

There are basically two protocols that can be active at the same time on the ATA bus, as follows:

• The first and simplest protocol (PIO mode access) can be started at any time by the ARM926 to

the ATA bus. The PIO mode is a slow protocol, mainly intended to be used to program an ATA disc

drive, but also can be used to transfer data to/from the disc drive.

• The second protocol is the DMA mode access. DMA mode is started by the ATA interface after

receiving a DMA request from the drive, and only if the ATA interface has been programmed to

accept the DMA request. In DMA mode, either multiword-DMA or ultra-DMA protocol is used

on the ATA bus. All transfers between FIFO and the host IP or DMA IP bus are zero wait states

transfer, so a high-speed transfer between FIFO and DMA/host bus is possible.

2.3.6

Digital Audio MUX (AUDMUX)

The Digital Audio MUX (AUDMUX) provides programmable interconnecting for voice, audio, and

synchronous data routing between host serial interfaces—for example, SSI, SAP, and peripheral serial

interfaces—such as, audio and voice codecs. The AUDMUX allows audio system connectivity to be

modified through programming, as opposed to altering the design of the system into which the chip is

designed. The design of the AUDMUX allows multiple simultaneous audio/voice/data flows between the

ports in point-to-point or point-to-multipoint configurations.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

11

Functional Description and Application Information

Included in the AUDMUX are two types of interfaces. The internal ports connect to the processor serial

interfaces, and the external ports connect to off-chip audio devices and serial interfaces of other processors.

A desired connectivity is achieved by configuring the appropriate internal and external ports.

The module includes full 6-wire SSI interfaces for asynchronous receive and transmit, as well as a

configurable 4-wire (synchronous) or 6-wire (asynchronous) peripheral interface. The AUDMUX allows

each host interface to be connected to any other host or peripheral interface in a point-to-point or

point-to-multipoint (network mode).

2.3.7

Clock and Reset Module (CRM)

The Clock and Reset Module (CRM) generates clock and reset signals used throughout the

i.MX27/MX27L processor and for external peripherals. It also enables system software to control,

customize, or read the status of the following functions:

• Chip ID

• Multiplexing of I/O signals

• I/O Driving Strength

• I/O Pull Enable Control

• Well-Bias Control

• System boot mode selection

• DPTC Control

2.3.8

CMOS Sensor Interface (CSI)

The CMOS Sensor Interface (CSI) is a logic interface that enables the i.MX27/MX27L processors to

connect directly to external CMOS sensors and CCIR656 video source.

The capabilities of the CSI include the following:

• Configurable interface logic to support popular CMOS sensors in the market

• Support traditional sensor timing interface

• Support CCIR656 video interface, progressive mode for smart sensor, interlace mode for PAL and

NTSC input

• 8-bit input port for YCC, YUV, Bayer, or RGB data

• 32 × 32 FIFO storing image data supporting Core data read and DMA data burst transfer to system

memory

• Full control of 8-bit and 16-bit data to 32-bit FIFO packing

• Direct interface to eMMA-lt Pre-Processing block (PrP) - Not available on the i.MX27L

• Single interrupt source to interrupt controller from maskable sensor interrupt sources: Start of

Frame, End of Frame, Change of Field, FIFO full

• Configurable master clock frequency output to sensor

• Asynchronous input logic design. Sensor master clock can be driven by either the i.MX27/MX27L

processor or by external clock source.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

12

Freescale Semiconductor

Functional Description and Application Information

•

Statistic data generation for Auto Exposure (AE) and Auto White Balance (AWB) control of the

camera (for Bayer data only)

2.3.9

Configurable Serial Peripheral Interface (CSPI)

The Configurable Serial Peripheral Interface (CSPI) is used for fast data communication with fewer

software interrupts. There are three CSPI modules in the i.MX27/MX27L processors, which provide a

full-duplex synchronous serial interface, capable of interfacing to the SPI master and slave devices. CSPI1

and CSPI2 are master/slave configurable and include three chip selects to support multiple peripherals.

CSPI3 is only a master and has one chip-select signal. The transfer continuation function of the CSPI

enables unlimited length data transfers using 32-bit wide by 8-entry FIFO for both TX and RX data DMA

support.

The CSPI Ready (SPI_RDY) and Chip Select (SS) control signals enable fast data communication with

fewer software interrupts. When the CSPI module is configured as a master, it uses a serial link to transfer

data between the CSPI and an external device. A chip-enable signal and a clock signal are used to transfer

data between these two devices. When the CSPI module is configured as a slave, the user can configure

the CSPI Control register to match the external SPI master’s timing.

2.3.10

Direct Memory Access Controller (DMAC)

The Direct Memory Access Controller (DMAC) provides 16 channels to support linear memory, 2D

memory, FIFO, and end-of-burst enable FIFO transfers to support a wide variety of DMA operations.

Features include the following:

• Support of 16 channels linear memory, 2D memory, and FIFO for both source and destination

• Support of 8-bit, 16-bit, or 32-bit FIFO port size and memory port size data transfer

• Configurability of DMA burst length of up to a maximum of 16 words, 32 half-words, or 64 bytes

for each channel

• Bus utilization control for a channel that is not triggered by DMA request

• Interrupts that are provided to interrupt handler on bulk data transfer complete or transfer error

• DMA burst time-out error to terminate DMA cycle when the burst cannot be completed in a

programmed timing period

• Dedicated external DMA request and grant signal

• Support of increment, decrement, and no increment for source and destination addressing

• Support of DMA chaining

2.3.11

enhanced MultiMedia Accelerator Light (eMMA_lt)

The enhanced MultiMedia Accelerator Light (eMMA_lt) consists of the video pre-processor (PrP) and

post-processor (PP). In contrast with i.MX21 processor’s components, this eMMA does not include the

video codec. A more powerful video codec is included as a separate module.

NOTE

The i.MX27L does not have a eMMA_lt module.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

13

Functional Description and Application Information

Each module has individual control and configuration registers that are accessed via the IP interface, and

are capable of bus mastering the AMBA bus to independently access system memory without any CPU

intervention. This enables each module to be used independently of each other, and enables the

pre-processor and post-processor modules to provide acceleration features for other software codec

implementations and image processing software. These blocks work together to provide video

acceleration, and to off-load the CPU from computation intensive tasks. The PrP and PP can be used for

generic video pre- and post-processing, such as scaling, resizing, and color space conversions. A

32-bit-to-64-bit AHB gasket is used to convert a PrP AHB bus from a 32-bit to 64-bit protocol. A bypass

function is implemented to bypass this 64-bit gasket if it is not needed.

eMMA_lt supports the following image/video processing features:

• Pre-processor:

— Data input:

– System memory

– Private DMA between CMOS Sensor Interface module and pre-processor

— Data input formats:

– Arbitrarily formatted RGB pixels (16 or 32 bits)

– YUV 4:2:2 (Pixel interleaved)

– YUV 4:2:0 (IYUV, YV12)

— Input image size: 32 × 32 to 2044 × 2044

— Image scaling:

– Programmable independent CH-1 and CH-2 resizer. Can program to be in cascade or

parallel.

– Each resizer supports downscaling ratios from 1:1 to 8:1 in fractional steps.

— Channel-1 output data format

– Channel 1

– RGB 16 and 32 bpp

– YUV 4:2:2 (YUYV, YVYU, UYVY, VYUY)

— Channel-2 output data format

– YUV 4:2:2 (YUYV)

– YUV 4:4:4

– YUV 4:2:0 (IYUV, YV12)

– RGB data and YUV data format can be generated concurrently

— 32/64-bit AHB bus

• Post-processor

— Input data:

– From system memory

— Input format:

– YUV 4:2:0 (IYUV, YV12)

— Image Size: 32 × 32 to 2044 × 2044

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

14

Freescale Semiconductor

Functional Description and Application Information

— Output format:

– YUV 4:2:2 (YUYV)

– RGB16 and RGB32 bpp

— Image Resize

– Upscaling ratios ranging from 1:1 to 1:4 in fractional steps

– Downscaling ratios ranging from 1:1 to 2:1 in fractional steps and a fixed 4:1

– Ratios provide scaling between QCIF, CIF, QVGA (320 × 240, 240 × 320)

2.3.12

Enhanced Synchronous Dynamic RAM Controller (ESDRAMC)

The Enhanced Synchronous Dynamic RAM Controller (ESDRAMC) provides an interface and control for

synchronous DRAM memories for the system. SDRAM memories use a synchronous interface with all

signals registered on a clock edge. A command protocol is used for initialization, read, write, and refresh

operations to the SDRAM, and is generated on the signals by the controller (when required due to external

or internal requests). It has support for both single data rate RAMs and double data rate SDRAMs. It

supports 64 Mbits, 128 Mbits, 256 Mbits, and 512 Mbits, 1 Gbit, 2 Gbits, four bank synchronous DRAM

by two independent chip selects and with up to 256 Mbytes addressable memory per chip select.

2.3.13

Fast Ethernet Controller (FEC)

The Fast Ethernet Controller (FEC) is designed to support both 10 and 100 Mbps

Ethernet/IEEE Std 802.3™ networks. An external transceiver interface and transceiver function are

required to complete the interface to the media. The FEC supports the 10/100 Mbps MII and the 10

Mbps-only 7-wire interface, which uses a subset of the MII pins for connection to an external Ethernet

transceiver.

The FEC incorporates the following features:

• Support for three different Ethernet physical interfaces:

— 100-Mbps IEEE 802.3 MII

— 10-Mbps IEEE 802.3 MII

— 10-Mbps 7-wire interface (industry standard)

• IEEE 802.3 full duplex flow control

• Programmable max frame length supports IEEE Std 802.1™ VLAN tags and priority

• Support for full-duplex operation (200 Mbps throughput) with a minimum system clock rate of

50 MHz

• Support for half-duplex operation (100 Mbps throughput) with a minimum system clock rate of

25 MHz

• Retransmission from transmit FIFO following a collision (no processor bus utilization)

• Automatic internal flushing of the receive FIFO for runts (collision fragments) and address

recognition rejects (no processor bus utilization)

• Address recognition

— Frames with broadcast address may be always accepted or always rejected

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

15

Functional Description and Application Information

•

•

•

— Exact match for single 48-bit individual (unicast) address

— Hash (64-bit hash) check of individual (unicast) addresses

— Hash (64-bit hash) check of group (multicast) addresses

— Promiscuous mode

Independent DMA engine with multiple channels allowing transmit data, transmit descriptor,

receive data, and receive descriptor accesses to provide high performance

Independent RISC-based controller that provides the following functions in the FEC:

— Initialization (those internal registers not initialized by the user or hardware)

— High level control of the DMA channels (initiating DMA transfers)

— Interpreting buffer descriptors

— Address recognition for receive frames

— Random number generation for transmit collision backoff timer

The Message Information Block (MIB) in FEC maintains counters for a variety of network events

and statistics. The counters supported are the RMON (RFC 1757) Ethernet Statistics group and

some of the IEEE 802.3 counters.

2.3.14

General Purpose I/O Module (GPIO)

The general-purpose input/output (GPIO) module provides dedicated general-purpose pins that can be

configured as either inputs or outputs. When it is configured as an output, you can write to an internal

register to control the state driven on the output pin. When configured as an input, you can detect the state

of the input by reading the state of an internal register. The GPIO includes all of the general purpose

input/output logic necessary to drive a specific data to the pad and control the direction of the pad using

registers in the GPIO module. The ARM926 is able to sample the status of the corresponding pads by

reading the appropriate status register. The GPIO supports up to 32 interrupts and has the ability to identify

interrupt edges as well as generate three active high interrupts.

2.3.15

General Purpose Timer (GPT)

The i.MX27/MX27L processors contains six identical 32-bit General Purpose Timers (GPT) with

programmable prescalers and compare and capture registers. Each timer’s counter value can be captured

using an external event, and can be configured to trigger a capture event on the rising or/and falling edges

of an input pulse. Each GPT can also generate an event on the TOUT pin, and an interrupt when the timer

reaches a programmed value. Each GPT has an 11-bit prescaler that provides a programmable clock

frequency derived from multiple clock sources, including ipg_clk_32k, ipg_clk_perclk, ipg_clk_perclk/4,

and external clock from the TIN pin. The counter has two operation modes: free-run and restart mode. The

GPT can work in low-power mode.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

16

Freescale Semiconductor

Functional Description and Application Information

2.3.16

Inter IC Communication (I2C)

Inter IC Communication (I2C) is a two-wire, bidirectional serial bus that provides a simple, efficient

method of data exchange, minimizing the interconnection between devices. This bus is suitable for

applications requiring occasional communications over a short distance between many devices. The

flexible I2C enables additional devices to be connected to the bus for expansion and system development.

The I2C operates up to 400 kbps dependent on pad loading and timing. (For pad requirement details, refer

to Phillips I2C Bus Specification, Version 2.1.) The I2C system is a true multiple-master bus, including

arbitration and collision detection that prevents data corruption if multiple devices attempt to control the

bus simultaneously. This feature supports complex applications with multiprocessor control and can be

used for rapid testing and alignment of end products through external connections to an assembly-line

computer.

2.3.17

IC Identification Module (IIM)

The IC Identification Module (IIM) provides an interface for reading and in some cases programming

and/or overriding identification and control information stored in on-chip fuse elements. The module

supports laser fuses (L-Fuses) or electrically-programmable poly fuses (e-Fuses) or both.

Contact your Freescale Semiconductor sales office or distributor for additional information on SCC, RTIC,

IIM, SAHARA2

2.3.18

JTAG Controller (JTAGC)

The JTAG Controller (JTAGC) module supports debug access to the ARM926 Platform and tristate enable

of the I/O pads. The overall strategy is to achieve good test and debug features without increasing the pin

count and reducing the complexity of I/O muxing. The JTAG Controller is compatible with

IEEE Std 1149.1™ Standard Test Access Port and Boundary Scan Architecture.

2.3.19

Keypad Port (KPP)

The Keypad Port (KPP) is designed to interface with a keypad matrix with 2-contact or 3-point contact

keys. KPP is designed to simplify the software task of scanning a keypad matrix. With appropriate

software support, the KPP is capable of detecting, debouncing, and decoding one or multiple keys pressed

simultaneously in the keypad. The KPP supports up to 8 × 8 external key pad matrix. Its port pins can be

used as general purpose I/O. Using an open drain design, the KPP includes glitch suppression circuit

design, multiple keys, long key, and standby key detection.

2.3.20

Liquid Crystal Display Controller (LCDC)

The Liquid Crystal Display Controller (LCDC) provides display data for external gray-scale or color LCD

panels. The LCDC is capable of supporting black-and-white, gray-scale, passive-matrix color (passive

color or CSTN), and active-matrix color (active color or TFT) LCD panels.

The LCDC provides the following features:

• Configurable AHB bus width (32-bit/64-bit)

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

17

Functional Description and Application Information

•

•

•

Support for single (non-split) screen monochrome or color LCD panels and self-refresh type LCD

panels

16 simultaneous gray-scale levels from a palette of 16 for monochrome display

Support for:

— Maximum resolution of 800 × 600

— Passive color panel:

– 4 (mapped to RGB444)/8 (mapped to RGB444)/12 (RGB444) bits per pixel (bpp)

— TFT panel:

– 4 (mapped to RGB666)/8 (mapped to RGB666)/12 (RGB444)/16 (RGB565)/18 (RGB666)

bpp

— 16 and 256 colors out of a palette of 4096 colors for 4 bpp and 8 bpp CSTN display,

respectively

— 16 and 256 colors out of a palette of 256 colors for 4 bpp and 8 bpp TFT display, respectively

— True 4096 colors for a 12 bpp display

— True 64-Kbyte colors for 16 bpp

— True 256-Kbyte colors for 18 bpp

— 16-bit AUO TFT LCD Panel

— 24-bit AUO TFT LCD Panel

2.3.21

Multi-Master Memory Interface (M3IF)/M3IF-ESDCTL/MDDRC

Interface

The M3IF-ESDCTL/MDDRC interface is optimized and designed to reduce access latency by generating

multiple accesses through the dedicated ESDCTL/MDDRC arbitration (MAB) module, which controls the

access to and from the Enhanced SDRAM/MDDR memory controller. For the other port interfaces, the

M3IF only arbitrates and forwards the master requests received through the Master Port Gasket (MPG)

interface and M3IF Arbitration (M3A) module toward the respective memory controller. The masters that

interface with the M3IF include the ARM Platform, FEC, LCDC, H.264, and the USB. The controllers are

the ESDCTL/MDDRC, PCMCIA, NFC, and WEIM.

2.3.22

Multi-Layer AHB Crossbar Switch (MAX)

The ARM926EJ-S processor’s instruction and data buses—and all alternate bus master

interfaces—arbitrate for resources via a 6 × 34 Multi-Layer AHB Crossbar Switch (MAX). There are six

(M0–M5) fully functional master ports and three (S0–S2) fully functional slave ports. The MAX is

uni-directional. All master and slave ports are AHB-Lite compliant.

The design of the crossbar switch enables concurrent transactions to proceed from any master port to any

slave port. That is, it is possible for all three slave ports to be active at the same time as a result of three

independent master requests. If a particular slave port is simultaneously requested by more than one master

port, arbitration logic exists inside the crossbar to allow the higher priority master port to be granted the

bus, while stalling the other requestor(s) until that transaction has completed. The slave port arbitration

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

18

Freescale Semiconductor

Functional Description and Application Information

schemes supported are fixed, programmable fixed, programmable default input port parking, and a round

robin arbitration scheme.

The Crossbar Switch also monitors the ccm_br input (clock control module bus request), which requests

a bus grant from all four slave ports. The priority of ccm_br is programmable and defaults to the highest

priority. Upon receiving bus grants for all four output ports, the ccm_bg output will assert. At this point,

the clock control and reset module (CRM) can turn off hclk and be assured there are no outstanding AHB

transactions in progress. Once the CRM is granted a port, no other master will receive a grant on that port

until the CRM bus request (ccm_br) negates.

2.3.23

Memory Stick Host Controller (MSHC)

The Memory Stick Host Controller (MSHC) is located between the AIPI and the Sony Memory Stick and

provides support for data transfers between the i.MX27 processor and the Memory Stick (MS). The MSHC

consists of two sub-modules; the MSHC gasket and the Sony Memory Stick Host Controller (SMSC). The

SMSC module, which is the actual memory stick host controller, is compatible with Sony Memory Stick

Ver 1.x and Memory Stick PRO. The gasket connects the AIPI IP bus to the SMSC interface to allow

communication and data transfers via the IP Bus.

NOTE

The i.MX27L does not include the MSHC feature.

The MSHC gasket uses a reduced IP Bus interface that supports the IP bus read/write transfers that include

a back-to-back read or write. DMA transfers also take place via the IP Bus interface.

A transfer can be initiated by the DMA or the host (through the AIPI) response to an MSHC DMA request

or interrupt. The SMSC has two DMA address modes—a single address mode and a dual address mode.

The MSHC is set to dual-address mode for transfers with the DMA. In dual-address mode, when the

MSHC requests a transfer with the DMA request (XDRQ), the DMA will initiate a transfer to the MSHC.

NOTE

Details regarding the operation of the MSHC module can be found

separately in Memory Stick/Memory Stick PRO Host Controller IP

Specification 1.3.

2.3.24

NAND Flash Controller (NFC)

NAND Flash Controller (NFC) interfaces standard NAND Flash devices to the i.MX27/MX27L

processors and hides the complexities of accessing the NAND Flash. It provides a glueless interface to

both 8-bit and 16-bit NAND Flash parts with page sizes of 512 Bytes or 2 Kbytes. Its addressing scheme

enables it to access flash devices of almost limitless capacity. The 2-Kbyte RAM buffer of the NAND

Flash is used as the boot RAM during a cold reset (if the i.MX27/MX27L device is configured for a boot

to be carried out from the NAND Flash device). After the boot procedure completes, the RAM is available

as buffer RAM. In addition, the NAND Flash controller provides an X16-bit and X32-bit interface to the

AHB bus on the chip side, and an X8/X16 interface to the NAND Flash device on the external side.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

19

Functional Description and Application Information

2.3.25

Personal Computer Memory Card International Association

(PCMCIA)

The Personal Computer Memory Card International Association (PCMCIA) provides the PCMCIA 2.1

standard, which defines the usage of memory and I/O devices as insertable and exchangeable peripherals

for personal computers or PDAs. Examples of these types of devices include CompactFlash and WLAN

adapters.

The pcmcia_if host adapter module provides the control logic for PCMCIA socket interfaces, and requires

some additional external analog power switching logic and buffering. The additional external buffers

allow the pcmcia_if host adapter module to support one PCMCIA socket. The pcmcia_if shares its chip

level I/O with the external interface to memory (EIM) pins. Additional logic is required to multiplex the

EIM and the pcmcia_if on the same pins.

2.3.26

Digital Phase Lock Loop (DPLL)

Two on-chip Digital Phase Lock Loop (DPLLs) provide clock generation in digital and mixed

analog/digital chips designed for wireless communication and other applications. The DPLLs produce a

high-frequency chip clock signals with a low frequency and phase jitter.

2.3.27

Pulse-Width Modulator (PWM)

The Pulse-Width Modulator (PWM) has a 16-bit counter and is optimized to generate sounds from stored

sample audio images; it can also generate tones. The PWM uses 16-bit resolution and a 4 × 16 data FIFO

to generate sound. The 16-bit up-counter has a source selectable clock with 4 × 16 FIFO to minimize

interrupt overhead. Clock-in frequency is controlled by a 12-bit prescaler for the division of a clock.

Capable of sound and melody generation, the PWM has an active-high or active-low configurable output,

and can be programmed to be active in low-power and debug modes. The PWM can be programmed to

generate interrupts at compare and rollover events.

2.3.28

Real Time Clock (RTC)

The Real Time Clock (RTC) module maintains the system clock, provides stopwatch, alarm, and

interrupt functions, and supports the following features:

• Full clock—days, hours, minutes, seconds

• Minute countdown timer with interrupt

• Programmable daily alarm with interrupt

• Sampling timer with interrupt

• Once-per-day, once-per-hour, once-per-minute, and once-per-second interrupts

• Operation at 32.768 kHz or 32 kHz, or 38.4 kHz (determined by reference clock crystal)

The prescaler converts the incoming crystal reference clock to a 1 Hz signal, which is used to increment

the seconds, minutes, hours, and days TOD counters. The alarm functions, when enabled, generate RTC

interrupts when the TOD settings reach programmed values. The sampling timer generates

fixed-frequency interrupts, and the minute stopwatch allows for efficient interrupts on very small

boundaries.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

20

Freescale Semiconductor

Functional Description and Application Information

2.3.29

Run-TIme Integrity Checker (RTIC)

The Run-Time Integrity Checker (RTIC) is one of the security components in the i.MX27/MX27L

processors. Its purpose is to ensure the integrity of the peripheral memory contents and assist with boot

authentication. The RTIC has the ability to verify the memory contents during system boot and during

run-time execution. If the memory contents at runtime fail to match the hash signature, an error in the

security monitor is triggered.

Contact your Freescale Semiconductor sales office or distributor for additional information on SCC, RTIC,

IIM, SAHARA2

2.3.30

Symmetric/Asymmetric Hashing and Random Accelerator

(SAHARA2)

SAHARA2 is a security co-processor, it implements encryption algorithms (AES, DES, and 3DES),

hashing algorithms (MD5, SHA-1, SHA_224, and SHA-256), stream cipher algorithm (ARC4), and a

hardware random number generator.

Contact your Freescale Semiconductor sales office or distributor for additional information on SCC, RTIC,

IIM, SAHARA2

2.3.31

Security Controller Module (SCC)

The Security Controller Module (SCC) is a hardware security component. Overall, its primary

functionality is associated with establishing a centralized security state controller and hardware security

state with a hardware configured, unalterable security policy.

Contact your Freescale Semiconductor sales office or distributor for additional information on SCC, RTIC,

IIM, and SAHARA2.

2.3.32

Secure Digital Host Controller (SDHC)

The Secure Digital Host Controller (SDHC) controls the MultiMedia Card (MMC), Secure Digital (SD)

memory, and I/O cards by sending commands to cards and performing data accesses to/from the cards. The

Multimedia Card/Secure Digital Host (MMC/SD) module integrates both MMC support along with SD

memory and I/O functions. The SDHC is fully compatible with the MMC System Specification Version

3.0, as well as with the SD Memory Card Specification 1.0, and SD I/O Specification 1.0 with 1/4

channel(s). The maximum data rate in 4-bit mode is 100 Mbps. The SDHC uses a built-in programmable

frequency counter for the SDHC bus, and provides a maskable hardware interrupt for an SDIO interrupt,

internal status, and FIFO status. It has a pair of 32 × 16-bit data FIFO buffers built in.

The MultiMedia Card (MMC) is a universal, low-cost data storage and communication media that is

designed to cover a wide area of applications, including, for example, electronic toys, organizers, PDAs,

and smart phones. The MMC communication is based on an advanced 7-pin serial bus designed to operate

in a low-voltage range.

The Secure Digital Card (SD) is an evolution of MMC technology, with two additional pins in the form

factor. It is specifically designed to meet the security, capacity, performance, and environment

requirements inherent in newly emerging audio and video consumer electronic devices. The physical form

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

21

Functional Description and Application Information

factor, pin assignment, and data transfer protocol are forward-compatible with the MultiMedia Card with

some additions. Under SD, it can be categorized into Memory and I/O. The memory card invokes a

copyright protection mechanism that complies with the security of the SDMI standard, which is faster and

provides the capability for a higher memory capacity. The I/O card provides high-speed data I/O with

low-power consumption for mobile electronic devices.

2.3.33

Smart Liquid Crystal Display Controller Module (SLCDC)

The Smart Liquid Crystal Display Controller (SLCDC) module transfers data from the display memory

buffer to the external display device. Direct Memory Access (DMA) transfers the data transparently with

minimal software intervention. Bus utilization of the DMA is controllable and deterministic.

As cellular phone displays become larger and more colorful, demands on the processor increase. More

CPU power is needed to render and manage the image. The role of the display controller is to reduce the

CPU’s involvement in the transfer of data from memory to the display device so the CPU can concentrate

on image rendering. DMA is used to optimize the transfer. Embedded control information needed by the

display device is automatically read from a second buffer in system memory and inserted into the data

stream at the proper time to completely eliminate the CPU’s role in the transfer.

A typical scenario for a cellular phone display is to have the display image rendered in main system

memory. After the image is complete, the CPU triggers the SLCDC module to transfer the image to the

display device. Image transfer is accomplished by burst DMA, which steals bus cycles from the CPU.

Cycle-stealing behavior is programmable so bus use is kept within predefined bounds. After the transfer

is complete, a maskable interrupt is generated indicating the status. For animated displays, it is suggested

that a two-buffer ping-pong scheme be implemented so that the DMA is fetching data from one buffer

while the next image is rendered into the other.

Several display sizes and types are used in the various products that use the SLCDC. The SLCDC module

has the capability of directly interfacing to the selected display devices. Both serial and parallel interfaces

are supported. The SLCDC module only supports writes to the display controller. SLCDC read operations

from the display controller are not supported.

2.3.34

Synchronous Serial Interface (SSI)

The Synchronous Serial Interface (SSI) is a full-duplex serial port that allows the chip to communicate

with a variety of serial devices. These serial devices can be standard codecs, Digital Signal Processors

(DSPs), microprocessors, peripherals, and popular industry audio codecs that implement the inter-IC

sound bus standard (I2S) and Intel AC97 standard.

The SSI is typically used to transfer samples in a periodic manner. The SSI consists of independent

transmitter and receiver sections with independent clock generation and frame synchronization.

The SSI contains independent (asynchronous) or shared (synchronous) transmit and receive sections with

separate or shared internal/external clocks and frame syncs, operating in Master or Slave mode. The SSI

can work in Normal mode operation using frame sync, and in Network mode operation allowing multiple

devices to share the port with as many as thirty-two time slots.

The SSI provides two sets of Transmit and Receive FIFOs. Each of the four FIFOs is 8 × 24 bits. The two

sets of Tx/RX FIFOs can be used in Network mode to provide two independent channels for transmission

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

22

Freescale Semiconductor

Functional Description and Application Information

and reception. It also has programmable data interface modes such as I2S, LSB, and MSB aligned and

programmable word lengths. Other program options include frame sync, clock generation, and

programmable I2S modes (Master, Slave, or Normal). Oversampling clock, ccm_ssi_clk is available as

output from SRCK in I2S Master mode.

In addition to AC97 support, the SSI has completely separate clock and frame sync selections for the

receive and transmit sections. In the AC97 standard, the clock is taken from an external source and frame

sync is generated internally. The SSI also has a programmable internal clock divider and Time Slot Mask

registers for reduced CPU overhead (for Tx and RX both).

2.3.35

Universal Asynchronous Receiver/Transmitter (UART)

The i.MX27/MX27L processors contain six UART modules. Each UART module is capable of standard

RS-232 non-return-to-zero (NRZ) encoding format and IrDA-compatible infrared modes. The UART

provides serial communication capability with external devices through an RS-232 cable or through use

of external circuitry that converts infrared signals to electrical signals (for reception); or it transforms

electrical signals to signals that drive an infrared LED (for transmission) to provide low-speed IrDA

compatibility.

The UART transmits and receives characters that are either 7 or 8 bits in length (program selectable). To

transmit, data is written from the peripheral data bus to a 32-byte transmitter FIFO (TxFIFO). This data is

passed to the shift register and shifted serially out on the transmitter pin (TXD). To receive, data is received

serially from the receiver pin (RXD) and stored in a 32-half-word-deep receiver FIFO (RxFIFO). The

received data is retrieved from the RxFIFO on the peripheral data bus. The RxFIFO and TxFIFO generate

maskable interrupts as well as DMA requests when the data level in each of the FIFO reaches a

programmed threshold level.

The UART generates baud rates based on a programmable divisor and input clock. The UART also

contains programmable auto baud detection circuitry to receive 1 or 2 stop bits as well as odd, even, or no

parity. The receiver detects framing errors, idle conditions, BREAK characters, parity errors, and overrun

errors.

2.3.36

Universal Serial Bus (USB)

The i.MX27/MX27L processors provide three USB ports. The USB module provides high performance

USB On-The-Go (OTG) functionality, compliant with the USB 2.0 specification, the OTG supplement,

and the ULPI 1.0 Low Pin Count specification. The module consists of three independent USB cores, each

controlling one USB port.

In addition to the USB cores, the USB module provides for Transceiverless Link (TLL) operation on host

Ports 1 and 2, and provides the ability of routing the OTG transceiver interface to Host Port 1 such that

this transceiver can be used to communicate with a USB peripheral connected to Host Port 1. The USB

module has two connections to the CPU bus—one IP-bus connection for register accesses and one

AHB-bus connection for the DMA transfer of data to and from the FIFOs.

The USB module includes the following features:

• Full Speed/Low speed Host only core (HOST 1)

• Transceiverless Link Logic (TLL) for on board connection to a FS/LS USB peripheral

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

23

Functional Description and Application Information

•

•

•

•

•

Bypass mode to route Host Port 1 signals to OTG I/O port

High Speed /Full Speed/Low Speed Host Only core (Host 2)

Full Speed/Low Speed interface for Serial transceiver

TLL function for direct connection to USB peripheral in FS/LS (serial) operation

High-speed OTG core

The USB module has two main modes of operation: Normal mode and Bypass mode. Furthermore, the

USB interfaces can be configured for high-speed operation (480 Mbps) and/or full/low speed operation

(12/1.5 Mbps). In Normal mode, each USB core controls its corresponding port. In additional to th4e

major operational modes, each port can work in one or more modes, as follows:

PHY mode

In PHY mode, an external serial transceiver is connected to the port. This is used

for off-board USB connections.

TLL mode

In TLL mode, internal logic is enabled to emulate the functionality of two

back-to-back connected transceivers. This mode is typically used for on-board

USB connections to USB-capable peripherals.

Host Port 2 supports ULPI and Serial Transceivers. The OTG port requires a transceiver and is intended

for off-board USB connections.

Serial Interface mode In serial mode, a serial OTG transceiver must be connected. The port does not

support dedicated signals for OTG signaling. Instead, a transceiver with built-in

OTG registers must be used. Typically, the transceiver registers are accessible

over an I2C or SPI interface.

ULPI mode

In this mode, a ULPI transceiver is connected to the port pins to support

high-speed off board USB connection.

Bypass mode

Bypass mode affects the operation of the OTG port and Host Port 1. This mode is

only available when a serial transceiver is used on the OTG port, and the

peripheral device on Port 1 is using a TLL connection. Bypass mode is activated

by setting the bypass bit in the USBCONTROL register. In this mode, the USB

OTG port connections are internally routed to the USB Host 1 port, such that the

transceiver on the OTG port connects to a peripheral USB device on Host Port 1.

The OTG core and the Host 1 core are disconnected from their ports when bypass

is active.

Low Power mode

Each of the three USB cores has an associated power control module that is

controlled by the USB core and clocked on a 32-kHz clock. When a USB bus is

idle, the transceiver can be placed in low-power mode (suspend), after which the

clocks to the USB core can be stopped. The 32-kHz low power clock must remain

active as it is needed for walk-up detection.

2.3.37

Watchdog Timer Module (WDOG)

The Watchdog Timer module (WDOG) protects against system failures by providing a method of escaping

from unexpected events or programming errors. Once the WDOG module is activated, it must be serviced

by software on a periodic basis. If servicing does not take place, the timer times out. Upon a time-out, the

WDOG Timer module either asserts the wdog signal or a system reset signal wdog_rst, depending on

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

24

Freescale Semiconductor

Functional Description and Application Information

software configuration. The WDOG Timer module also generates a system reset via a software write to

the Watchdog Control Register (WCR) when there is a detection of a clock monitor event, an external

reset, an external JTAG reset signal, or if a power-on-reset has occurred.

2.3.38

Wireless External Interface Module (WEIM)

The Wireless External Interface Module (WEIM) handles the interface to devices external to the chip,

including generation of chip selects, clocks and controls for external peripherals and memory. It provides

asynchronous and synchronous access to devices with an SRAM-like interface.

The WEIM includes six chip selects for external devices, with two CS signals covering a range of

128 Mbytes, and the other four each covering a range of 32 Mbytes. The 128-Mbyte range can be

increased to 256 Mbytes when combined with the two signals. The WEIM offers selectable protection for

each chip select as well as programmable data port size. There is a programmable wait-state generator for

each chip select and support for Big Endian and Little Endian modes of operation per access.

2.3.39

Video Codec

The Video Codec module is the video processing module in the i.MX27 processor. It supports full duplex

video codec with 25 fps VGA resolution, supports multi-party calls, and integrates multiple video

processing standards, including H.264 BP, MPEG-4 SP, and H.263 P3 (including annex I, J, K, and T), D1

resolution, 30 fps—half-duplex.

NOTE

The Video Codec feature is not available on the i.MX27L

It has three 64-bit AHB-Lite master bus interfaces connecting to the EMI, which includes two read

channels and one write channel. Its 32-bit AHB-Lite master bus is connected to ARM Platform to access

system-internal SRAM.

The Video Codec module contains three major architectural components: video codec processing IP,

AXI-to-AHB bus protocol transfer module, and a 32-bit to 64-bit AHB master bus protocol transfer

module.

The Video Codec module supports following video stream processing features:

• Multi-standard video codec

— MPEG-4 part-II simple profile encoding/decoding

— H.264/AVC baseline profile encoding/decoding

— H.263 P3 encoding/decoding

— Multi-party call: max processing four image/bitstream encoding and/or decoding

simultaneously

— Multi-format: for example, encodes MPEG-4 bitstream, and decodes H.264 bitstream

simultaneously

• Coding tools

— High-performance motion estimation

– Single reference frame for both MPEG-4 and H.264 encoding

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

Freescale Semiconductor

25

Signal Descriptions

•

•

3

– Support 16 reference frame for H.264 decoding

– Quarter-pel and half-pel accuracy motion estimation

– [+/-16, +/-16] Search range

– Unrestricted motion vector

— All variable block sizes are supported (in case of encoding, 8 × 4, 4 × 8, and 4 × 4 block sizes

are not supported).

— MPEG-4 AC/DC prediction and H.264 Intra prediction

— H.263 Annex I, J, K(RS = 0 and ASO =0), and T are supported. In case of encoding, the Annex

I and K(RS=1 or ASO=1) are not supported.

— CIR (Cyclic Intra Refresh)/AIR (Adaptive Intra Refresh)

— Error resilience tools

– MPEG-4 re-synchronize marker and data-partitioning with RVLC (fixed number of

bits/macroblocks between macroblocks)

– H.264/AVC FMO and ASO

– H.263 slice structured mode

— Bit-rate control (CBR and VBR)

Pre/post rotation/mirroring

— 8 rotation/mirroring modes for image to be encoded

— 8 rotation/mirroring modes for image to be displayed

Programmability

— Embeds 16-bit DSP processor that is dedicated to processing bitstream and driving codec

hardware

— General purpose registers and interrupt generation for communication between system and

video codec module

Signal Descriptions

This section discusses the following:

• Identifies and defines all device signals in text, tables, and (as appropriate) figures. Signals can be

organized by group, as applicable.

• Contains pin-assignment/contact-connection diagrams, if the sequence of information in the data

sheet requires them to be included here.

Table 3 shows the i.MX27/MX27L signal descriptions.

Table 3. i.MX27/MX27L Signal Descriptions

Pad Name

Function/Notes

External Bus/Chip Select (EMI)

A [13:0]

Address bus signals, shared with SDRAM/MDDR, WEIM and PCMCIA, A[10] for

SDRAM/MDDR is not the address but the pre-charge bank select signal.

i.MX27 and i.MX27L Data Sheet, Rev. 1.8

26

Freescale Semiconductor

Signal Descriptions

Table 3. i.MX27/MX27L Signal Descriptions (continued)

Pad Name

Function/Notes

MA10

Address bus signals for SDRAM/MDDR

A [25:14]

Address bus signals, shared with WEIM and PCMCIA

SDBA[1:0]

SDRAM/MDDR bank address signals

SD[31:0]

Data bus signals for SDRAM, MDDR

SDQS[3:0]

MDDR data sample strobe signals

DQM0–DQM3

SDRAM data mask strobe signals

EB0