ECE 1250 Lab 5 Measuring Voltages for Op-Amp Building

advertisement

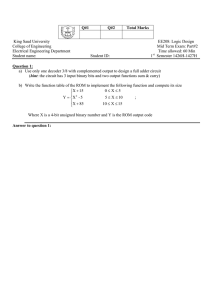

ECE 3300 Lab 2 ECE 1250 Lab 5 Measuring Voltages for Op-Amp Building: Resistive Networks and Op-Amp Circuit Design and Build a Digital Power Supply Overview: In Lab 5 you will: • Build an R-2R ladder for converting binary numbers to analog voltages • Build an op-amp circuit to add gain • Measure voltages. • Observe voltage waveforms on the myDAQ oscilloscope This lab is another example of an op-amp in action. The Digital-to-Analog (D/A) circuit you build in this lab is like the one in your MP3 player that turns a series of stored binary numbers (patterns of 1's and 0's) into voltages that represent a music waveform. The 1's and 0's are just voltages that are high (+15 V in our case) and low (0 V). In this lab, you will use dip switches to connect inputs of a circuit to a 1 (+15 V) or to a 0 (0 V = reference). Our D/A circuit will have three binary inputs, which allows us to have eight binary patterns of input: 000, 001, 010, 011, 100, 101, 110, 111. For each binary input, our circuit will output a different voltage. Thus, we are building a digital power supply. This circuit will output 0, 1, 2, 3, 4, 5, 6, or 7 Volts. Equipment List: • myDAQ board with cables. (You can hook them to the lab computers if you don’t want to bring your laptop.) • Multisim software. • From previous labs: o Protoboard & wire kit o Resistor: 10 kΩ • Additional parts: o 12 Resistors: values to be determined in lab o Potentiometer (50kΩ) o LM324 quad op-amp o Dip switch module (optional but convenient) Instructions & Reference Material: • myDAQ as voltmeter https://utah.instructure.com/courses/266578/assignments/1347122 • Multisim demos : See DVD in back of your book. • Data Sheets: LM324 quad op-amp http://www.ti.com/lit/ds/symlink/lm124-n.pdf 1 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 3300 LAB 5 I. PreLab: A. Review the D/A problem from MATLAB Lecture 2 problems, problem 2: https://utah.instructure.com/courses/266578/assignments/1467277 The D/A converter part of our digital power supply circuit is shown below in Fig. 1 and is the same as the Lecture 2 problem 2. The matrix equation for our circuit where we have 15 V inputs instead of 5 V inputs may be written as follows: ⎤ ⎡ v2 / 2 ⎤ ⎥ ⎢ ⎥ ⎥ = ⎢ v1 / 2 ⎥ ⎥ ⎢ v /2 ⎥ ⎦ ⎣ 0 ⎦ Use MATLAB and the matrix equation in the lecture notes to determine the expected output voltage, vD/A, from the circuit when the input voltages are the following: v0 = 15 V (binary 1) v1 = 0 V (binary 0) v2 = 15 V (binary 1) ⎡ 2 −1 0 ⎢ ⎢ −1 5 / 2 −1 −1 3 / 2 ⎢⎣ 0 ⎤ ⎡ vA ⎥⎢ v ⎥⎢ B ⎥⎦ ⎢ vD/A ⎣ Fig. 1 R-2R ladder D/A circuit with 3 inputs B. Look through the data sheets for the LM324: http://www.ti.com/lit/ds/symlink/lm124-n.pdf Find the connection diagram on the 2nd page (which you will need to construct the circuit). Note that the only difference between the LM124, LM224, and LM324 is the operating temperature range (see 3rd page of datasheets). C. (Optional) You will be faster if you do the Multisim simulation in II.E before you come to lab. If you do not have Multisim running on your PC yet, then do the Multisim simulation on the lab computers. II. R-2R Ladder (10 points) A. Design: The R-2R ladder part of the D/A circuit is shown above in Fig. 1. The value of R cancels out in this circuit. That is, vD/A does not depend on the value of R. In practice, however, we want a value of R that will result in currents around 100 µA. Much smaller currents than 100 µA result in circuit noise that is undesirably large. Much larger currents than 100 µA result in wasted power or excessive current drain from the power supply. 2 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 3300 LAB 5 The R-2R ladder, has an interesting property that it may be extended in either direction for as far as desired and its input resistance will remain 2R. Without doing a detailed solution of the currents in the circuit, come up with a rough estimate of the resistance seen by voltage source v2 as a function of R. Hint: you have 2R in series with two R-2R ladders (approximately) in both directions. So are those two ladders in series or parallel? Input R ≈ times R I≈ for 15 V input Choose a standard 5% tolerance value of R that you will use in your circuit for input currents around 100 µA. (You also want an R value for which there is also a standard 2R value.) R choice: List of standard 5% resistor values: http://ieee.ucsd.edu/wiki/_media/tutorials/standard_resistor_and_capaciter_values.pdf B. Build: Construct the R-2R ladder circuit as shown in Fig. 2. Use the binary input pattern 101 from the Pre-lab. For a 1, connect to the 15 V power supply. For a 0, connect to reference. If you wish, you may use dip switches as shown in Fig. 3 to select whether inputs are 0 or 1. (If you use the dip switches, use only the 0 switch or the 1 switch but not both for a given input at a given time. If you close both switches at once, no harm is done, but you get strange results.) Fig. 2 R-2R ladder D/A circuit with 3 inputs Fig. 3 R-2R ladder D/A with dip switches. C. Measure: Use the voltmeter on the myDAQ to measure the value of vD/A. Compare it with the value you calculated in the Pre-lab part A. vD/A = 3 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 3300 LAB 5 D. Experiment: Try several different binary input voltages for the R-2R ladder circuit and see if the results are an output voltage proportional to the binary input number. Note that v0 is the most significant bit in the binary input number. number 5 = binary input number 101 vD/A = number = binary input number vD/A = number = binary input number vD/A = number = binary input number vD/A = Multisim: Use the Multisim circuit file provided in the following file on the class Canvas site to simulate the R-2R ladder circuit and compare the output voltages with the results from D: Lab5_DAconvertr.ms12 (you should find that vD/A is proportional to the input number) number binary vD/A 5 101 III. Op-Amp Amplifier (10 points) A. Design: Add a positive-gain op-amp amplifier circuit to your R-2R ladder to scale the vD/A value to 0-7 V for binary number inputs 0-7, as shown in Fig. 4. The first stage of this amplifier is a buffer followed by a voltage divider on its output that divides the voltage by two. The second stage is a positive-gain amplifier. The gain of the two stages together is the product of the gains of each stage. The gain of the first stage is 1/2 because of the voltage divider. Determine the value of resistance needed where the 50 kΩ potentiometer is located: R for 50 kΩ pot = _________________ Fig. 4 Digital voltage source with 3-input R-2R ladder D/A. 4 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 3300 LAB 5 B. Build: Build the complete circuit, as shown in Fig. 4. (You may wish to use dip switches for the D/A inputs as shown in Fig. 3.) On the schematic diagram in Fig. 4, show all component values, and label pin numbers on the op-amps. C. Measurement: Adjust the potentiometer so that your circuit outputs 7.0 V when the input number is 111 = 7. Then, using the myDAQ voltmeter, record the output voltage for each binary input to your circuit. number binary vD/A 0 000 1 001 2 010 3 011 4 100 5 101 6 110 7 111 5 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu