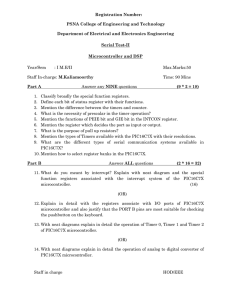

Chapter 8

advertisement

The 68HC12 Microcontroller Chapter 8 68HC12 Port T Timer Functions Input Capture (IC) Output Compare (OC) Pulse Accumulator Input (PAI) H. Huang Transparency No.8-1 The 68HC12 Microcontroller Port T: Timer Port - Port can be used as a general I/O pin (configured by DDRT) , or … - Individual pins can be selected to provide a timer function: - input capture: measuring timing of incoming signals/interrupts - output compare: generating timed outgoing signals/interrupts - pulse accumulator (Pin 7 only): counting incoming signals/interrupts -Port T timer functions are based on Enhanced Timer Capture Module - Central to its operations: Timer Counter Register (TCNT) • 16-bit up-counter • When enabled, automatically increments on every clock tick • Read: “current time” • Must be read in one 16-bit operation. • Write: reset value in counter H. Huang Transparency No.8-2 The 68HC12 Microcontroller What is Output Compare ? • Each (of the 8) output compare channels consist of – 16-bit compare register TCx (also used for input capture) – output action pin PTx – interrupt request circuit – control logic (key logic: comparator) • Typical use: trigger an action at a specific time in the future • To use output-compare function: 1. copy current contents of the TCNT register, 2. add a value equal to the desired delay, and 3. store sum into an output-compare register (TCx, x = 0..7). H. Huang Transparency No.8-3 The 68HC12 Microcontroller What is Output Compare ? • On each TCNT tick, control logic will compare TCNT with TCx. If successful (i.e. equal) : • Set a flag to indicate success • request an interrupt, if enabled. • perform an action on the output action pin (pull low/high; toggle ) H. Huang Transparency No.8-4 The 68HC12 Microcontroller What is Input Capture ? • Each (of the 8) input compare channel consists of – 16-bit input capture register TCx (same used for output compare) R is ing e dge F alling e dge – input pin PTx – interrupt request circuit or – edge-detection logic F igur e 8 .3 E ve nts r e pr e s e nte d by s ignal e dge s • Typical use: Measure the time of external events – Physical time: represented by contents of the main timer (TCNT) – Event: a signal edge (rising or falling edge). – Time of event: latch count of main timer when a signal edge arrives. • To use input-capture function: - When detect edge, store current contents of TCNT register • Most of the circuit shared with output compare: cannot be enabled simultaneously. H. Huang Transparency No.8-5 The 68HC12 Microcontroller Applications of Input Capture function - Event arrival time recording - Period measurement: input capture function captures main timer values corresponding to two consecutive rising or falling edges one period (a) Capture two rising edges one period (b) Capture two falling edges Figure 8.8 Period measurement by capturing two consecutive edges - Pulse width measurement: capture the rising and falling edges Pulse width Rising edge Falling edge Figure 8.9 Pulse-width measurement using input capture H. Huang Transparency No.8-6 The 68HC12 Microcontroller -Interrupt generation: each input capture functions can be used as edge-sensitive interrupt sources. - Event counting: counting number of signal edges arrived during a period e1 e2 e3 e4 ... ei ... ej Start of interval End of interval Figure 8.10 Using an input-capture function for event counting - Time reference: often used in combination with output compare function Time t 0 Time t0 + delay Time of reference (set up by signal edge) Time to activate output signal (set up by output compare) Figure 8.11 A time reference application H. Huang Transparency No.8-7 The 68HC12 Microcontroller Duty Cycle Measurement T ΔT ΔT * 100% duty cycle = T Figure 8.12 Definition of duty cycle Phase Difference Measurement T s i g n al S 1 ΔT s i g n al S 2 ΔT p h as e d i f f e r e n c e = * 360o T F i g u r e 8 .1 3 P h as e d i f f e r e n c e d e f i n i t i o n f o r t w o s i g n al s H. Huang Transparency No.8-8 The 68HC12 Microcontroller Programming the Timer - Timer Counter Register (TCNT) Timer System Control Register (TSCR-TSCR1) - Set or clear the bit 7 (TEN) to start or stop counting of TCNT. 6 7 TEN value after reset 0 read: anytime write: anytime 5 TSWAI TSFRZ 0 0 4 3 2 1 0 TFFCA 0 0 0 0 0 0 0 0 0 TEN -- timer enable bit 0 = disable timer; this can be used to save power consumption 1 = allows timer to function normally Timer Interrupt Flag 2 Register (TFLG2) • Bit 7 (TOF) will be set whenever TCNT overflows. H. Huang Transparency No.8-9 The 68HC12 Microcontroller Timer Interrupt Mask Register 2 (TMSK2 – TSCR2) Table 8.1 Timer counter prescale factor PR2 PR1 PR0 0 0 0 0 1 1 1 1 TOI — Timer Overflow Interrupt Enable 0 = Interrupt inhibited 1 = Hardware interrupt requested if TOF flag set TCRE — Timer Counter Reset Enable 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 Prescale Factor 1 2 4 8 16 32 reserved reserved The timer counter can be reset by a successful output compare 7 event. (i.e. up-counting modulus counter). 0 = Counter reset inhibited and counter free runs 1 = Counter reset by a successful output compare 7 PR2, PR1, PR0 — Timer Prescaler Select H. Huang Transparency No.8-10 The 68HC12 Microcontroller Timer Input Output Select Register (TIOS) • Selection of input capture and output compare on each bit of Port T 6 5 3 2 1 0 7 4 value IOS7 IOS6 IOS5 IOS4 IOS3 IOS2 IOS1 IOS0 after reset 0 0 0 0 0 0 0 0 IOS[7:0] -- Input capture or output compare channel configuration bits 0 = The corresponding channel acts as an input capture 1 = The corresponding channel acts as an output compare Figure 8.4 Timer input capture/output compare select register Example: Enable output-compare channels 7..4 and input-capture channels 3..0: movb #$F0,TIOS H. Huang Transparency No.8-11 The 68HC12 Microcontroller Timer Interrupt Flag 1 Register (TFLG1) - Status flag indicating when interrupt condition has occurred. - e.g. with input compare, when signal edge arrives, associated timer interrupt flag set to 1. - Flag must be cleared by writing a 1 to corresponding bit (unless TFFCA in TSCR set: any read/write from associated input/output channel will automatically clear it) value afterreset 7 6 5 4 3 2 1 0 C7F C6F C5F C4F C3F C2F C1F C0F 0 0 0 0 0 0 0 0 C7F-C0F: input capture/output compare interrupt flag bits 0 = interrupt condition has not occurred 1 = interrupt condition has occurred Figure 8.7 Timer interrupt flag 1 register H. Huang Transparency No.8-12 The 68HC12 Microcontroller Timer Mask Register 1 (TMSK1 – TIE, Timer Interrupt Enable) - Setting of a flag may optionally generate an interrupt to the CPU. - If cleared, corresponding flag is disabled from causing a HW interrupt; if set, enabled. value after reset 7 6 5 4 3 2 1 0 C7I C6I C5I C4I C3I C2I C1I C0I 0 0 0 0 0 0 0 0 C7I-C0I: input capture/output compare interrupt enable bits 0 = interrupt disabled 1 = interrupt enabled Figure 8.6 Timer interrupt mask 1 register (TMSK1) H. Huang Transparency No.8-13 The 68HC12 Microcontroller How to clear a timer flag bit? In normal mode, write a 1 to the flag bit to be cleared Method 1. Use BCLR instruction with a 0 at the bit position(s) corresponding to flag (s) to be cleared. For example, BCLR TFLG1, $FE will clear C0F flag. Method 2. Use movb instruction with a 1 at bit position (s) corresponding to flag (s) to be cleared. For example, movb #$01,TFLG1 will clear C0F flag. When fast timer flag clear function is enabled, see Figure 8.1. H. Huang Transparency No.8-14 The 68HC12 Microcontroller For Output Compare Only : TCTL1 and TCTL2 : Actions activated on an output compare pin include 1. pull up to high 2. pull down to low 3. toggle 6 5 7 4 value OM7 OL7 OM6 OL6 after reset 0 0 0 0 (a) TCTL1 register 6 5 7 4 value OM3 OL3 OM2 OL2 after reset 0 0 0 0 (b) TCTL2 register 3 2 OM5 OL5 0 0 1 0 OM4 OL4 0 0 3 2 OM1 OL1 0 0 1 0 OM0 OL0 0 0 OMn OLn : output level 0 0 no action (timer disconnected from output pin) 0 1 toggle OCn pin 1 0 clear OCn pin to 0 1 1 set OCn pin to high Figure 8.17 Timer control register 1 and 2 (TCTL1 & TCTL2) H. Huang Transparency No.8-15 The 68HC12 Microcontroller -Example 8.4. Generate 1 KHz digital waveform with 30 percent duty cycle from PT0 pin. Use polling to check success of output compare operation. E clock frequency: 8 MHz. Solution: - Set prescaler of TCNT to 8; period of clock signal to the TCNT will be 1 μs. The numbers of clock cycles that the signal is high and low are 300 and 700, respectively. 300 μ s 700 μ s Figure 8.18 1 KHz 30 percent duty cycle waveform H. Huang Transparency No.8-16 The 68HC12 Microcontroller high_time low_time equ equ 300 700 org bset movb movb movb ldd addd std $1000 TIOS,$01 #$03,TMSK2 #$01,TCTL2 #$90,TSCR TCNT #high_time TC0 high brclr ldd addd std TFLG1,$01,high TC0 #low_time TC0 ; wait until C0F flag is set low brclr ldd addd std bra end TFLG1,$01,low TC0 #high_time TC0 high ; wait until C0F flag is set ; ; ; ; select OC0 function set prescale factor to 8 select toggle as output compare action enable TCNT and fast timer flag clear ; start OC0 operation: 300 cycles delay H. Huang Transparency No.8-17 The 68HC12 Microcontroller Example 8.5 Write a function to generate a time delay of 1 second. E clock frequency is 8 MHz. Solution: Many ways. One method is 1. Set prescale factor to the TCNT to 8. Each clock period to the TCNT is 1 μs. 2. Perform 20 output-compare operations with each one creating 50 ms delay. delay_1s pshx movb movb movb ldx ldd again addd std brclr ldd dbne pulx rts #$90,TSCR ; #$03,TMSK2; #$01,TIOS ; #20 ; TCNT #50000 ; TC0 ; TFLG1,$01,* TC0 x,again enable TCNT & fast flags clear configure prescale factor to 8 enable OC0 prepare to do 20 OC0 actions start output compare operation with 50 ms time delay H. Huang Transparency No.8-18 The 68HC12 Microcontroller Example. Write a program that uses OC0 channel to generate variable frequency timing interrupts. Interrupt period should increase 500 clock ticks every time a new interrupt is generated. frequency What’s missing here ? tc0_isr msg org dw org FDB org movb movb movb bset cli jmp $4800 $f000 $3FEE tc0_isr $4000 #$90,TSCR #$05,TMSK2 #$01,TIOS TMSK1,$01 ldd addd std ldd addd std ldx jsr rti db TCNT frequency TC0 #$500 frequency frequency #msg $FF5E * ; Initial “frequency” ; On the Axiom board ; ; ; ; ; ; enable TCNT and fast timer set prescale factor to 32 select OC0 enable IC0 interrupt enable interrupts (background loop) ; ; ; ; TCNT in d TCNT + freq in D start OC operation: store D update interrupt frequency ; print a message on screen CR,LF,"Message",CR,LF,CR,LF,$04 H. Huang Transparency No.8-19 The 68HC12 Microcontroller For Input Capture Only : TCTL3 and TCTL4 - The signal edge to be capture is selected by TCTL3 and TCTL4. - 2 bits per channel : Provides options to capture rising, falling, or both edges. value after reset 6 5 3 2 1 0 7 4 EDG7B EDG7A EDG6B EDG6A EDG5B EDG5A EDG4B EDG4A 0 0 0 0 0 0 0 0 (a) Timer control register 3 (TCTL3) 6 5 3 2 1 0 7 4 EDG3B EDG3A EDG2B EDG2A EDG1B EDG1A EDG0B EDG0A 0 0 0 0 0 0 0 0 (b) Timer control register 4 (TCTL4) EDGnB 0 0 1 1 EDGnA -- Edge configuration 0 : Capture disabled 1 : Capture on rising edges only 0 : Capture on falling edges only 1 : Capture on both edges Figure 8.5 Timer control register 3 and 4 H. Huang Transparency No.8-20 The 68HC12 Microcontroller Example 8.2 Use input capture channel 0 to measure period of an unknown signal. Period known to be shorter than 128 ms. Write a program to set up IC0 to measure period. E clock frequency: 8 MHz. Solution: - Prescale factor = 1: longest period measured is 216 ÷ 8 MHz = 8.192 ms - Prescale factor = 16: longest period measurable is 216 ÷ (8MHz ÷ 16) = 128 ms a. b. c. d. e. f. g. Choose to capture the rising edge Set the prescale factor in TCNT to 16. Enable timer counter Clear COF flag Wait for COF set: first edge arrived. Save the time and clear COF. Wait for the second edge (COF set). Save the time Take the difference between both times H. Huang Transparency No.8-21 The 68HC12 Microcontroller Assembly Program for Period Measurement #include “DP256reg.asm” org edge_1st rmb period rmb $800 2 2 ; Always include the register definition file ; holds the first edge ; stores the period org movb bclr movb $1000 #$90,TSCR TIOS,$01 #$04,TMSK2 movb #$01,TCTL4 bclr brclr ldd std TFLG1,$FE TFLG1,$01,* TC0 edge_1st ; clear C0F flag ; wait for arrival of the first rising edge ; save the first edge and clear C0F flag bclr brclr ldd subd std swi end TFLG1,$FE TFLG1,$01,* TC0 edge_1st period ; clear C0F flag ; wait for the arrival of the second edge ; ; ; ; ; enable timer counter; fast timer flags clear select input capture 0 disable TCNT overflow interrupt, prescale factor = 16. choose to capture the rising edge of PT0 pin H. Huang Transparency No.8-22 The 68HC12 Microcontroller Pulse Accumulator • Purpose: Count number of pulses using independent pulse accumulator (i.e. count register) (PACNT) • HC12DP256: has four 8-bit Pulse Accumulators (PACN3… PACN0) which are also configurable as two 16-bit pulse accumulators (PACA, B) – Text’s Version : Only one 16-bit accumulator • Accumulators programmed to work in either : 1. Event counting mode: counter increments on active edge of PT7 pin. Used to count events. 2. Gated time-accumulation mode: counter clocked by an independent clock signal (E/64) when the PAI signal is active. Used to count duration of a single pulse. Counter = 0 before pulse starts. • If enabled, also provides interrupts – PA overflow and PB overflow interrupts – PA input interrupt H. Huang Transparency No.8-23 The 68HC12 Microcontroller Pulse Accumulator Counter Register 3,2,1,0 (PACN3… PACN0) – 16-bit version is formed by cascading counter registers – PACA = PAC3(high) and PAC2(low) – PACB = PAC1(high) and PAC0(low) Pulse Accumulator Flag Register (PAFLG) - Keep track of the status of the operation of the Pulse Accumulator value after reset 7 6 5 4 3 2 0 0 0 0 0 0 0 0 0 0 0 0 1 0 PAOVF PAIF 0 0 PAOVF -- pulse accumulator overflow flag This flag is set when PACNT overflows from $FFFF to $0000 and can be cleared by writing a 1 to it. PAIF -- PAI pin edge flag When in event counter mode, this bit is set when the selected edge on the PAI pin is detected. When in gated accumulator mode, the selected trailing edge sets this flag. PAIF : Bit is cleared by any write to PAFLG with Bit 0 set. Figure 8.26 Pulse accumulator flag register (PAFLG) H. Huang Transparency No.8-24 The 68HC12 Microcontroller Pulse Accumulator Control Register (PACTL) PAEN — Pulse Accumulator A System Enable PAMOD — Pulse Accumulator Mode Active only when the Pulse Accumulator A is enabled (PAEN = 1). 0 = event counter mode 1 = gated time accumulation mode PEDGE — Pulse Accumulator Edge Control CLK1, CLK0 — Clock Select Bits PAOVI — Pulse Accumulator A Overflow Interrupt enable 0 = interrupt inhibited; 1 = interrupt requested if PAOVF is set PAI— Pulse Accumulator Input Interrupt enable 0 = interrupt inhibited ; 1 = interrupt requested if PAIF is set H. Huang Transparency No.8-25 The 68HC12 Microcontroller Example 8.11 Interrupt after N events. Signal connected to PAI (event = signal edge) Assume N smaller than 65535. Write a program to interrupt the 68HC12 after N events. Solution: Write two’s complement of N into the PACNT (will overflow after N events). Enable overflow interrupt: it will interrupt the CPU after N events. #include ..\dp256reg.asm N equ 3 org $FFDC fdb paov_isr org $4000 lds #$3DFF ldd #N coma comb addd #1 std PACN3 PACA uses PACN3(high) and PACN2(low) movb #$52, PACTL cli bra * paov_isr: movb #$02, PAFLG rti end H. Huang Transparency No.8-26