The Current Sharing Optimisation of Paralleled IGBTs in a Power

advertisement

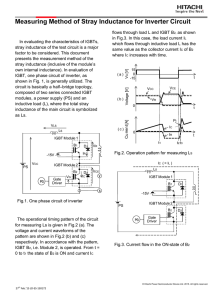

710 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 40, NO. 3, MAY/JUNE 2004 Advanced SPICE Modeling of Large Power IGBT Modules Ramy Azar, Florin Udrea, Mahesh De Silva, Gehan Amaratunga, Wai Tung Ng, Francis Dawson, Member, IEEE, W. Findlay, and Peter Waind Abstract—An enhanced insulated gate bipolar transistor (IGBT) model based on the Kraus model with new derivations based on an extra parameter accounting for p-i-n injection was developed to allow simulation of both trench and DMOS IGBT structures. Temperature dependence was also implemented in the model. The model was validated against steady-state and transient measurements done on an 800-A 1.7-kV Dynex IGBT module at 25 C and 125 C. The Spice model has also shown excellent agreement with mixed mode MEDICI simulations. The Spice model also takes into account for the first time the parasitic thyristor effect allowing the dc and dynamic temperaturedependent latchup modeling of power modules as well as their temperature-dependent safe operating area. Index Terms—Insulated gate bipolar transistor (IGBT) model, PSPICE, trench IGBT simulation. I. INTRODUCTION T HE industry has until now favored the Kraus insulated gate bipolar transistor (IGBT) model for use with SPICE and Saber because it offers an excellent tradeoff between speed and complexity in dc and transient simulations. However, it does not account for temperature dependence or self-heating effects and does not include any temperature-dependent safe operating area (SOA) assessments. It is also limited to DMOS-type IGBTs. There is great industry demand for simulations of large-area IGBTs, and in particular trench IGBTs, but there are few or no available fast and robust SPICE or Saber models for these structures at the present time. An enhanced IGBT model based on the Kraus model [1] with new derivations accounting for p-i-n injection was developed for the simulation of both DMOS and trench structures. Results were validated against measurements on 1.7-kV Dynex Paper IPCSD 03–137, presented at the 2002 Industry Applications Society Annual Meeting, Pittsburgh, PA, October 13–18, and approved for publication in the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS by the Power Electronics Devices and Components Committee of the IEEE Industry Applications Society. Manuscript submitted for review February 1, 2003 and released for publication February 9, 2004. The work of R. Azar was supported by Dynex Semiconductors, U.K., under a full Ph.D. scholarship. The work of F. Udrea was supported by EPSRC Advanced Fellowship AF/100 027. The work of W. T. Ng was supported by CITO, by the Ministry of Energy, Science and Technology of Ontario, and by Dynex Semiconductors, U.K. The work of F. Dawson was supported by Dynex Semiconductors, U.K. R. Azar, F. Udrea, M. De Silva, and G. Amaratunga are with the Department of Engineering, Cambridge University, Cambridge CB2 1PZ, U.K. (e-mail: ramyazar@hotmail.com; fu@eng.cam.ac.uk; dimd@eng.cam.ac.uk). W. T. Ng and F. Dawson are with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON M5S 3G4, Canada (e-mail: ngwt@vrg.utoronto.ca; dawson@ele.power.utoronto.ca). W. Findlay and P. Waind are with Dynex Semiconductors, Lincoln LN6 3LF, U.K. (e-mail: bill_findlay@dynexsemi.com; peter_waind@dynexsemi.com). Digital Object Identifier 10.1109/TIA.2004.827456 Fig. 1. Original Kraus model and charge subcircuit. IGBT modules and MEDICI simulation. The parasitic thyristor effect has also been modeled along with temperature dependence, thereby allowing temperature-dependent SOA simulations in SPICE. II. CHARGE EQUATIONS A. Original Assumption in the Kraus Model Fig. 1 shows the basic IGBT Kraus model and base charge , the emitter elecsubcircuit [1]. The collected hole current , and the variable base resistance are all contron current depends on the trolled by the base charge . The current MOSFET threshold voltage and gain factor which in turn reflect the layout and gate density of the IGBT. controls the injection effiThe reverse saturation current ciency and carrier concentration at the anode end of the base. At the cathode end of the base, the model assumes a zero carrier concentration in the on state [1]. B. Accounting for p-i-n Injection The p-i-n diode effect is defined as the increased carrier concentration near the accumulation region under the gate-to-drain n n layers overlap surface [2]. The p form a p-i-n diode structure, and the carrier recombination near n interface will tend to increase the the n carrier concentration in this area, thereby reducing the overall on-state resistance of the device. It has been shown in [2] that p-i-n injection adds a significant contribution to the current in DMOS structures and is also largely responsible for the lower on-resistance in trench structures due to their large accumulation area. Accounting for p-i-n injection will require making changes in the base charge distribution equation while preserving model simplicity and robustness. Solving the ambipolar diffusion equation for a nonzero carrier concentration at the cathode end and integrating over the base 0093-9994/04$20.00 © 2004 IEEE AZAR et al.: ADVANCED SPICE MODELING OF LARGE POWER IGBT MODULES 711 n junction, it will be assumed rent through the p . that In its current state the boundary condition assumes that all the holes injected at the emitter actually recombine in the accumulation region. It therefore overlooks the bipolar component of the hole current reaching the p-well cathode. Numerical simulations performed in [2] show that the actual carrier concentration profile in the base of an IGBT follows neither the condition used in the PSPICE implementation of the Kraus model nor the boundary condition shown in (4). This is due to the fact that neither the p-i-n diode contribution nor the p-n-p bipolar contribution can be ignored. A onedimensional approximation of the carrier concentration at the cathode end of the base region must, therefore, depend on the relative weighing of both the bipolar transistor contribution and the p-i-n effect, which in turn depends on the aspect ratio and layout of the device. The boundary condition is therefore adjusted by introducing a weighing factor (5) Fig. 2. (a) IGBT structure showing pure p-n-p versus p-i-n diode regions. (b) Pure p-i-n diode versus pure p-n-p base charge concentration profile. width will yield the solution for the steady-state base charge (1) is the ambipolar diffusion length and and are the carrier concentrations at the cathode and anode edges of the base, respectively. Under high injection conditions, the charge neutrality condition at the emmitter–base junction is (2) is the voltage dropped through the junction. Substiwhere tuting this result into the diode current equation allows one to as a function of and . derive is the accumulation layer area and is the total where the p-i-n diode effect cell area. It follows that since is weighted according to the proportion that the accumulation , layer area occupies within the total cell area. Thus, if the carrier distribution reduces to that of the original Kraus the carrier distribution reflects that of model whereas if a pure p-i-n diode. This factor also introduces a dependence of the charge on the design aspect ratio and technology used (DMOS or trench). Substituting this new boundary condition will yield the following result: in (1) and solving for (6) Introducing this change into the Kraus model’s recombination equation [1] and solving for the charge will yield the final solution for the base charge (3) At the cathode end, however, the boundary condition now needs to take into account the increased charge due the p-i-n effect. The boundaries and charge distributions of the p-i-n diode and the thick base p-n-p structure in a non-punchthrough (NPT)-IGBT are shown in Fig. 2. Similarly to the boundary condition at the anode, a new boundary condition at the cathode end of the base region is proposed based on the p-i-n effect, using junction analysis on n junction: the n (4) is the reverse saturation current of the p-i-n diode. where is equal to the reverse curConsidering that in reverse bias (7) where Note that if , then (7) reduces to the standard Kraus model charge expression of (1). Substituting this new charge derivation in the current equations of the original PSPICE Kraus model allows one to simulate the forward and transient characteristics of the IGBT under the new charge conditions derived in (7). 712 Fig. 3. IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 40, NO. 3, MAY/JUNE 2004 IGBT cell cylindrical layout. In more complex two–dimensional (2-D) models such as the p-i-n–p-n-p–MOS model [2], more accurate expressions are . However, since the approximation proposed derived for here allows immediate insertion within the Kraus model, the resulting model benefits from the Kraus model’s robustness and stability in circuit simulators such as PSPICE or Saber while requiring minimum extra computational power. C. Increased Accuracy in Large-Area DMOS IGBTs Fig. 4. Hole recombination rate in cm =s at the cathode end of the IGBT in the on-state for V = 15 V and V = 5 V. The on-state characteristics of a Dynex 1.7-kV 800-A DMOS NPT-IGBT module are plotted using the original Kraus model and the weighted p-i-n charge equations. These are compared to results obtained through numerical MEDICI simulation. The weighing factor is calculated from the cylindrical layout of the IGBT cell as shown in Fig. 3. For the structure in Fig. 3, is equal to 0.8, reflecting a relatively large contribution from the p-i-n effect. This is mainly due to the presence of gate oxide instead of field oxide across the cell surface. The recombination rate in the base is plotted in MEDICI. As can be seen in Fig. 4, the recombination rate decreases in the direction of the cathode. Although a decrease occurs when nearing the p-well, a significant increase is shown in the direction of the Si-SiO interface away from the MOSFET channel and into the accumulation layer area. It can be seen that the recombination rate within the accumulation layer reaches the same order of magnitude as in the base. This demonstrates that the contribution of the hole current recombining within the accumulation region cannot be dismissed if the on state is to be correctly modeled. The MEDICI on-state current is compared to the results obtained using the original Kraus model and the new IGBT model using the charge equations proposed here. Results are shown in Fig. 5. The percentage difference between the Kraus model and the weighted p-i-n model is also plotted as a function of the anode voltage. A maximum 75% difference is reached at lower current V. This is levels and this difference decreases to 40% at to be expected since the p-i-n effect is prominent at low injection levels, when the amount of holes recombining with electrons injected from the accumulation layer is comparable to the fraction of holes reaching the cathode contact. It follows from Fig. 5 that Fig. 5. Drain transfer characteristic for V = 15 V showing the original DMOS Kraus model with = 0 and the proposed model including p-i-n injection with = 0:8. the Kraus model can adequately represent only IGBTs where the p-i-n effect is minimal, such as designs where the gate to drain overlap area is covered with field oxide instead of gate oxide. Optimization of such designs however entails maximizing the accumulation layer area. A model taking into account the p-i-n effect such as the weighted p-i-n model then becomes necessary. This requirement becomes more pronounced when dealing with the basic modeling of any trench structure. D. Accomodating Trench IGBT Structures To illustrate the impact of the p-i-n effect on the on state characteristics, a wide trench structure is examined. The weighing . factor for a typical square layout is calculated as AZAR et al.: ADVANCED SPICE MODELING OF LARGE POWER IGBT MODULES 713 Fig. 6. Drain transfer characteristic for V = 15 V showing the original DMOS Kraus model with = 0 and the proposed model adapted for trench IGBTs with = 0:97. The increased channel density in trench structures is also taken into account in the weighted p-i-n model by including the perimeter to area ratio in the MOSFET gain factor parameter . A comparison of the on-state currents of a DMOS IGBT using the original Kraus model and a trench IGBT using the charge equations proposed here is shown in Fig. 6. The substantial drop in on-resistance with increasing is consistent with the MEDICI results obtained in [2]. III. TEMPERATURE DEPENDENCE The temperature dependence of the injection efficiency, repin the Kraus model (Fig. 1), was resented by the current derived from the ideal diode equation. The temperature dependence of the diffusion length, lifetime, mobility, and intrinsic carrier concentration of silicon has been documented in [5]. The result shows the product of a linear and an exponential temperature component Fig. 7. Drain transfer characteristic of the new model versus the MEDICI results and actual measurements done on a 1.7-kV IGBT module at (a) 25 C and (b) 125 C. IV. LATCHUP MODELING (8) where is the room temperature and and are the room temperature electron mobility and base lifetime, respectively. with increasing temperature. InThis reflects an increase in troducing this in PSPICE allows the simulation of the IGBT at any given temperature. A comparison of this new model and the mixed mode MEDICI model to actual on-state and transient measurements done on an 800-A 1.7-kV Dynex IGBT module at 25 C and 125 C shows very good agreement (Figs. 7 and 8). The turn-off energy predicted by the SPICE model is also in excellent agreement with the energy predicted by MEDICI and the actual measurements. Adding the thermal model of the package in the form of an RC circuit allows one to account for the self-heating effect during dc and transient operation. Adding the modeling of the latch up effect is essential in order to evaluate a product for practical applications. Modifying the Kraus model to include the latchup behavior implies adding the parasitic NPN bipolar transistor to the basic circuit with the emitter connecting to the source of the MOSFET and separated from the base by the source resistance while the collector connects directly to the base. A. Steady-State Latchup The solution proposed here consists in a change of the cathode position, so that it contacts the source of the MOSFET directly, as shown in Fig. 9. The source resistance , originally present in the model to account for imperfections in the MOSFET channel, is now used as the latchup p-well resistance, , the hole current responsible for latchup. thereby isolating 714 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 40, NO. 3, MAY/JUNE 2004 Fig. 8. Measured turn-off characteristic and energy of Dynex 1.7-kV modules versus mixed-mode model and proposed SPICE model at (a) 25 C and (b) 125 C. Fig. 10. (a) DC latchup curves for hypothetical R = 10:58 m . (b) Dynamic latchup showing increase in post-latchup current due to snap-back behavior. thyristor action is modeled by measuring the n-p-n current and feeding it to the charge accumulation subcircuit. B. Dynamic Latchup Fig. 9. (a) Kraus model circuit with added n-p-n BJT and new cathode position. (b) Base charge subcircuit with the added latchup current component. Since is controlled by a current source the pre-latchup characteristics will remain unchanged. After n-p-n turn-on the In the case of transient operation, two main current components contribute to an eventual latchup: • the increase of resulting from an increased when is turned off; the gate current • the displacement current required to deplete the p n junction during turn-off. As can be seen from Fig. 9, the modification in the cathode position also allows both these two contributions to go through during a transient period. C. Latchup Simulation Results can be done in MEDICI by plotExtracting the value of along ting both the hole quasi-fermi potential and the current AZAR et al.: ADVANCED SPICE MODELING OF LARGE POWER IGBT MODULES 715 the p depletion edge. can also be approximated by integrating the silicon resistivity along the current path in the undeturn-on voltage pleted region of the p . The value of the can be calculated from the junction doping levels. Note that found for the Dynex module is less than since the actual , no latchup curves could be simulated or measured. To l50 demonstrate the latchup features of the model in SPICE simulam was used. tions, a higher, hypothetical value of Results for static and dynamic latchup are shown in Fig. 6. The latchup current threshold is found to be constant irrespective of in Fig. 10(a). Latchup at lower gate voltages due to increasing temperature can be simulated by adding the package thermal circuit in SPICE. In Fig. 10(b), since the forward voltage drop decreases below the on-state value as a result of the thyristor effect, the total current increases slightly. Overall, this allows one to analyze and extract the parasitic components of large power IGBT modules to predict accurately their switching behavior. [4] Sigg, Turkes, and Kraus, “Parameter extraction methodology and validation for an electro-thermal physics based NPT IGBT model,” in Conf. Rec. IEEE-IAS Annu. Meeting, vol. 2, 1997, pp. 1166–73. [5] T. Trajkovic, “High voltage trench devices,” Ph.D. dissertation, Dept. Eng., Cambridge Univ., Cambridge, U.K., 2001. [6] Kraus and Hoffmann, “An analytical model of IGBT’s with low emitter efficiency,” in Proc. IEEE Int. Symp. Power Semiconductor Devices, 1993, pp. 30–34. [7] Redig and Kraus, “The influence of the base resistance modulation on switching losses in IGBTs,” in Conf. Rec. IEEE-IAS Annu. Meeting, vol. 3, 1996, pp. 1500–1506. V. CONCLUSION A new IGBT model was proposed. An extra parameter representing the ratio of the accumulation layer area to the active region area was introduced to account for the IGBT aspect ratio and p-i-n effect. The resulting model can accommodate trench structures and allow higher accuracy on DMOS structures. Temperature dependence was introduced in the model. The model was also adapted to include the parasitic thyristor effect, allowing accurate simulations of forward-biased and short-circuit SOAs. Overall, this new model not only benefits from the simplicity, speed, and robustness of the Kraus model, but also incorporates temperature change effects and latchup modeling, a necessary feature for the industrial benchmarking of IGBT modules. Furthermore, it answers the industry’s demand for an easy way to evaluate and/or simulate the on-state, transient, and SOA curves of large power modules such as IGBTs and, in particular, trench IGBTs. ACKNOWLEDGMENT Ramy Azar (S’94) received the B.Eng.Hs. degree in 1997 from McGill University, Montreal, QC, Canada, and the M.Phil. degree in 1999 from Cambridge University, Cambridge, U.K., where he is currently working toward the Ph.D. degree in the Power Semiconductor Devices Group, sponsored by Dynex Semiconductors and in collaboration with the University of Toronto, Toronto, ON, Canada. While originally at Cambridge University, his work focused on the study of silicon carbide (SiC) p-i-n diodes as well as both lateral and trench structures for SiC MOSFETs and IGBTs. In January 1999, he joined Matrox Graphics Inc., where he was responsible for physical reliability issues in ASIC designs such as ESD protection, simultaneous switching I/O (SSO/SSI), RLC extraction, electromigration, and IR Drop in ASIC power grids. His research interests include the coupled electrical and thermal modeling of high-power IGBT devices as well as the electromagnetic modeling of high-power IGBT module packages through parasitic extraction. Florin Udrea (M’90) has been a Lecturer in the Department of Engineering, Cambridge University, Cambridge, U.K., since October 1998. He was an Advanced Engineering and Physical Sciences Research Council (EPSRC) Fellow between August 1998–July 2003 and, prior to this, a College Fellow at Girton College, Cambridge University. He has authored more than 140 papers published in journals and international conference proceedings and is the holder of 18 patents on power semiconductor devices and sensors. He is currently leading a research group in power semiconductor devices and solid-state sensors, which has won during the last ten years an international reputation. He has collaborated with several companies, including Philips, Toshiba, Fuji, GEC, Mitel, Dynex, National Semiconductor, and Denso Corporation. In August 2000, he co-founded Cambridge Semiconductor, a company dedicated to power ICs. The authors acknowledge TMA for the use of the MEDICI software. REFERENCES [1] R. Kraus, P. Türkes, and J. Sigg, “Physics based models of power semiconductor devices for the circuit simulator spice,” in Proc. IEEE PESC’98, vol. 2, 1998, pp. 1726–1731. [2] F. Udrea, “Novel MOS-gated bipolar device concepts toward a new generation of power semiconductor devices,” Ph.D. dissertation, Dept. Eng., Cambridge Univ., Cambridge, U.K., 1995. [3] Kraus and Mattaush, “Status and trends of power semiconductor device models for circuit simulation,” IEEE Trans. Power Electron., vol. 13, pp. 452–65, May 1998. Mahesh De Silva (S’01) received the B.Sc. (Eng.) degree in electronics and telecommunication engineering from the University of Moratuwa, Moratuwa, Sri Lanka, in 1999. He is currently working toward the Ph.D. degree in high-performance IGBTs for resonant power conversion at Cambridge University, Cambridge, U.K. At Cambridge University, he is working with the Electronics, Power and Energy Conversion (EPEC) Group. His main research interests are application-specific power semiconductor device modeling, high-frequency IGBTs, and resonant power converters. 716 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 40, NO. 3, MAY/JUNE 2004 Gehan Amaratunga (M’85) received the B.Sc. degree from Cardiff University, Cardiff, U.K., and the Ph.D. degree from Cambridge University, Cambridge, U.K., both in electrical engineering. He has held the 1966 Professorship in Engineering at Cambridge University since 1998. He currently heads the Electronics, Power and Energy Conversion Group, one of four major research groups within the Electrical Engineering Division of the Cambridge Engineering Faculty. He has worked for 20 years on integrated and discrete electronic devices for power conversion; and on the science and technology of carbon-based electronics for 15 years. His group was among the first to demonstrate integration of logic-level electronics for signal processing and high-voltage power transistors in a single IC (chip). His current research is focused on integrated power conversion circuits and developing a holistic approach to discrete power device design by considering system-level interactions/control. He is a co-founder of Cambrdge Semiconductor—CamSemi—which is commercializing a new generation of power ICs. He also has an active research program on the synthesis and electronic applications of carbon nanotubes. He has previously held faculty positions at the Universities of Liverpool (Chair in Electrical Engineering), Cambridge, and Southampton. He has authored over 300 published journal and conference papers. Prof. Amaratunga held the U.K. Royal Academy of Engineering Overseas Research Award at Stanford University. Wai Tung Ng (M’84) received the B.A.Sc., M.A.Sc., and Ph.D. degrees in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 1983, 1985, and 1990, respectively. His graduate research was focused on analog integrated circuits design and smart-power integrated fabrication processes. In 1990, he joined the Semiconductor Process and Development Center of Texas Instruments Incorporated, Dallas, TX, to work on LDMOS power transistors for automotive applications. His academic career started in 1992 when he joined the Department of Electrical and Electronic Engineering, University of Hong Kong, where his focus was on device models and circuit design. In 1993, he joined the University of Toronto, and was promoted to Associate Professor in 1998. His current work covers a wide spectrum, ranging from advanced MOS and RF BJT device designs, analog circuit techniques, smart-power integrated circuits, and fabrication processes. Francis Dawson (S’86–M’87) received the B.Sc. degree in physics and the B.A.Sc., M.A.Sc., and Ph.D. degrees in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 1978, 1982, 1985, and 1988, respectively. He was a Process Control Engineer in the pulp and paper, rubber, and textile industries during the period 1978–1980. From 1982 to 1984, he acted as a Consultant on various projects. Development areas included high-frequency link power supplies, power supplies for specialized applications, and high-current protection circuits. Since 1988, he has been with the Department of Electrical and Computer Engineering, University of Toronto, where he is engaged in teaching and research. His areas of research interest include static power converters and their applications, signal processing in power engineering applications, and device or process modeling. He has also participated as a Consultant or Project Leader in several industrial projects. Dr. Dawson is a member of the Association of Professional Engineers of Ontario, Canada. W. (Bill) Findlay was born in the U.K. in 1959. He received the B.Sc. degree in applied physics and electronics from Durham University, Durham, U.K., in 1980. He joined AEI Semiconductors (now Dynex Semiconductors), Lincoln, U.K., in 1980, where he was responsible for the design and development of a variety of power semiconductor devices. Areas of expertise include thyristors, GTOs, and IGBT modules, with a particular interest in application specific designs. Currently, he is responsible for high-power IGBT module design and development. Mr. Findlay is a Chartered Engineer in the U.K. and a Member of the Institution of Electrical Engineers, U.K. Peter Waind was born in the U,K. in 1956. He received the B.Sc. degree in physics and the Ph.D. degree in solid-state physics from the University of Manchester, Manchester, U.K., in 1977 and 1981, respectively. He joined Ferranti Electronics in 1982 and, in 1985, he moved to Marconi Electronic Devices (now Dynex Semiconductors), Lincoln, U.K., where he has been responsible for the design and development of a variety of power semiconductor devices. Areas of experience include thyristors, bipolar transistors, MOSFETs, IGBTs, and fast-recovery diodes. Most recently, he has led the trench gate IGBT development activities at Dynex Semiconductors. He is currently responsible for overall MOS device design and process development.