CHAPTER 7 FIELD EFFECT TRANSISTORS

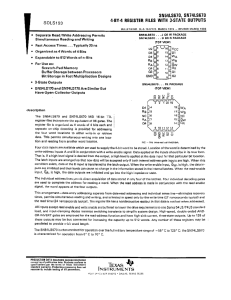

advertisement

CHAPTER 7 FIELD EFFECT TRANSISTORS © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 1 Outline © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 2 Transistors Vacuum tubes, invented by Fleming in 1905 and further developed by Lieben (1906) and by De Forest (1907) used for rectification, amplification, switching and otherwise modification and creation of electrical signal for many years. Invention of bipolar transistor in 1947 started the solid state electronics era. Demonstration of MOSFET in 1960 revolutionized electronics industry. Today MOSFET is the most abundant man made device on Earth. (107 – 108 MOSFETs per person in Western World.) RCA Vacuum tube 1940s First transistor (Bardeen et al. 1947) © Nezih Pala npala@fiu.edu First MOSFET (Kahng and Attala, 1960) EEE 6397 – Semiconductor Device Theory Transistors 2000s 3 Transistor operation -1 Load line for two-terminal devices: Consider a circuit containing a two terminal device with given I-V characteristics. Using KVL E iD R vD One equation with two unknowns (iD, vD). With known iD-vD dependence, the equation can be solved graphically. Two graphs cross at vD=VD and iD=ID, the steady state values of current van volatage for device with this biasing circuit. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 4 Transistor operation -2 Load line for three-terminal devices: Now a third terminal which controls the I-V characteristics. E iD R vD Similar to the two-terminal case, the current ID corresponding to the voltage VD can be found for any specific control voltage vG. The property of controlling I-V characteristics by a voltage vG can be used for amplification and switching. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 5 The junction FET (JFET) Voltage-variable depletion region width of p-n junction is used to control the effective cross sectional area of the channel and thereby the current flowing between source and drain. The width of the depletion region can be controlled by the voltage applied to the gate electrodes. The voltage in the channel increases linearly from 0 at the source to VD at the drain. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 6 JFET Biasing conditions -1 Linear region For small currents, voltage drop throughout the channel is small and the depletion region width is close to the equilibrium value. When VG=VS=0 Onset of saturation By increasing current, the voltage difference between the gate and channel increases . Increasing reverse voltage widens the depletion region. Pinch off and Saturation When the total depletion width becomes equal to the channel width, the channel is pinched-off, current saturates and does not increase with increasing drain bias. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 7 JFET Biasing conditions -2 When VG ≠0 When a negative gate bias –VG is applied, the effective channel width becomes smaller and the channel resistance becomes larger. For the same reason, pinch-off condition is reached at lower drain bias. Beyond the saturation voltage VD, the current is constant depending on the gate bias VG. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 8 JFET Pinch off -1 The pinch-off voltage can be calculated by assuming the channel is symmetric and depletion width decreases symmetrically with increasing potential difference between the gate and the channel. Remember the eqn for the depletion region: 2 (V0 V ) N a N d W ( x) q Na Nd 1/ 2 At x=L, applied voltage V=VGD=VG-VD. Equilibrium contact potential V0 can be neglected compared to VGD. And Na >> Nd for p+-n junction. Hence 2 (VGD ) W ( x L) qN d © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 1/ 2 9 JFET Pinch off -2 Pinch-off occurs when W ( x L) a 2 (VGD ) W ( x L) qN d 1/ 2 a If we define the value of –VGD at pinch off as VP: qa 2 N d VP 2 The pinch off voltage is a positive number and VP VGD (pinch - off) VG VD where VG is zero or negative for proper device operation. Q: What happens if VG is positive? © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 10 JFET Current-voltage characteristics -1 The current can be calculated for sub-pinch off region. Assume: ρ=resistivity of n channel Z=channel depth 2h(x)=channel width at x Differential volume of the neutral channel: Z 2h( x)dx and the resistance of this volume element: dx / Z 2h( x) The current ID is related to the differential voltage change in the element: Z 2h( x) dVx ID dx © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 11 JFET Current-voltage characteristics -2 2 (VGx ) h( x ) a W ( x ) a qN d 1/ 2 Using VGx=VG-Vx and VP=qa2Nd/2є V V 1/ 2 h( x) a 1 x G VP The last expression implicitly assumes the gradual channel approximation where h(x) does not change abruptly in the channel. The voltage VGx will be negative since the gate voltage VG chosen zero or negative for proper operation. Hence by substituting h(x) into ID in the previous page: Z 2h( x) dVx ID dx 1/ 2 Vx VG 2aZ dV x 1 I D dx VP © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 12 JFET Current-voltage characteristics -3 Taking the integral of both sides: Which gives 3 / 2 Vd 2aZ VD 2 Vx VG L IDx 0 V x 0 VP 3 VP 0 3/ 2 xg 2 xg dx p p 3 p 3/ 2 3/ 2 2aZ VD 2 VG 2 VD VG ID VP L VP 3 VP 3 VP where VG is negative and 2aZ G0 L is the conductance of the channel for negligible W(x), i.e. with no gate voltage and low values of ID. The last equation for ID is valid only up to the pinch off where VP=VD - VG © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 13 JFET Saturation current Remember: We assumed that the current remains constant above pinch off Inserting VD – VG = VP into the last equation, ID at saturation can be found: 3/ 2 VG 2 VG 2aZ 1 I D ( sat ) VP L VP 3 VP 3 Saturation current can also be modeled by a simple semi-empirical model: VG I D ( sat ) I DSS 1 VP © Nezih Pala npala@fiu.edu 2 where IDSS is the saturation current at VG=0 EEE 6397 – Semiconductor Device Theory 14 JFET Transconductance In FETs the output current (ID) can be related to the input voltage VG through (mutual) transconductance. I D gm VG VD with units (A/V) called Siemens (S). As a figure of merit for FETs it is usually normalized as gm/Z and given in units of millisiemens per millimeter. at saturation I D ( sat ) g m ( sat ) VG V © Nezih Pala npala@fiu.edu D 1/ 2 VG 2aZ 1 L VP EEE 6397 – Semiconductor Device Theory 15 Example An n-channel Si JFET is to be constructed with a channel doping of ND=1016cm-3 and gate doping of NA=5x1019 cm-3. Assuming room temperature operation, determine the maximum junction-to-junction half width (a) that can be employed in constructing the JFET. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 16 Let WBR be the depletion width when the pn junctions in the JFET are biased to the breakdown voltage. For the JFET to exhibit saturating characteristics, we must have a << WBR. As read from the figure in the previous slide VBR= 55 V for the given ND=1016 cm-3 p-n junctions. kT N a N d V0 ln 2 q ni amax 2 Si 0 WBR (V0 VBR qN d 2.7 m © Nezih Pala npala@fiu.edu 1/ 2 1016 5 1019 0.92V 0.026 ln 1.5 1010 2 2 11.8 8.85 10 14 (0.92 55) 19 16 1.6 10 10 EEE 6397 – Semiconductor Device Theory 1/ 2 17 Metal-semiconductor FET (MESFET) -1 Figure shows schematically a simple MESFET in GaAs. The substrate is undoped or doped with chromium, which has an energy level near the center of the GaAs band gap. In either case the Fermi level is near the center of the gap, resulting in very high resistivity material (~108 .cm), generally called semi-insulating GaAs. On this nonconducting substrate a thin layer of lightly-doped n-type GaAs is grown epitaxially, to form the channel region of the FET. The photolithographic processing consists of defining pattern in the metal layers for source and drain ohmic contacts (e.g., Au-Ge) and for the Schottky barrier gate (e.g., AI). By reverse biasing the Schottky gate, the channel can be depleted to the semi-insulating substrate, and the resulting I-V characteristics are similar to the JFET device. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 18 Metal-semiconductor FET (MESFET) -2 Gate Drain Source n+ layer S.I. GaAs Self aligned GaAs MESFET Eg (eV) n (cm2/Vs) p (cm2/Vs) Si 1.1 1350 480 GaAs 1.4 8500 400 By using GaAs instead of Si, a higher electron mobility is available, and furthermore GaAs can be operated at higher temperatures (and therefore higher power levels). Since no diffusions are involved, close geometrical tolerances can be achieved and the MESFET can be made very small. Gate lengths L 0.25 m are common in these devices. This is important at high frequencies, since drift time and capacitances must be kept to a minimum. It is possible to avoid the epitaxial growth of the n-type layer and the etched isolation by using ion implantation. Starting with a semiinsulating GaAs substrate, a thin n-type layer at the surface of each transistor region can be formed by implanting Si or a column VI donor impurity such as Se. This implantation requires an anneal to remove the radiation damage. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 19 High Electron Mobility Transistor (HEMT) HEMTs exploit the band gap engineering available with heterojunctions in group III-V semiconductors. High transconductance can be achieved by high channel conductance. high channel conductance high channel doping increased scattering (degradation of mobility) Solution: Physical separation of donors from the electron channel! © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 20 High Electron Mobility Transistor (HEMT) When a thin undoped well (e.g., GaAs) bounded by wider band gap, doped barriers (e.g., AlGaAs).This configuration, called modulation doping, results in conductive GaAs when electrons from the doped AlGaAs barriers fall into the well and become trapped there. Since the donors are in the AlGaAs rather than the GaAs, there is no impurity scattering of electrons in the well. We can take advantage of this reduced scattering and resulting higher mobility. This device is called a modulation doped field-effect transistor (MODFET) and is also called a high electron mobility transistor (HEMT). © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 21 Metal-Insulator-Semiconductor FET (MISFET) One of the most widely used electronic devices, particularly in digital integrated circuits, is the metal-insulator-semiconductor (MIS) transistor. In this device the channel current is controlled by a voltage applied at a gate electrode that is isolated from the channel by an insulator. The resulting device may be referred to generically as an insulated-gate field-effect transistor (IGFET). However, since most such devices are made using silicon for the semiconductor, SiO2 for the insulator, and metal or heavily doped polysilicon for the gate electrode, the term MOS field-effect transistor (MOSFET) is commonly used. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 22 History of Transistors Vacuum Tubes BJTs MOSFET Now •Spintronics •Bio Sensors •Displays …. 1906-1950s 1947-1980s 1960 – until now This circuit board block is one of hundreds of blocks that held the 4000 vacuum tubes for IBM's Model 701, it's first computer intended for scientific work. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 23 Basic Configuration of a MOSFET Almost like a lateral bipolar transistor! © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 24 Metal-Oxide-Semiconductor FET (MOSFET) -1 The figure shows a basic MOS transistor for the case of an enhancement-mode n-channel device formed on a p-type Si substrate. The n+ source and drain regions are diffused or implanted into a relatively lightly doped p-type substrate, and a thin oxide layer separates the conducting gate from the Si surface. No current flows from drain to source without a conducting n channel between them. The Fermi level is flat in equilibrium. The conduction band is close to the Fermi level in the n+ source/drain, while the valence band is closer to the Fermi level in the p-type material. Hence, there is a potential barrier for an electron to go from the source to the drain, corresponding to the built-in potential of the back-to-back p-n junctions between the source and drain. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 25 Metal-Oxide-Semiconductor FET (MOSFET) -2 When a positive voltage is applied to the gate relative to the substrate (which is connected to the source in this case), positive charges are in effect deposited on the gate metal. In response, negative charges are induced in the underlying Si, by the formation of a depletion region and a thin surface region containing mobile electrons. These induced electrons form the channel of the FET, and allow current to flow from drain to source. Since electrons are electrostatically induced in the p-type channel region, the channel becomes less p-type, and therefore the valence band moves down, farther away from the Fermi level. This obviously reduces the barrier for electrons between the source, the channel, and the drain. If the barrier is reduced sufficiently by applying a gate voltage in excess of what is known as the threshold voltage, VT, there is significant current flow from the source to the drain. This is gate-controlled potential barrier view for MOSFET. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 26 Metal-Oxide-Semiconductor FET (MOSFET) -3 The threshold voltage VT is the minimum gate voltage required to induce the channel. Some n-channel devices have a channel already with zero gate voltage, and in fact a negative gate voltage is required to turn the device off. Such a "normally on" device is called a depletion-mode transistor, since gate voltage is used to deplete a channel which exists at equilibrium. The more common MOS transistor is "normally off" with zero gate voltage, and operates in the enhancement mode by applying gate voltage large enough to induce a conducting channel. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 27 Metal-Oxide-Semiconductor FET (MOSFET) -4 © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 28 Metal-Oxide-Semiconductor FET (MOSFET) -5 VG>VT VD<(VG –VT) An alternative view of a MOSFET is that it is a gatecontrolled resistor. Since this channel is connected to the n+ source and drain regions, the structure looks electrically like an induced n-type resistor. As the gate voltage increases, more electron charge is induced in the channel and, therefore, the channel becomes more conducting. The voltage difference between the gate and the channel reduces from VG near the source to (VG-VD) near the drain end as more drain current flows in the channel. VG>VT VD=(VG –VT) Once the drain bias is increased to the point that (VG -VD) = VT, threshold is barely maintained near the drain end, and the channel is said to be pinched off. Increasing the drain bias beyond this point (VD (sat.)) causes the device to enter the saturation region because ID does not increase with drain bias significantly. VG>VT VD>(VG –VT) © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 29 Ideal MOS Capacitor -1 © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 30 Ideal MOS Capacitor -2 q m: Modified work function measured from the metal Fermi level to the conduction band of the oxide q s: Modified work function at the semiconductor-oxide interface. qF: Position of the Fermi level below the intrinsic level Ei for the semiconductor. This quantity indicates how strongly p-type the semiconductor is. In this idealized case we assume that qm= qs, so there is no difference in the two work functions. The MOS structure of is essentially a capacitor in which one plate is a semiconductor. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 31 Ideal MOS Capacitor -3 (Accumulation) When a negative voltage is applied between the metal and the semiconductor, effectively a negative charge is deposited on the metal. In response, an equal net positive charge accumulates at the surface of the semiconductor. In the case of a p-type substrate this occurs by hole accumulation at the semiconductor-oxide interface. Since the applied negative voltage depresses the electrostatic potential of the metal relative to the semiconductor, the electron energies are raised in the metal relative to the semiconductor. As a result, the Fermi level for the metal EFm lies above its equilibrium position by qV, where V is the applied voltage. Since m and S do not change with applied voltage, moving EFm up in energy relative to EFs causes a tilt in the oxide conduction band. We expect such a tilt since an electric field causes a gradient in Ei (and similarly in EV and EC) as ( x) 1 dEi q dx © Nezih Pala npala@fiu.edu Which leads increase in hole concentration EEE 6397 – Semiconductor Device Theory E EF p ni exp i kT 32 Ideal MOS Capacitor -4 (Depletion) When a positive voltage is applied from the metal to the semiconductor. This raises the potential of the metal, lowering the metal Fermi level by qV relative to its equilibrium position. As a result, the oxide conduction band is again tilted. We notice that the slope of this band, obtained by simply moving the metal side down relative to the semiconductor side, is in the proper direction for the applied field. The positive voltage deposits positive charge on the metal and calls for a corresponding net negative charge at the surface of the semiconductor. Such a negative charge in p-type material arises from depletion of holes from the region near the surface, leaving behind uncompensated ionized acceptors. This is analogous to the depletion region at a p-n junction discussed earlier. In the depleted region the hole concentration decreases, moving Ei closer to EF, and bending the bands down near the semiconductor surface. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 33 Ideal MOS Capacitor -4 (Inversion) If we continue to increase the positive voltage, the bands at the semiconductor surface bend down more strongly. In fact, a sufficiently large voltage can bend Ei below EF. This is a particularly interesting case, since EF >> Ei implies a large electron concentration in the conduction band. The region near the semiconductor surface in this case has conduction properties typical of ntype material, with an electron concentration given by E Ei n ni exp F kT This n-type surface layer is formed not by doping, but instead by inversion of the originally ptype semiconductor due to the applied voltage. This inverted layer, separated from the underlying p-type material by a depletion region, is the key to MOS transistor operation. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 34 Ideal MOS Capacitor -5 Potential is defined at any point x, measured relative to the equilibrium position of Ei. The energy q tells us the extent of band-bending at x, and qS represents the band-bending at the surface. 1 F Ei BULK EF q 1 S Ei BULK Ei SURFACE q © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 35 Ideal MOS Capacitor -5 We notice that qS = 0 is the flat band condition for this ideal MOS case. When S < 0, the bands bend up at the surface, and we have hole accumulation. Similarly, when S > 0, we have depletion. Finally, when S is positive and larger than F, the bands at the surface are bent down such that Ei(x= 0) lies below EF, and inversion is obtained. 1 F Ei BULK EF q Flat band S = 0 © Nezih Pala npala@fiu.edu 1 S Ei BULK Ei SURFACE q Accumulation S < 0 Depletion S > 0 EEE 6397 – Semiconductor Device Theory Inversion S > F 36 Ideal MOS Capacitor -6 The best criterion for strong inversion is that the surface should be as strongly n-type as the substrate is p-type. That is, Ei should lie as far below EF at the surface as it is above EF far from the surface. This condition occurs when kT N a S (inv.) 2F 2 ln q ni A surface potential of F is required to bend the bands down to the intrinsic condition at the surface (Ei = EF), and Ei must then be depressed another qF at the surface to obtain the condition we call strong inversion. Equilibrium electron concentration related to the potential is n0 ni e EF Ei kT ni e qF kT We can easily obtain the electron and hole concentrations at any x q F kT qF q kT n ni e © Nezih Pala npala@fiu.edu n0e p0 ni e EEE 6397 – Semiconductor Device Theory kT p p0e q kT 37 Ideal MOS Capacitor -7 Using Poisson's equation and the usual charge density expression to solve for (x): 2 ( x) 2 x S ( x) q( N d N a p n) Let us solve this equation to determine the total integrated charge per unit area, QS, as a function of the surface potential, S 2 q x 2 x x S It should be kept in mind that q q kT kT p0 e 1 n0 e 1 x is the electric field at a depth x Integrating from the bulk (where the bands are flat, the electric fields are zero, and the carrier concentrations are determined solely by the doping), towards the surface, we get x 0 © Nezih Pala npala@fiu.edu q d S x x 0 q q kT kT p0 e 1 n0 e 1d EEE 6397 – Semiconductor Device Theory 38 Ideal MOS Capacitor -8 After integration, q q 2 kTp n q q 2 0 0 kT kT e 1 e 1 kT p0 kT S at the surface (x = 0) where the surface perpendicular electric field, s, becomes 2kT e S qLD q S kT n0 qS 1 e kT p0 qS kT qS 1 kT 1 2 where we have introduced a new term, the Debye screening length LD S kT q 2 p0 The Debye length gives an idea of the distance scale in which charge imbalances are screened or smeared out. For example, if we think of inserting a positively charged sphere in an n-type semiconductor we know that the mobile electrons will crowd around the sphere. If we move away from the sphere by several Debye lengths, the positively charged sphere and the negative electron cloud will look like a neutral entity. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 39 Ideal MOS Capacitor -9 By using Gauss's law at the surface, we can relate the integrated space charge per unit area to the electric displacement, keeping in mind that the electric field or displacement deep in the substrate is zero. QS S S which gives QS s qS qS q n q 2kT S 0 S e kT e kT 1 1 p qLD kT kT 0 2kT 2qkTS e QS s qL D S < 0 accumulation 2kT qS QS s 1 qLD kT © Nezih Pala npala@fiu.edu 2kT 2qkTS e QS s qL D 1 2 S EEE 6397 – Semiconductor Device Theory 1 2 S >>0 strong inversion S >>0 depletion and weak inversion 40 Ideal MOS Capacitor -9 1. S = 0 (flat band condition) The net space charge is zero. This is because the fixed dopant charges are cancelled by the mobile carrier charges at flat band. 2. S < 0 it attracts and forms an accumulation layer of the majority carrier holes at the surface. Accumulation space charge increases very strongly (exponentially) with negative surface potential. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 41 Ideal MOS Capacitor -10 3. S > 0 initially the second (linear) term is the dominant one. At some point, the band-bending is twice the Fermi potential (j>F, which is enough for the onset of strong inversion. Hence, for band bending beyond this point, it becomes the dominant term. As in the case of accumulation, the mobile inversion charge now increases very strongly with bias. The typical inversion layer thicknesses are ~5 nm, and the surface potential now is essentially pinned at 2F. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 42 Ideal MOS Capacitor -11 Charge distribution, for the inverted surface can be sketched by using the depletion approximation and assuming complete depletion for 0 < x < W, and neutral material for x > W. In this approximation the charge per unit area due to uncompensated acceptors in the depletion region is qNaW. The positive charge Qm on the metal is balanced by the negative charge QS in the semiconductor, which is the depletion layer charge plus the inversion region charge Qn: Qm QS qN aW Qn the width of the inversion region is generally less than 100 A. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 43 Ideal MOS Capacitor -12 The width of the inversion region is neglected in sketching the potential distribution. In the potential distribution diagram we see that an applied voltage V appears partially across the insulator (Vi) and partially across the depletion region of the semiconductor (S): V Vi S The voltage across the insulator is obviously related to the charge on either side, divided by the capacitance: Vi QS d QS i Ci where i is permittivity of the insulator and Ci, is the insulator capacitance per unit area. The charge QS will be negative for the n channel, giving a positive Vi. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 44 Ideal MOS Capacitor -13 Using the depletion approximation, W as a function of S can be obtained similar to n+-p junction, for which the depletion region extends almost entirely into the p region: 2 W S S qN a 12 This depletion region grows with increased voltage across the capacitor until strong inversion is reached. After that, further increases in voltage result in stronger inversion rather than in more depletion. Thus the maximum value of the depletion width is 2 (inv ) Wm S S qN a 12 kT ln( N a / ni ) 2 S 2 q N a 12 Hence, the charge per unit area in the depletion region Qd at strong inversion is Qd qN aWm 2(S qN aF )1 2 © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 45 Ideal MOS Capacitor -14 The applied voltage must be large enough to create this depletion charge plus the surface potential S(inv.).The threshold voltage required for strong inversion is Qd VT 2F Ci (Ideal case) This assumes the negative charge at the semiconductor surface QS at inversion is mostly due to the depletion charge Qd. However other terms must be added to this expression for real MOS structures. Considering that the capacitance for MOSFETs is voltage dependent, the voltagedependent semiconductor capacitance dQ dQS CS dV dS MOS capacitor is the series combination of a fixed, voltage-independent gate oxide (insulator) capacitance, and a voltage-dependent semiconductor capacitance such that the overall MOS capacitance becomes voltage dependent. The semiconductor capacitance itself can be determined from the slope of the QS versus S plot. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 46 Ideal MOS Capacitor -15 Capacitance in accumulation is very high because the slope is so steep; i.e., the accumulation charge changes a lot with surface potential. The series capacitance in accumulation is basically the insulator capacitance (point 1), Ci=i/d As the voltage becomes less negative, the semiconductor surface is depleted. Thus a depletion-layer capacitance Cd is added in series with Ci. Ci S W Where s is the semiconductor permittivity and W is the width of the depletion layer. The total capacitance is © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory C Ci Cd Ci Cd 47 Ideal MOS Capacitor -16 The capacitance decreases as W grows from flatband (point 2), past weak inversion (point 3), until finally strong inversion is reached at VT (point 4). In the depletion region, the small signal semiconductor capacitance is given by the equation dQS/dS which gives the variation of the (depletion) space charge with surface potential. Since the charge increases as ~ S, the depletion capacitance will obviously decrease as 1/ S, exactly as for the depletion capacitance of a p-n junction. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 48 Ideal MOS Capacitor -17 After inversion is reached, the small signal capacitance depends on whether the measurements are made at high (typically ~1 MHz) or low (typically -1-100 Hz) frequency, where "high" and "low" are with respect to the generation-recombination rate of the minority carriers in the inversion layer. If the gate voltage is varied rapidly, the charge in the inversion layer cannot change in response, and thus does not contribute to the small signal a-c capacitance. Hence, the semiconductor capacitance is at a minimum, corresponding to a maximum depletion width. © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 49 Ideal MOS Capacitor -18 On the other hand, if the gate bias is changed slowly, there is time for minority carriers to be generated in the bulk, drift across the depletion region to the inversion layer, or go back to the substrate and recombine. Now, the semiconductor capacitance, using the same equation (dQS/dS ), is very large because we saw that the inversion charge increases exponentially with S Hence, the low frequency MOS series capacitance in strong inversion is basically Ci once again (point 5). © Nezih Pala npala@fiu.edu EEE 6397 – Semiconductor Device Theory 50 Example Construct line plots (with S plotted along the x-axis) that visually identify the voltage ranges corresponding to accumulation, depletion, and inversion in ideal n-type and p-type MOS devices. The “plots” shown below are in essence a graphical representation of the word summary given at the end of the preceding section. Note that acc, depl, and inv are standard abbreviations for accumulation, depletion, and inversion, respectively. INV DEPL ACC VT ACC DEPL 0 © Nezih Pala npala@fiu.edu INV VT EEE 6397 – Semiconductor Device Theory VG n-type VG p-type 51 Example Construct line plots (with plotted along the x-axes) that visually identify the surface potential ranges corresponding to accumulation, depletion, and inversion in ideal n-type and p-type MOS devices. Converting the discussion at the and of the preceding subsection into a graphical representation yields INV DEPL ACC S F <0 n-type S F >0 p-type 2F ACC DEPL 0 © Nezih Pala npala@fiu.edu INV 2F EEE 6397 – Semiconductor Device Theory 52 Example For each of the F and S parameter sets listed below, indicate the doping type and the specified biasing condition. Also draw the corresponding energy band diagram and block charge diagram that characterize the static state of the ideal MOS system i) iii ) v) F kT / q F kT / q F kT / q 12, 9, 15, © Nezih Pala npala@fiu.edu S kT / q 12 S kT / q S kT / q 18 ii ) iv ) F kT / q F kT / q 9, 15, S kT / q S kT / q 3 36 0 EEE 6397 – Semiconductor Device Theory 53 1 F Ei BULK EF q i) ii ) iii ) F kT / q 12, F kT / q F kT / q S kT / q 9, 12 S 9, kT / q S kT / q © Nezih Pala npala@fiu.edu 1 S Ei BULK Ei SURFACE q 3 18 EEE 6397 – Semiconductor Device Theory 54 1 F Ei BULK EF q iv ) v) F kT / q F kT / q 15, S kT / q 15, © Nezih Pala npala@fiu.edu S kT / q 1 S Ei BULK Ei SURFACE q 36 0 EEE 6397 – Semiconductor Device Theory 55