Design and comparison of CMOS current mode logic latches

advertisement

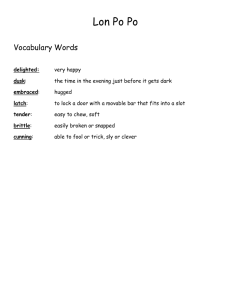

DESIGN AND COMPARISON OF CMOS CURRENT MODE LOGIC LATCHES Muhammad Usama and Tad Kwasniewski Department of Electronics, Carleton University, 1125 Colonel By Drive, Ottawa, Ontario, K1S 5B6 Canada. ABSTRACT A comprehensive study of the MOS Current Mode Logic (MCML) is presented. Operation of a conventional MCML latch is analyzed and some modified structures are described. A novel structure is proposed for increased stability with reduced delay parameters. General problems with single-ended to differential conversion are addressed. Comparative performance measures of Master-Slave (MS) latches are presented in a 0.18-µm CMOS technology. RL Out 2. MCML CIRCUITS MCML in general consists of three main components, as shown in Fig. 1, which include the pull-up load, the pull-down network (PDN) and a constant current source [4]. MCML is a completely differential logic, i.e. all signals and their complements are required. Depending on the logic implemented by PDN, all the current flows through one of the two branches, providing complementary output signals. Voltage at the output of branch with no current reaches VDD, whereas for the other branch some voltage drops across the load resistor and the output voltage ;,((( Out I Pull n p Down u t Network (s) 1. INTRODUCTION High-speed latches and flip-flops (FF) are considered the core of high-speed communication transceivers. They are an integral part of digital design, especially used for data sampling and clock deskew applications. Over the decades various different structures have been proposed for high-speed latch and flip-flop designs, including static, dynamic, single phase, multiphase, clocked CMOS, transmission gate, etc. For last few years designers’ interest in Current Mode Logic increases due to its superior performance at very high frequencies as compared to other logic styles. CML latch was first introduced in [4] and some modified latches are found in literature [2][3]. The MCML lathes exhibit better performance than other latch structures. A fair comparison between various latch/FF design structures requires each structure to be fully optimized and evaluated under consistent simulation conditions. This paper presents the design and comparison of some MCML latches. Section-2 briefly describes the operation of general MCML circuits. In section-3 important latch timing parameters are explained. Saection-4 covers the review of MCML latches and a modified latch design is presented. General issues in single ended to differential conversion are addressed in section-5. Simulation results in 0.18 µm CMOS technology are presented. RL I n p u t (s) Ibias Fig. 1: General MCML Structure becomes VDD – IbiasRL. MCML does not provide a rail-to-rail output swing. Due to the reduced swing, it has smaller dynamic power dissipation. MCML circuits are faster than other logic families, because it uses NMOS transistors only. Due to its differential nature, it is highly immune to common mode noise. It has almost flat power curve over a wide range of frequency as opposed to other logic styles where power consumption increases directly with frequency. Therefore at very high frequencies its power consumption is comparable or lower than other logic styles. This makes it a good choice for high speed and low power integrated circuit design. 3. MS-LATCH/FF TIMING PARAMETERS For designers, a thorough understanding of latch timing parameters, like setup time, hold time, Clk – Q delay, etc. is essential for reliable operation and speed optimization. For clarification the parameters are stated below. Setup time is defined as the minimum time before the clock edge by which the data should be stable in order to be captured as the next state. It should be noted that satisfying this condition does not necessarily mean that the output will change accordingly. Hold Time is defined as the minimum time after the clock edge until which the data must be in the same state. For successful and reliable operation both conditions must be satisfied. These times define a sampling window, in which the data is captured as next state. Any data change in that window will result in failure of the latch operation. The minimum width of the data pulse is, therefore, the sum of setup and hold time. ,9 Authorized licensed use limited to: Carleton University. Downloaded on July 13, 2009 at 14:26 from IEEE Xplore. Restrictions apply. ,6&$6 Metastable Region 72 Stable Region 65 Failure Region Hold Time [ps] RL RL Q Q D 58 D Clk Clk 32 40 46 50 Ibias DŦClk Delay [ps] Fig. 2: Hold Time for MCML Latch Fig. 3: Conventional MCML Latch Measurement of setup and hold time for comparison is not trivial, because the hold time depends on the time the data changes before the clock edge, i.e. the D-Clk delay, as shown in Fig. 2. If the change in data occurs sufficiently prior to the clock edge, the hold time is constant and does not depend on D-Clk delay. This is known as the stable region. As D-Clk delay decreases, at a certain point the hold time starts to rise exponentially. This region is called the metastable region. As the D-Clk delay further decreases, setup time violation occurs. Any change in data after this cannot be transferred to the output. This is known as the failure region. Another important parameter is Clk-Q delay, which is the time between triggering edge of clock and the change in the output (Q), provided that the data changes before the minimum setup time. This follows the same trend as hold time shown in Fig. 2. In the metastable region, as described in reference [1], the D-Q delay reaches its minimum value which is smaller than setup + Clk-Q delay in the stable region. Obviously the cycle time will be reduced if the data changes near this point. Therefore the minimum D-Q delay is the only true measure of the performance of a master-slave latch or flip-flop. RL Q RL RL RL Q D D Vref Clk Clk Iss1 Iss2 Fig. 4: MCML Latch with distinct Tail Currents [2] Q Q D D 4. MCML LATCH 4.1. Conventional MCML Latch A current mode logic latch consists of a sample and a hold stage. A set of transistors is used to sense and track the input data. Whereas the other set of cross-coupled transistors is used to store that data. As shown in the Fig. 3 the differential pairs formed by the transistors are switched by the complementary signals of the clock. When Clk is high, all the current passes through the tracking pair. And when Clk is low, all the current passes through the storage pair. The tracking pair works as a CML inverter, driven by complementary data signals. When data is high all the current passes through one branch, as a result the voltage at the drain of that transistor drops to a low voltage level (VDD – IbiasRL). As the other transistor is in cut off and no current is flowing through it, the voltage at the drain of that transistor becomes high (VDD). When Clk goes low, the hold pair is activated. The cross coupled transistors form a regenerative positive feedback structure and keep the output in the same state. In the stable region the propagation delay (D-Q) is a function of the total output capacitance and load resistance, TDQ = CTOT RL. Near the clock edge the D-Q delay changes due to finite current transition time and causes metastability in the output. Clk Clk Ibias Fig. 5: Feedback MCML Latch [3] 4.2. Other Modified Latches Some modified latch structures are found in the literature for improved performance. In reference [2], the regenerative latch is modified so that the sample circuit and the hold circuit use two distinct tail currents, shown in Fig. 4. Because of the parasitic capacitance of transistors of sample circuit, the tail current must be sufficiently high to achieve a wider range of linearity and a larger transconductance. On the other hand the hold circuit do not need a large bias current. This technique shows significant improvement. However this increases the static power consumption and circuit complexity. The maximum operation frequency of MCML is reduced by the variation of the threshold voltage. A feedback MCML D-Latch has been proposed in [3] ,9 Authorized licensed use limited to: Carleton University. Downloaded on July 13, 2009 at 14:26 from IEEE Xplore. Restrictions apply. (a) RL RL + CML Output Q Q CMOS Input D D CMOS Inverter Ibias (b) RL Clk Clk RL Differential Output + SingleŦended Input (Reduced Swing) TG Ibias CMOS Inverter Ibias Fig. 6: Proposed MCML Latch Fig. 7: Differential Converters. (a) Conventional (b) Modified for improved performance against VTH variations. Feedback transistors are connected between the input and the output as shown in Fig. 5. In the always-on configuration they work as a feedback resistance. The effect of these feedback resistances results in wider operation bandwidth, or at same frequency, larger stability against threshold voltage fluctuation. Since feedback transistors are connected between data inputs and outputs of the latch, in hold mode any change in the input data will directly affect the output state. As MCML output swing is relatively small, these fluctuations in the output may result in a false state and metastability in the master slave configuration. 4.3. Proposed MCML Latch Other than small propagation delay in the sampling mode and isolation from the data in hold mode through current switching, another important aspect is the input output coupling and clock feed through due to the device overlap capacitance. This can be eliminated using the capacitive feedback [2]. However any additional capacitance connected at the output should be avoided because it will result in higher D-Q delay. Cross-coupled capacitors connected at the Clk transistors will neutralize the effect of clock feed through. At high frequencies these capacitors can result in spikes at the output due to sharp clock edges. The addition of a series resistance can eliminate this problem. However a purely resistive component will try to equalize the differential outputs resulting in failure of the latch operation. So a high resistance is required for clock feed through cancellation. It is not area efficient to use capacitors in the integrated environment. A cross-coupled feedback transistor pair at the Clk terminals will suffice the requirement of both the capacitor and resistor, as shown in Fig. 6. This significantly improves the performance in terms of speed as compared to normal feedback structure, and the latch operation is more reliable. It also results in reduced dynamic power dissipation due to stable output. Simulation results are presented in Table-I. The aspect ratio of feedback transistors (W/L)FB should be kept small for higher resistance, whereas larger width is required for more capacitance. However larger (W/L)FB will create instability and spikes at the output, or complete failure at the extreme. So careful sizing must be performed according to other transistor sizes and currents in the latch. 5. DIFFERENTIAL CONVERTER CML is a differential logic style. A growing number of electronic applications, both digital and analog, use differential circuit techniques, but unfortunately almost all high performance test instruments, including sampling oscilloscope and signal generators, are single-ended, ground-referenced, 50 Ohm instruments. In order to avoid external differential converters due to limited number of pins, an on-chip differential converter can be used for both clock and data signals. This also eliminates the mismatches in phase and provides perfectly complementary signals at very high frequencies. CML inverter’s differential input voltage swing must be equal to its output swing, in order to get equal rise/fall times and duty cycle. It requires a minimum input common mode voltage to keep the current source in saturation, which cannot be accomplished in full swing. Therefore a reduced input swing must be used. In a conventional CMOS to CML converter the inputs of CML inverter are overlapping due to the delay of CMOS inverter. It results in unequal rise and fall times of the output. In order to match the delay of the CMOS inverter an all time on transmission gate is used along with a cross-coupled inverters pair between the CML inverter’s differential inputs, as shown in Fig. 7. The structure is insensitive to the rise and fall times of signals, so the performance of the master slave latch is fairly consistent. 6. SIMULATION RESULTS Using different simulation methods makes it difficult to interpret the comparison results of various latches and flip-flops. The test bench used for simulation is shown in Fig. 10 with the simulation environment given in Table-I. The clock and data signals were fed through the differential converter, which consumes approximately 300µW power at maximum 3.3GHz clock activity. Output waveforms of falling edge triggered MS latches are shown in Fig. 10. False states and metastability can be seen in latches other than proposed. The proposed latch has lower setup/hold time and D-Q delay. Curves of Clk-Q and D-Q delays are plotted for various latches against D-Clk delay and are shown in Fig. 8. ,9 Authorized licensed use limited to: Carleton University. Downloaded on July 13, 2009 at 14:26 from IEEE Xplore. Restrictions apply. Simulation Environment Technology Conventional Latch Feedback Latch Proposed Latch L-H 40 62 19 H-L 42 65 21 L-H 27 -5 17 H-L 30 13 15 L-H 156 149 106 H-L 157 208 112 Simulation Parameter 0.18µm CMOS Setup Time (ps) Process Corner Typical o Temperature 27 C Hold Time (ps) Supply Voltage 1.2 V Data/Clock Rise & Fall Time 30% of Tclk Clock Period (Tclk) 300 ps Internal Power Consumption (µW) < 265 < 240 < 275 Output Load 2 pF Power Delay Product (f J) < 45 < 42 < 30 Minimum D-Q (ps) Table-I: Simulation Environment and Comparison Results of MCML Master Slave Latches 250 D-Q Delay 200 Time [ps] Data PInternal PData Differential Converter Q D Q D MCML MS Ŧ Latch 150 Clock 100 Clk-Q Delay 50 Clk PClock Differential Converter CL CL Clk Fig. 10: Simulation Test Bench Conventional Feedback Proposed 0 0 50 100 D-Clk Delay [ps] Fig. 8: D-Q and Clk-Q delays of various latches 7. CONCLUSION 150 In this paper a brief introduction to the MOS Current Mode Logic was given. Operation of a conventional MCML latch was described and some modified structures were presented. A modified structure with feedback clock transistors is proposed which increases the stability and performance measures. Results in a 0.18- µm CMOS process show that the proposed latch is more stable and has lower setup/hold time and minimum D-Q delay as compared to other MCML latches. 8. REFERENCES Fig. 9: Output Waveforms of MS-Latches [1] Vladimir Stojanovic, and Vojin G. Oklobdzija, “Comparative Analysis of Master-Slave Latches and Flip-Flops for High-Performance and Low-Power Systems,” IEEE Journal of Solid State Circuits, Vol. 34, No. 4, April 1999. [2] Heydari, P., Mohavavelu, R., “Design of Ultra High-Speed CMOS CML buffers and Latches,” Proceedings of the 2003 Int’l Symposium on Circuits and Systems, Vol. 2, May 2003. [3] Tanabe, A., Umetani, M., Fujiwara, I., Ogura, T., Kataoka, K., Okihara, M., Sakuraba, H., Endoh, T., Masuoka, F., “0.18µm CMOS 10-Gb/s Multiplexer/Demultiplexer ICs using current mode logic with tolerance to threshold voltage fluctuation,” IEEE Journal of Solid State Circuits, Vol. 36, No. 6, June 2001. [4] Mizuno, M.; Yamashina, M.; Furuta, K.; Igura, H.; Abiko, H.; Okabe, K.; Ono, A.; Yamada, H.; ”A GHz MOS adaptive pipeline technique using MOS current-mode logic,” IEEE Journal of Solid-State Circuits, Vol. 31, No: 6, June 1996. ,9 Authorized licensed use limited to: Carleton University. Downloaded on July 13, 2009 at 14:26 from IEEE Xplore. Restrictions apply.