New Process Development for Planar-Type CIC Tunneling

advertisement

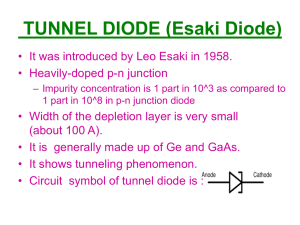

IEEE ELECTRON DEVICE LETTERS, VOL. 31, NO. 8, AUGUST 2010 809 New Process Development for Planar-Type CIC Tunneling Diodes Kwangsik Choi, Filiz Yesilkoy, Athanasios Chryssis, Mario Dagenais, Fellow, IEEE, and Martin Peckerar, Fellow, IEEE Abstract—A planar-type conductor–insulator–conductor tunneling diode is developed using a boiling water process for surface oxidation. First, microsized bow-tie patterns are transferred on a doped polysilicon layer using e-beam lithography. After reactive ion etching, the polysilicon bow-tie pattern has a very narrow knot between two triangles. Using a buffered oxide etchant (BOE) solution, hydrogen silsesquioxane patterns and native oxide layer are etched. The knot is oxidized by a boiling water oxidation process. By repeating the BOE etch and oxidation, the bow-tie patterns are transformed into tunneling diodes with a very thin oxide barrier separating two polysilicon conductors. We show that the resulting structures follow the Simmons tunneling current–voltage relationship after boiling. Moreover, a high sensitivity of 31 V−1 is achieved at a bias voltage of 80 mV. this phenomenon is applicable in tunneling diodes, the performances of tunneling diodes can be improved by increasing tunneling currents. However, most thin-film MIM tunneling diode structures are not appropriate to use the field enhancement or “lightning rod” effect due to the overlap tunneling junction structures [4]–[6]. Therefore, a planar-type tunneling diode is required to exploit near-field enhancement. In this letter, we report new processes for a planar-type polysilicon tunneling diode that allows coupling SPRs. E-beam writing is used for device patterning, and a thin insulator is achieved by boiling water for surface oxidation of polysilicon pattern. Index Terms—Bow-tie antenna, metal–insulator–metal (MIM) diode, optical antenna, surface plasmon, surface plasmon resonance (SPR), tunneling diode. II. D EVICE FABRICATION I. I NTRODUCTION M ETAL–INSULATOR–METAL (MIM) diodes are tunnel junction devices that have a sandwich structure with an insulator layer between two conductors. The early devices were called whisker or contact diodes, implemented with a sharpened tip on a metal surface with an air or vacuum gap [1]–[3]. However, the whiskers were mechanically fragile, and the process repeatability was poor. The second generation uses thin-film technologies and e-beam writing to overcome these deficiencies [4], [5]. MIM diodes have many attractive properties: The operating speed is high (up to visible frequencies) [5], processes, including metal and insulator layer deposition, are repeatable and stable, the devices can be integrated with popular CMOS processes, and antennas can be integrated with the tunneling diodes [6]. Recently, we have focused on merging the tunneling diodes with plasmonics to use near-field enhancement by the surface plasmon resonance (SPR) in optical antennas. Many research results on optical antennas have shown an electric-field enhancement caused by SPRs at the in-plane gap of bow-tie metal patterns [7], [8]. This is also called as a “lightning rod” effect. If Manuscript received April 5, 2010; accepted April 26, 2010. Date of publication June 28, 2010; date of current version July 23, 2010. This work was supported in part by the Naval Air Systems Command (NAVAIR) under Grant N00042-1081003, with Charles D. Caposell as the Program Manager. The review of this letter was arranged by Editor C. Bulucea. The authors are with the Department of Electrical and Computer Engineering, University of Maryland College Park, College Park, MD 20742 USA (e-mail: choiks@umd.edu). Digital Object Identifier 10.1109/LED.2010.2049637 The device fabrication consists of four steps: preparing substrate, patterning device, repeating etch/oxidation, and pad metallization. For device isolation, we start with Si3 N4 deposition on a Si wafer using PECVD, and then, a polysilicon layer is deposited on the Si3 N4 using LPCVD to create the active device material. Each layer has 800- and 600-Å thicknesses, respectively. Polysilicon doping is performed using spin-ondopant (SOD) of phosphorus dopants, followed by RTA to diffuse dopants. After SOD coating, the sample is baked at 200 ◦ C for 20 min on a hot plate. A simple RTA process at 1000 ◦ C during 30 s transfers the dopants into the deposited polysilicon layer. Finally, the SOD is removed using buffered oxide etchant (BOE). For device patterning, we use e-beam writing instead of optical lithography because of its higher resolution. A bow tie is chosen for the basic device shape with 60◦ flare angle. Hydrogen silsesquioxane (HSQ) and CD-26 are used as an e-beam resist and a developer, respectively. A 10-kV acceleration voltage and a 10-μm aperture size result in 12-pA current for a Raith e-LiNE writer. The 160 μC/cm−3 writing dose gives almost perfect dose clearance for the bow-tie patterns. After the development, reactive ion etching (RIE) etching is applied using SF6 and O2 to etch out the polysilicon layer. Electronexposed HSQ patterns work as etch stop layer during RIE etching, and it is removed using BOE after dry etching. Right after the RIE etching, the two flares of the bow tie are connected by a thin polysilicon knot [see Fig. 3(a) and (b)]. To implement a conductor–insulator–conductor (CIC) structure, we use a boiling water oxidation process. This accelerates growth of the native oxide [9]. To check the polysilicon etch rate by the boiling water oxidation process, we set an experiment 0741-3106/$26.00 © 2010 IEEE 810 Fig. 1. BOE etching and boiling water oxidation test result for 16 samples. One cycle is composed of 20-s etching in BOE and 1-min boiling. The 16 samples are divided into four groups, and the different numbers of cycles are applied to each group, such as 1, 5, 10, and 15 cycles. The lateral etching thickness of doped polysilicon is checked using a SEM. Fig. 2. Schematic for device fabrication process flow. (a) Si3 N4 deposition. (b) Poly-Si deposition and doping. (c) E-beam writing with HSQ. (d) RIE dry etching. (e) HSQ removing. (f) Etch and oxidation. cycle: 20-s etch in BOE (10:1) and 1-min oxidation in boiling water. The etch rate is monitored by SEM for different numbers of cycles for 16 samples. The test results are shown in Fig. 1. From the experiments, the average etch rate is approximately 7 Å/cycle using a linear fit for average values of lateral etching thickness of doped polysilicon. This experiment result shows that the boiling water process is controllable and repeatable. This etch and oxidation cycles are applied to bow-tie patterns. After each cycle, dc IV measurement is performed to monitor a polysilicon knot transformation into a CIC structure. When measured, current property is changed from linear to nonlinear, the boiling oxidation process is stopped, and the pattern is checked using SEM. The overall process is shown in Fig. 2 before the pad metallization along the dashed line shown in Fig. 3(a). Metal pads (Ti/Au) are made using regular metal liftoff process. A SEM image of the fabricated bow-tie pattern is shown in Fig. 3(a) after RIE etching, designed with 60◦ regular flares of 4.3 μm IEEE ELECTRON DEVICE LETTERS, VOL. 31, NO. 8, AUGUST 2010 Fig. 3. Device SEM images. (a) Fabricated polysilicon bow-tie pattern with 60◦ flare angle. (b) Polysilicon knot between flares. (c) Before etch and oxidation process. (d) After etch and oxidation process. Note that the devices in (c) and (d) are the same device. Fig. 4. DC IV measurement before and after the etch/oxidation process. The current–voltage property is changed from linear to nonlinear. Theoretical fit gives 1.38-nm SiO2 barrier thickness. each side length. Fig. 3(b) shows a magnified SEM image of the knot. III. E XPERIMENT R ESULT We have performed dc I–V measurements after each etch and oxidation cycle to observe the tunneling currents using a probe station and a parameter analyzer. The inset plot in Fig. 4 shows the dc I–V result of the device shown in Fig. 3(c), before the etch/oxidation process. It displays a linear I–V relation. However, the IV characteristic is changed to nonlinear after one cycle of etch/oxidation process for this device, as shown in Fig. 4. The SEM image of Fig. 3(d) shows the shape after one cycle etch/oxidation process. In Fig. 4, the filled circle line is a fit using Simmons’ tunneling current model [10]. For the fit, we assumed the junction area and the insulator type to be 60 nm2 and silicon oxide with 2.9-eV barrier height. The theoretical fit yields a 1.38-nm oxide thickness. Through our new process, we achieve very high sensitivity, one of the figures of merit for tunneling diodes. Using a CHOI et al.: NEW PROCESS DEVELOPMENT FOR PLANAR-TYPE CIC TUNNELING DIODES 811 IV. C ONCLUSION We have developed a new and simple process for fabricating planar-type CIC tunneling diodes using e-beam writing and a boiling water oxidation process. The boiling water process transforms the bow-tie pattern, obtained by optimized e-beam writing, into a planar-type CIC tunneling diode. Using SEM and dc IV measurements, we have demonstrated planar-type tunneling diode processes and operations. A diode sensitivity of 31 V−1 is achieved. This is the highest sensitivity ever reported for a thin-film MIM tunneling structure. This new planar-type MIM tunneling diodes can use high electric-field enhancement by SPRs or “lightning rod” effect. R EFERENCES Fig. 5. (Open circles) IV measurement data and (solid line) polynomial fit of a CIC diode are shown. (Dashed line) Sensitivity is calculated and plotted by I /I using the polynomial fit. TABLE I S ENSITIVITY C OMPARISON (F ROM [12]) polynomial fit to the measured data, I and I are obtained. The sensitivity is calculated as I /I . The highest sensitivity is 31 V−1 at 80 mV, which is the highest ever reported for a thin-film MIM tunneling diode. The closest reported value is disclosed in [11]: 13 V−1 . The measurement data, polynomial fitting, and sensitivity of the highest sensitivity diode are shown in Fig. 5. The asymmetric IV curve is due to the asymmetry of the device shape for the two polysilicon triangles. That is, one flare is sharper than the other. It makes the electron tunneling easier from the sharp to the blunt side of the diode by geometric field enhancement and therefore gives asymmetric IV characteristic. The asymmetry factor improves rectification. To compare with our results, recent measurements of the sensitivity are listed in Table I, taken from [12]. [1] J. W. Dees, “Detection and harmonic generation in the sub-millimeter wavelength region,” Microw. J., vol. 9, no. 25, pp. 48–55, 1966. [2] L. M. Matarrese and K. M. Evenson, “Improved coupling to infrared whisker diodes by use of antenna theory,” Appl. Phys. Lett., vol. 17, no. 1, pp. 8–10, Jul. 1970. [3] S. Faris, T. Gustafson, and J. Wiesner, “Detection of optical and infrared radiation with DC-biased electron-tunneling metal-barrier-metal diodes,” IEEE J. Quantum Electron., vol. QE-9, no. 7, pp. 737–745, Jul. 1973. [4] T. K. Gustafson, R. V. Schmidt, and J. R. Perucca, “Optical detection in thin-film metal–oxide–metal diodes,” Appl. Phys. Lett., vol. 24, no. 12, pp. 620–622, Jun. 1974. [5] M. Heiblum, S. Wang, J. Whinnery, and T. Gustafson, “Characteristics of integrated MOM junctions at dc and at optical frequencies,” IEEE J. Quantum Electron., vol. QE-14, no. 3, pp. 159–169, Mar. 1978. [6] C. Fumeaux, W. Herrmann, F. K. Kneubuhl, H. Rothuizen, B. Lipphardt, and C. O. Weiss, “Nanometer thin-film Ni–NiO–Ni diodes for mixing 28 THz CO2 -laser emissions with difference frequencies up to 176 GHz,” Appl. Phys. B: Lasers Opt., vol. 66, no. 3, pp. 327–332, 1998. [7] D. P. Fromm, A. Sundaramurthy, P. J. Schuck, G. Kino, and W. E. Moerner, “Gap-dependent optical coupling of single “bowtie” nanoantennas resonant in the visible,” Nano Lett., vol. 4, no. 5, pp. 957–961, May 2004. [8] A. Sundaramurthy, K. B. Crozier, G. S. Kino, D. P. Fromm, P. J. Schuck, and W. E. Moerner, “Field enhancement and gap-dependent resonance in a system of two opposing tip-to-tip Au nanotriangles,” Phys. Rev. B, Condens. Matter, vol. 72, no. 16, p. 165 409-6, Oct. 2005. [9] J. W. Beck, “Boiling water oxidation rates on silicon,” J. Appl. Phys., vol. 33, no. 7, p. 2391, Jul. 1962. [10] J. G. Simmons, “Generalized formula for the electric tunnel effect between similar electrodes separated by a thin insulating film,” J. Appl. Phys., vol. 34, no. 6, pp. 1793–1803, Jun. 1963. [11] P. Esfandiari, G. Bernstein, P. Fay, W. Porod, B. Rakos, A. Zarandy, B. Berland, L. Boloni, G. Boreman, B. Lail, B. Monacelli, and A. Weeks, “Tunable antenna-coupled metal–oxide–metal (MOM) uncooled IR detector (Invited Paper),” Proc. SPIE, vol. 5783, pp. 470–482, 2005. [12] S. Krishnan, H. La Rosa, E. Stefanakos, S. Bhansali, and K. Buckle, “Design and development of batch fabricatable metal–insulator–metal diode and microstrip slot antenna as rectenna elements,” Sens. Actuators A, Phys., vol. 142, no. 1, pp. 40–47, Mar. 2008.