High Efficiency and Low Noise Charge Pump Circuits for Non

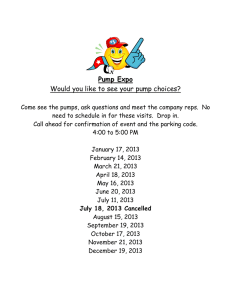

advertisement