Thermal Characterization of Packaged RFIC, Modeled vs

advertisement

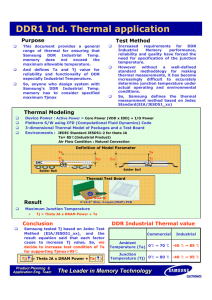

Thermal Characterization of Packaged RFIC, Modeled vs. Measured Junction to Ambient Thermal Resistance Steven Brinser IBM Microelectronics Abstract Thermal characterization of a semiconductor device is the determination of the maximum junction temperature (Tjmax) of the die circuit during worst case operating conditions, as well as the thermal resistances of the semiconductor package alone, and attached on the second level to a Printed Circuit Board (PCB). The die junction temperature (Tj) is directly related to the life of the product, and is used in reliability calculations to rate the power on hours the product can produce during its life. The higher the circuit junction temperature during operation, the quicker product end of life will be reached. The maximum junction temperature of the die cannot exceed the maximum temperature specified in the technology's design and reliability specifications. In today's wireless market, devices are getting smaller in size and power dissipations are on the rise. This produces higher heat fluxes on the semiconductor die producing higher junction temperatures. The design of both the package that encapsulates the die and the printed circuit board it is attached to become instrumental in removing heat from the die. This is a study characterizing an RFIC silicon germanium (SiGe) die packaged in an exposed paddle QFN 20 lead package that is soldered to an assumed PCB. Thermal modeling done in ANSYS 5.7.0 was correlated to measured results using a JEDEC compliant system for semiconductor packaging thermal measurements. The test system used for this study is a "Phase 10 Thermal Analyzer" from Analysis Tech in Wakefield, MA. Introduction In order to get a clear understanding and confidence in Finite Element Analysis (FEA) modeling results, it is necessary to physically test the device to compare results. This approach holds true for any product. For example, aircraft manufacturers will test bend an airplane wing from tip to fuselage until failure to measure maximum deflection, stress/strain, and location of failure. The test data taken is used to correlate to FEA stress models. The same approach is used in semiconductor thermal characterization. Careful attention to detail must be taken to ensure that the FEA model and device under test are as close to the same design as possible. This way we are comparing apples to apples. In this case, the semiconductor device will be installed in a cell phone or some type of wireless hand held product. A typical cell phone PCB design is assumed for both modeling and testing. This helps to simulate the thermal performance of the device in as close to actual operating conditions as possible. The JEDEC packaging standard states that PCB characteristics can have a dramatic impact on thermal measurements, greater than 60% variation on results. Due to this wide variability, JEDEC defined an industry-wide standard for the design of thermal test boards to keep results common. Modeling is also done using the specs for the JEDEC standard thermal test board. By having a common standard PCB, companies can compare one package with another for thermal performance, and not be concerned with the variability of PCB effects. The mistake that is often made is using this standardized junction to ambient data as actual operating conditions for the product, remember the 60% variation in results stated by JEDEC. To obtain results from this model, thermal boundary conditions are applied, in this case Natural Convection, and heat generating power is applied to very specific areas on the die. The junction temperature is solved for and used to calculate the junction to ambient thermal resistance, and junction to case thermal resistance. By knowing the thermal resistances, now Tj can be calculated for any ambient temperature, power level, or PCB temperature that the device will be subjected to during it's operating life. The FEA model also provides valuable data on the design of the PCB that will be used in the cell phone, and how it's design affects the thermal performance of the packaged semiconductor. Terms and Nomenclature Figure 1 shows a side view of the model used in this study. The plastic mold compound that encapsulates the die has been removed for clarity. The die is epoxied to a copper leadframe, which is soldered to the top metal layer of the PCB. The QFN Package has a leadframe that is an "exposed paddle" design which provides a direct thermal path from die to PCB. The heat then flows through thermal vias in the PCB, which are copper plated through holes that connect to PCB internal metal planes that extend outward in the PCB. The thermal via connectivity to the copper planes acts as heat sink fins to dissipate the heat energy from the die. The heat energy then travels out of the PCB into the air where it is cooled. The thermal resistance from die through the package and PCB to the air is called the Junction to Ambient Thermal Resistance (Theta JA) and is measured in °C/Watt. Tc is the Case Temperature and is located on the bottom surface of the leadframe. The Junction to Case Thermal Resistance (Theta JC) represents the thermal rating for the die and package only, omitting the PCB from the equation. The only factors affecting Theta JC are the die characteristics such as size, thickness, power mapping and the package thermal characteristics. Theta JC (°C/Watt) for a package/die will remain at a constant value regardless of the PCB design. The Theta JA however will vary with the design of the PCB. In some cases, the package will only represent 10% of the total Theta JA value with the PCB representing 90% of Theta JA. For this reason, the PCB becomes a very important component when specifying a Junction to Ambient Thermal Resistance for a Package. Figure 1 - QFN20 Package Soldered to Cell Phone PCB Tjmax Maximum Junction Temperature Tc Case Temperature Ta Ambient Temperature Theta JA = (Tjmax - Ta) / Power Theta JC = (Tjmax - Tc) / Power The equations above are used to calculate the thermal resistances Theta JA and Theta JC. Temperatures are taken from the model at the die top surface for Tjmax, and on the bottom surface of the exposed paddle leadframe for Tc. The ambient air temperature is known, and used as a surface convection load. The power dissipation is also a known value, and is applied as a heat generating body load. ANSYS users should note that this is an internal surface in the model and a heat flux surface load could cause erroneous results due to its one directional heat flow. A body load will disperse the heat in all directions for internal surface loads according to the thermal conductivity and geometry of the materials. FEA Model Figure 2 shows the temperature gradients on the external surfaces of the package attached to the PCB. The QFN package is in the center of the PCB and is soldered to the top metal layer on the board, which is slightly larger in size than the package. The maximum temperature shown of 106.1°C is on the top surface of the plastic mold compound of the package. The PCB has multi layers of metal with insulating dielectric material between layers. The Ta ambient air temperature was set to 70°C Natural Convection, and 1 Watt power dissipation is applied. All detailed model views that will be examined in this document are taken from this complete assembly model shown in Figure 2. The die, leadframe, thermal vias, inner PCB layers, epoxy and solder layers, etc., are all contained in the model below and are viewed in whatever combination provides us with the data being sought. Figure 2 - QFN20 attached to PCB Figure 3 shows how the thermal vias are spreading the heat onto the inner layer of metal within the PCB. Both the mold compound and PCB dielectric materials have been removed for clarity. The inner layer was modeled as a solid volume, however it’s thermal conductivity was reduced by the volumetric reduction of the metal as compared to the actual layer geometry. This averaging of thermal conductivity is an accepted practice and produces accurate results if estimated accurately. Figure 3 - Thermal Vias Spreading Heat from the package to PCB inner metal layer Figure 4 shows the die epoxied to the leadframe. The Tjmax of 110.16°C is shown on the die. By applying the power dissipation to specific areas on the die, the spreading resistance in the die can be viewed along with hot spots of maximum temperature, and uniformity of temperature on the die surface. Figure 4 - Die Epoxied to Leadframe, Tjmax of 110.16°C Shown Figure 5 shows the case temperature gradients on the bottom surface of the leadframe. Some leads are fused to the exposed paddle which helps with thermal spreading, however the maximum Tc is shown near the center of the exposed paddle. This Tcmax area of 103.8°C is the main path of heat flow to the PCB. The range of case temperatures is viewed from Tcmin of 101.2°C to Tcmax of 103.8°C, and is used to calculate Theta JC for the package. When packages are specified for Theta JC, the average value is provided. In this case the Theta JCmin is 6.315°C/W and Theta JCmax is 8.83°C/Watt. This QFN20 package and die is then specified at 7.57°C/Watt. This thermal resistance rating is based on the temperature drop per watt of the die, die attach epoxy, and leadframe. Theta JC will remain constant for this packaged assembly regardless of the PCB design as shown in Chart 1 in Model Results. Figure 5 - Case Temperature on Bottom of Leadframe Exposed Paddle and Leads FEA Model Results Chart 1 and Table 1 show the results from the model shown. The model has 16 thermal vias in a 4 x 4 array connecting the top metal layer in the PCB that the package is soldered to, to a PCB inner metal layer and also a small sized metal layer on the back side of the PCB. Today's PCB Design Engineers are challenged in many ways. The area under the package is heavily populated with metal traces for electrical signaling, leaving very little space for thermal vias. Also plated through holes connecting to inner layers takes time and additional cost to manufacture. However at the same time thermal requirements must be satisfied for reliability qualification of the product. Chart 1 provides the PCB designer with the information that is needed to minimize the amount of thermal vias to meet thermal requirements. Theta JA and Tjmax are affected by the design of the PCB, and are decreasing in a nonlinear fashion with the increase of thermal vias in the PCB. This is due to the vias acting as resistors in parallel with the area of the vias as the variable being reduced. Notice that from 0 to 4 vias we see a 10° drop in Tjmax, where from 12 to 16 vias there is only a 0.83° drop in Tjmax. Theta JC is represented by the lower horizontal line in the graph. Notice that Theta JC for the package remains constant regardless of variation in PCB design, Tjmax, or Theta JA. This study is beneficial to compare packages with one another using Theta JC values, predict closely the thermal performance of the package under actual operating conditions, and provide PCB Design Engineers with valuable data to thermally optimize the design of their products. Chart 1 - PCB Design vs. Thermal Results QFN20 4x4 Soldered to 4 Layer PCB 70oC Ambient 160 Theta JA (Deg C/Watt) 54.399 Theta JC min (Deg C/Watt) 50 150 44.572 41.979 140 40.787 40 39.96 30 130 124.671 119.412 120 20 117.023 114.795 112.189 110 110.991 110.16 10 6.295 6.224 6.324 6.331 6.291 6.331 6.315 0 100 0 4 8 No. of Thermal Vias in PCB Ground Pad 12 16 Theta JA (Deg C/Watt) Theta JC min (Deg C/Watt) 46.789 49.166 Tjmax (Deg C) 60 Tjmax (Deg C) Table 1 - PCB Design vs. Thermal Results QFN20 4x4 mm Thermal Results @ 1.005 Watts # Vias Through PCB Theta JA (oC/Watt) Tjmax (oC) @70oC Ambient Tcase (oC) Theta JC (oC/Watt) 16 39.96 110.16 103.813 6.315 12 40.787 110.991 104.628 6.331 8 41.979 112.189 105.833 6.324 4 44.572 114.795 108.432 6.331 2 46.789 117.023 110.7 6.291 1 49.166 119.412 113.085 6.295 0 54.399 124.671 118.416 6.224 Test Measurement Methods The Electrical Test Method (ETM) used in this study conforms to JEDEC packaging standard methods for thermal testing and is widely used in the industry for testing Tjmax and Theta JA. For this study the thermal test board is identical in design to the cell phone PCB used for modeling. There are 16 thermal vias in the test board in an attempt to correlate to the FEA results for the 16 via model. For testing accuracy, the actual product's die packaged in QFN20 is soldered to the test board. Its leads are probed with a DC voltmeter to find a diode in the circuit suitable for testing. This diode is usually the substrate isolation diode that is present to separate circuit elements from each other. The method uses the junction voltage across the diode as a temperature sensitive electrical parameter. The diode is calibrated in a hot oil bath with a very small value of current to not introduce heating. The oil temperature is dropped at a slow rate and a linear relationship is established for junction voltage vs. temperature. The device under test is then put in an environmental fixture, for this study a still air box at room temperature was used, and the diode is powered to a chosen level. Because the diode is forward biased it acts as a temperature sensor and also the heating element. The heat is generated and sensed at the same location on the die producing a good estimate of the highest junction temperature internal to the chip. The testing system records all data taken from calibration, as well as ambient air temperature in the still air box or oven, thermocouples attached to the case or leads, and power level applied. The system then provides a Tjmax, Delta T, which is the temperature rise of the die above ambient air, and Theta JA of the package on board. Test Measurement Results Chart 2 shows actual test data taken on the modeled device on the assumed cell phone test board. Tjmax of the die is shown under 0.5 Watts of power and an ambient still air temperature of 23.4°C. The plot represents a temperature sensing time of 300us which is then linearly extrapolated back to time zero for the Tjmax reading of approximately 44°C. The system has already determined that steady state has been reached and is continuously sensing junction temperature for 300us at a time. Chart 3 shows Delta T for the same test. Readings here are between 20°C and 21°C. The system has calculated the Theta JA for this test and provides the number of 41.1°C/Watt. Theta JA becomes to common variable for comparing measured results and FEA modeled results. Chart 2 - Junction Temperature during Test Chart 3 - Temperature Rise Above Ambient FEA Model Results Compared to Measured Results Table 2 compares the Theta JA between modeled and measures results on the same PCB. By getting an error of less than 3% between the two, a confidence level is gained assuring that the procedures for both modeling and testing are valid. With the 16 via model correlating so well to testing on a 16 via identical test board, the other data taken from the FEA model can be viewed as accurate such as the reduced thermal via data and Theta JC values. Table 2 Results Comparison Modeled FEA vs. Test Measurements Modeled vs. Measured Theta JA # Vias Power Theta JA Through Dissipation o ( C/Watt) PCB (Watts) Modeled 16 1.005 39.96 Measured Results 16 0.5 41.1 % Error Modeled Measured between Tjmax o Tjmax ( C) modeled vs (oC) o @23.4 C measured @70oC Ambient Theta JA Ambient 110.16 2.85% 44-45 Conclusion When modeling and testing packaged semiconductors for thermal performance, careful attention to product details, such as PCB design, and thermal boundary conditions are important for accuracy of results. Using the design specifications of the actual printed circuit board used during product operation will provide the most accurate thermal characterization of the device during operation, which is the goal. Standard test boards in the industry are used for package comparison only. Thermal performance during the product's actual operation will be significantly different, and can actually be controlled and optimized before the product is manufactured using simulations such as this. Theta JC can be accurately extracted from the convection model and is a very useful specification for comparing packages with one another. Theta JC is also useful for specifying a package's thermal performance by itself if no PCB has been designed yet. The trend in the industry lately has been to specify Theta JC for the package rather than a Theta JA on a standard test board. This way it becomes very clear that the thermal performance during operation is dependent on the PCB design that is installed in the wireless product. In most cases enough data on PCB specifications can be supplied and used to predict operating conditions. Thermal optimization studies of PCB designs can easily be done in ANSYS to meet thermal requirements as well as minimize manufacturing cost issues. Testing should always be done if possible to ensure that FEA modeling procedures are accurate. References Dr. John Sofia, Fundamentals of Thermal Resistance Measurement, 1995, Analysis Tech, Wakefield, MA www.analysistech.com Bernie Siegal, Elements of Device Thermal Characterization EIA/JESD51-1, JEDEC IC Thermal Measurement Method - ETM (Single Semiconductor Device) EIA/JESD51-2, JEDEC IC Thermal Test Method Environmental Conditions - Natural Convection-Still Air EIA/JESD51-3, JEDEC Low Effective Thermal Conductivity Test Board The author wishes to acknowledge Dr. Ephraim Flint and Paul Panaccione for their mentoring and support