TM 11-5895-1284-13

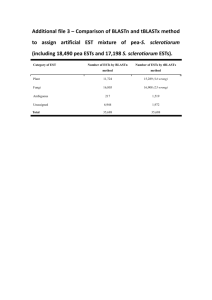

advertisement