Analog Integrated Circuits - Integrated Systems Laboratory

Integrated Systems Laboratory

Analog Integrated Circuits

(The lectures and the exercises are given in English)

Department of Information Technology and Electrical Engineering (D-ITET),

5. and 7. Semester

Prof. Dr. Q. Huang

Autumn term 2016

Lectures: ETZ E6 Friday 10:15 – 11:55

Exercises: ETZ E6 & D61.1 Friday 13:00 – 15:00

Coordination: Thomas Burger

(burger@iis.ee.ethz.ch)

Assistants: Xu Han

Thomas Kleier

Danny Luu

ETZ J94 255 28

ETZ J64.2

271 58

ETZ J61 252 44

ETZ J61 279 86

The attendance at the exercises is highly recommended, however not mandatory for the admittance to the exam. They are indeed essential for the understanding and provide valuable insight into the analog circuits design-flow.

Since the nineteen-seventies the advantages of digital circuits have led to predictions that everything would become digital. Such predictions appear to become reality today since the most important applications, such as telephony, mobile communications and high definition television adopt a digital approach.

This leaves the impression that digital circuits will simply replace analog circuits until the latter will totally disappear from the electronic systems we use. In reality, the pervasiveness of digital circuits has increased the importance of analog circuits for the simple reason that most digital systems need analog circuits to interface with the real world which is analog. Analog circuits, instead of disappearing, have expanded with digital circuits into new applications. Although analog circuits often occupy only a small fraction of the total area of an integrated circuit, their performance is critical in deciding the overall performance of the system. Analog integrated circuit design is therefore among the most sought after skills by the integrated circuit (IC) industry.

This course provides a foundation in the analysis and design of most commonly used analog integrated circuits in both bipolar and CMOS technologies.

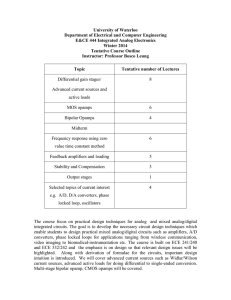

Date Lecture Topic

23. 9.

Introduction and background, review of BJTs and MOS-

FETs

30. 9.

Device Characteristics.

Large and small signal models, short-channel effects, passive components

07. 10.

Analog Sub-circuits.

Current sources and mirrors, active loads, supply independent biasing, voltage references

14. 10.

Basic Amplifiers.

Common-source, source-follower and common-gate amplifiers

21. 10.

Amplifiers.

Differential input stage, cascode amplifier high gain structures, output stages

28. 10.

Two Stage Amplifier.

Miller Op-Amp

04. 11.

Fully Differential OTAs.

Gain bandwidth product, stability, phase and amplitude margin

11. 11.

Fully Differential OTAs.

Regulated cascode, common-mode feedback

18. 11.

Comparators.

Exercise Topic

1: Op-amp characterization

2: Introduction to Cadence

3: Analog subcircuits

4: Common-source and differential amplifiers

25. 11.

Second-Order Effects.

Mismatch of geometrical and electrical parameters, offset, clock feed-through, noise

02. 12.

Switched-Capacitor Filter.

SC integrator, op-amp requirements, settling, slewing

09. 12.

A/D and D/A Converters.

Characterization, integrating converters, successive approximation A/D converters

16. 12.

Sigma-Delta Analog-to-Digital (A/D) converters and design example

23. 12.

Revision

5: Design of a single stage op-amp

6: Layout

The lecture slides/ script, the exercise tasks and their solutions can be found on our webpage: http://www.iis.ee.ethz.ch/stud area/vorlesungen/aic.en.html

. To be granted access, you have to be in the ETH network (or connected to it by VPN).

Exercise

3

4

1

2

5

6

Hand out

23.9.

14.10.

28.10.

11.11.

25.11.

09.12.

Date

Assistance special

14.10. / 21.10.

28.10. / 04.11.

11.11. / 18.11.

25.11. / 02.12.

09.12. / 16.12.

Hand in

-

-

-

-

-

-

Place Assistants

ETZ K63

ETZ D61.1

Kleier, Meier, Brun

Luu, Han, (Burger)

ETZ E6 / D61.1

Luu, Han, (Burger)

ETZ E6 / D61.1

Han, Luu

ETZ E6 / D61.1

Luu, Han

ETZ E6 / D61.1

Han, Luu

Some of the exercises are done using Cadence . We provide accounts on our filesystem during the course.

Do not put personal material on these accounts! — Do not change the accounts’ passwords!

The accounts will be removed at the end of the course.