lecture10

advertisement

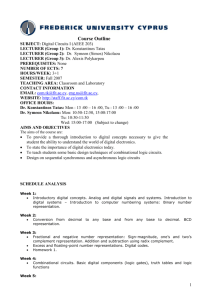

EECS 141 – S02 Lecture 10 Wire Modeling Combinational Logic Digital Integrated Circuits Interconnect © Prentice Hall 2000 Last Lecture Scaling l Wire parasitics l » Capacitance Digital Integrated Circuits Interconnect © Prentice Hall 2000 1 Today’s Lecture l Wire modeling » Resistance » Ellmore Delay » Distributed RC line and models l Introduction to static CMOS gates Digital Integrated Circuits Interconnect © Prentice Hall 2000 Administrivia l Review session » Monday Feb 25, 6:30-8pm, 277 Cory l Office hour Friday Feb 22, » 10:30-12pm in 511 Cory l Midterm Exam Tu Feb 26. Digital Integrated Circuits Interconnect © Prentice Hall 2000 2 Interconnect Digital Integrated Circuits Interconnect © Prentice Hall 2000 The Lumped Model Vo ut c wire Driver Rdriver Vout Vin Clumpe d Digital Integrated Circuits Interconnect © Prentice Hall 2000 3 The Lumped RC-Model The Ellmore Delay Digital Integrated Circuits Interconnect © Prentice Hall 2000 The Ellmore Delay RC Chain Digital Integrated Circuits Interconnect © Prentice Hall 2000 4 Wire Model Assume: Wire modeled by N equal-length segments For large values of N: Digital Integrated Circuits Interconnect © Prentice Hall 2000 The Distributed RC-line Digital Integrated Circuits Interconnect © Prentice Hall 2000 5 Step-response of RC wire as a function of time and space 2.5 x= L/10 2 voltage (V) x = L/4 1.5 x = L/2 1 x= L 0.5 0 0 Digital Integrated Circuits 0.5 1 1.5 2 2.5 3 time (nsec) 3.5 Interconnect 4 4.5 5 © Prentice Hall 2000 RC-Models Digital Integrated Circuits Interconnect © Prentice Hall 2000 6 Driving an RC-line Rs (rw,cw,L) Vout Vin Digital Integrated Circuits Interconnect © Prentice Hall 2000 Design Rules of Thumb l l rc delays should only be considered when tpRC >> tpgate of the driving gate Lcrit >> √ tpgate/0.38rc rc delays should only be considered when the rise (fall) time at the line input is smaller than RC, the rise (fall) time of the line trise < RC » when not met, the change in the signal is slower than the propagation delay of the wire Digital Integrated Circuits Interconnect © MJIrwin, PSU, 2000 © Prentice Hall 2000 7 COMBINATIONAL LOGIC Digital Integrated Circuits Interconnect © Prentice Hall 2000 Overview Static CMOS Conventional Static CMOS Logic Ratioed Logic Pass Transistor/Transmission Gate Logic Dynamic CMOS Logic Domino np-CMOS Digital Integrated Circuits Interconnect © Prentice Hall 2000 8 Combinational vs. Sequential Logic In Logic In Circuit Out Out Logic Circuit State (a) Combinational (b) Sequential Output = f(In, Previous In) Output = f(In) Digital Integrated Circuits Interconnect © Prentice Hall 2000 Static CMOS Circuit At every point in time (except during the switching transients) each gate output is connected to either VDD or Vss via a low-resistive path. The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods). This is in contrast to the dynamic circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes. Digital Integrated Circuits Interconnect © Prentice Hall 2000 9 Static Complementary CMOS VDD PUN … In1 In2 InN F(In1,In2,…InN) PDN … In1 In2 InN PMOS only NMOS only PUN and PDN are dual logic networks Digital Integrated Circuits Interconnect © Prentice Hall 2000 NMOS Transistors in Series/Parallel Connection Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high A B X Y Y = X if A and B A X B Y Y = X if A OR B NMOS Transistors pass a “strong” 0 but a “weak” 1 Digital Integrated Circuits Interconnect © Prentice Hall 2000 10 PMOS Transistors in Series/Parallel Connection PMOS switch closes when switch control input is low A B X Y Y = X if A AND B = A + B A X B Y Y = X if A OR B = AB PMOS Transistors pass a “strong” 1 but a “weak” 0 Digital Integrated Circuits Interconnect © Prentice Hall 2000 Threshold Drops VDD PUN VDD S D VDD D 0 → VDD VGS S CL CL VDD → 0 PDN D VDD CL S Digital Integrated Circuits 0 → VDD - VTn VGS VDD → |VTp| S CL D Interconnect © Prentice Hall 2000 11 Complementary CMOS Logic Style Construction Digital Integrated Circuits Interconnect © Prentice Hall 2000 Example Gate: NAND Digital Integrated Circuits Interconnect © Prentice Hall 2000 12 Example Gate: NOR Digital Integrated Circuits Interconnect © Prentice Hall 2000 Complex CMOS Gate B A C D OUT = !(D + A • (B + C)) A D B Digital Integrated Circuits C Interconnect © Prentice Hall 2000 13