A 0.25- m CMOS Quad-Band GSM RF Transceiver Using an Efficient

advertisement

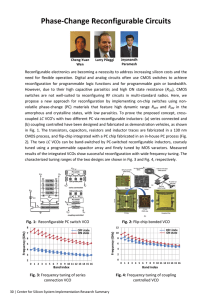

1094 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 A 0.25-m CMOS Quad-Band GSM RF Transceiver Using an Efficient LO Frequency Plan Eunseok Song, Yido Koo, Member, IEEE, Yeon-Jae Jung, Deok-Hee Lee, Sangyoung Chu, and Soo-Ik Chae, Member, IEEE Abstract—This paper describes a single-chip CMOS quad-band (850/900/1800/1900 MHz) RF transceiver for GSM/GPRS applications. It is the most important design issue to maximize resource sharing and reuse in designing the multiband transceivers. In particular, reducing the number of voltage-controlled oscillators (VCOs) required for local oscillator (LO) frequency generation is very important because the VCO and phase-locked loop (PLL) circuits occupy a relatively large area. We propose a quad-band GSM transceiver architecture that employs a direct conversion receiver and an offset PLL transmitter, which requires only one VCO/PLL to generate LO signals by using an efficient LO frequency plan. In the receive path, four separate LNAs are used for each band, and two down-conversion mixers are used, one for the low bands (850/900 MHz) and the other for the high bands (1800/1900 MHz). A receiver baseband circuit is shared for all four bands because all of their channel spaces are the same. In the transmit path, most of the building blocks of the offset PLL, including a TX VCO and IF filters, are integrated. The quad-band GSM transceiver that was implemented in 0.25- m CMOS technology has a size of 3.3 3.2 mm2 , including its pad area. From the experimental results, we found that the receiver provides a maximum noise figure of 2.9 dB and a minimum IIP3 of 13.2 dBm for the EGSM 900 band. The transmitter shows an rms phase error of 1.4 and meets the GSM spectral mask specification. The prototype chip consumes 56 and 58 mA at 2.8 V in the RX and TX modes, respectively. Index Terms—CMOS, dc offset, direct conversion, frequency divider, GSM, LO frequency, offset phase-locked loop (PLL), quadband, transceiver. I. INTRODUCTION T HE wide use of portable communication systems has created a great demand for low-cost, low-power, small formfactor transceivers. In the past, radio frequency (RF) front-end circuits have been implemented with GaAs or bipolar junction transistor (BJT) technologies while the low-frequency baseband circuits have used CMOS technologies. Such implementations using the technologies of different kinds, however, are not suitable as a low-cost solution for RF transceivers. In modern-day implementations, high-frequency CMOS circuits are becoming more feasible due to the aggressive scale-down in CMOS technologies. Thus, the recent research trends have been to develop Manuscript received June 25, 2004; revised October 22, 2004. E. Song and S.-I. Chae are with the ISRC, School of Electrical Engineering, Seoul National University, Seoul 151-742, Korea (e-mail: dooly@sdgroup.snu.ac.kr). Y. Koo, Y.-J. Jung, D.-H. Lee, and S. Chu are with GCT Semiconductor, Inc., San Jose, CA 95131 USA. Digital Object Identifier 10.1109/JSSC.2005.845990 a monolithic transceiver with low-cost CMOS technologies [1], [2]. The Global Systems for Mobile communication (GSM) network spanning over 200 countries is a rapidly growing and evolving mobile standard [3]. It is the first cellular system that specifies digital modulation and network-level architectures and services [4]. There are several frequency bands where GSM terminals are or will shortly be operated. Therefore, a GSM terminal that can support all of the GSM frequency bands listed in Table I will be more useful for its global roaming [3], [5]. Previously, there have been several works related to GSM transceivers [6]–[11]. Early GSM transceivers [6]–[8] employed the super-heterodyne architecture to integrate the receiver and transmitter in a single chip. However, they were implemented with BJT technology and did not integrate all of the functions, requiring several external components, such as an IF filter. Although the GSM transceivers [9], [10] developed later were implemented with low-cost CMOS technology, they still required several off-chip filters for image rejection and channel selection [9] or deferred these tasks to their baseband digital signal processing (DSP) chip [10]. Moreover, they supported only single-band communication, that is, the GSM900 band in [9] and the DCS1800 band in [10]. A GSM transceiver that supports the quad bands (850/900/1800/1900 MHz) [11] was implemented with BiCMOS technology. It employed a direct conversion receiver (DCR) and achieved a considerably high integration level. However, the TX IF filters and loop filters were not integrated. Moreover, its frequency doubler and subharmonic mixers (SHMs), which consume a large bias current, are difficult to be implemented in CMOS technology due to the relatively small transconductance of the MOS transistors. In order to overcome these problems, we have proposed a single-chip CMOS RF transceiver architecture for the four GSM bands (850/900/1800/1900 MHz). The proposed transceiver architecture employs a direct-conversion receiver and an offset PLL transmitter. The rest of this paper is organized as follows. In Section II, we explain the proposed architecture of the GSM quad-band transceivers in CMOS technology. Moreover, we also describe how we obtained an efficient LO frequency plan that is suitable for area reduction, low-power consumption, and generation in the proposed architecture. The major precise circuit blocks of the transceiver are described in Section III. The experimental results of the prototype GSM transceiver are presented in Section IV. Finally, the conclusion is given in Section V. 0018-9200/$20.00 © 2005 IEEE SONG et al.: 0.25- m CMOS QUAD-BAND GSM RF TRANSCEIVER USING AN EFFICIENT LO FREQUENCY PLAN 1095 TABLE I GSM FREQUENCY BANDS II. QUAD-BAND TRANSCEIVER ARCHITECTURE AND ITS LO FREQUENCY PLAN In this section, we propose the architecture for the GSM quadband transceiver that employs a direct-conversion receiver and an offset PLL transmitter. Therefore, we can share the baseband filters among the four frequency bands and image rejection filters are not required in the receiver, which reduces the area of the transceiver. We employ an offset PLL transmitter in the proposed transceiver architecture because it has lower noise and less spurious emission. The LO frequency planning is the key to designing the multiband GSM transceivers because it strongly influences the performance of the transceiver as well as its area and power consumption [12]. What we must consider in the LO frequency planning includes the number of VCOs/PLLs required, the VCO generation, and RF-LO interference. tuning range, precise To reduce the die size of a GSM quad-band transceiver, minimizing the number of VCOs and PLLs is the most important factor because they occupy relatively large areas in the transceiver ICs. In this section, we will also describe how we obtained an efficient frequency plan using direct down conversion for the receiver and offset PLL for the transmitter. Then, we will explain the detailed architecture of the quad-band transceiver based on the proposed frequency plan. Most RF communication systems today employ accurate signals for the complex domain signal processing. Thus, generating the precise signals is a key to making a successful frequency plan, in order to meet the phase error specification for the GSM transceivers. A. Precise Fig. 1. Waveforms of input and I=Q signals generated with frequency dividers. (a) With a divide-by-2 circuit. (b) With a divide-by-4 circuit. signal depends on the duty cycle of the input signal. On the other hand, in the frequency-divide-by-4 method shown in Fig. 1(b), and are rising-edge triggered. Therefore, the both phase accuracy is not affected by the duty cycle of the input signal. Although the divide-by- methods require a higher frequency signal, which can be a disadvantage in a frequency plan, they consume a relatively small current and provide good phase accuracy against the process and frequency variations. We decided to use the divide-by-4 or divide-by-8 circuits to generate signals in the frequency plan in order to meet the precise the phase-error specification for the GSM transceivers. Generation In integrated circuits, there are two common methods for generating signals: using an RC–CR phase shifter or using a divider circuit. The RC–CR phase shifters are more suitable to the frequency planning of the transceivers because they do not translate the frequency at all. However, it is difficult to achieve good matching performance in the RC–CR phase shifters because the absolute values of R and C depend on the process variations. Although the higher order phase shifters can reduce these mismatches substantially [10], they have larger signal attenuation and consume more power. Fig. 1 shows the other method of generating I/Q signals with the divider circuits. In the frequency-divide-by-2 method shown is rising-edge triggered and is fallingin Fig. 1(a), edge triggered. Therefore, the phase accuracy of the quadrature B. How to Obtain an Efficient Frequency Plan In finding an efficient LO frequency plan, we put some constraints that are required to develop a low-power low-cost small form-factor GSM transceiver based on the proposed architecture, as shown in Table II. First, it is very important to minimize the number of VCOs/PLLs required in the transceiver. Note that the number of VCOs required depends on the tuning range of each VCO and that the typical tuning range of an on-chip L–C VCO is less than 20% due to their design margin against the L and C variations. Although the VCOs using a ring oscillator have a wider tuning range, they are rarely used in the transceiver IC due to their large phase noise. is intended to loosen the VCO The constraint for away from pulling and pushing effect by separating 1096 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 TABLE II CONSTRAINTS FOR THE LO FREQUENCY PLAN FOR THE GSM QUAD-BAND TRANSCEIVER ARCHITECTURE THAT EMPLOYS A DIRECT-CONVERSION RECEIVER AND AN OFFSET PLL TRANSMITTER is suitable to the offset PLL transmitter for the quad-band transceiver, which can satisfy the requirement of separating away from in the direct conversion receiver. Note that we do not permit low-side mixing for high bands, to prevent the LO VCO frequency from being too high. For the frequency plan in Fig. 2(a), we can write the following equations: (1) (2) (3) where is the low-band frequency and is the high-band frequency. Equation (3) is the necessary condition to support the quad-band GSM. From (1)–(3), we write (4) To solve (4), , and are assumed as follows: or Fig. 2. LO frequency plans for the transceiver architecture that employs a direct conversion receiver and an offset PLL transmitter. (a) A general frequency plan. (b) Proposed frequency plan. the RF frequency [6], [13], [14]. The constraint for the generation with the divide-by-4 or divide-by-8 circuits is added to meet the tight phase error in the GSM specification because they are more precise and insensitive than the phase shifters, as explained before. Now we explain how we obtained the efficient LO frequency plans that satisfy the constraints in Table II. Fig. 2(a) shows a general frequency plan that employs only one LO VCO/PLL and (5) (6) (7) generation Equations (5)–(7) are the constraints for with the divide-by-4 or divide-by-8 circuits, thus limiting the VCO frequencies and making the task of implementing the dividers easier. By solving (4)–(7) together, we obtained six , and , as shown in Table III. feasible solutions for , and are all fixed, we can calculate the VCO If range and the TX IF range from the frequency band defined in the GSM specification. Among the six solutions, Plan3, in which the VCO and TX IF frequencies are the lowest, is the most suitable to be implemented in integrated circuits because the on-chip L–C VCO has smaller phase noise if its oscillation frequency is low. In addition, its prescaler is easier to be designed and consumes less current for the lower LO frequencies. The TX IF range should not be too high so that the TX IF filters can be easily implemented in the integrated circuits. We adopted the frequency Plan3 shown in Fig. 2(b), which satisfies all the constraints in Table II. C. Quad-Band Frequency Plan Based on the frequency Plan3 in Table III, we describe the detailed frequency plan suitable to the GSM quad-band SONG et al.: 0.25- m CMOS QUAD-BAND GSM RF TRANSCEIVER USING AN EFFICIENT LO FREQUENCY PLAN 1097 TABLE III LO FREQUENCY PLANS THAT SATISFIES THE CONSTRAINTS IN TABLE II Fig. 3. RX block diagram based on the proposed frequency plan. (a) GSM850/EGSM900 bands. (b) DCS1800/PCS1900 bands. the required range of the LO VCO that supports the quad band is from 1390 to 1592 MHz for the receiver. In the TX frequency plan shown in Fig. 4, we used the offset PLL architecture including a TX VCO to reduce the noise in the transmit signal. The TX VCO directly covers the high-band RF and its divide-by-2 signal covers for the low-band RF. Similar to the RX frequency plan, the LO VCO in the TX frequency plan runs at 8/5 of the transmit RF for the of the transmit RF low-band RX (GSM850/EGSM900) and for the high-band RX (DCS1800/PCS1900), as shown in Fig. 4. The quadrature LO2 signals that are generated by divide-by-4 or divide-by-8 circuits are applied to the offset UP mixers. Similarly, an LO VCO can be shared between the low and high bands. Thus, the required tuning range of an LO VCO that supports the quad-band TX is from 1318 to 1528 MHz, which is mostly overlapped with the tuning range of the LO VCO in the receiver. Therefore, we can share an LO VCO between the receiver and the transmitter. Table IV summarizes the tuning ranges of the TX and LO VCOs in the proposed GSM transceiver. Each VCO can be implemented with an on-chip L–C VCO because its tuning range is less than 20%. This frequency plan relaxes the VCO pulling/pushing problems because the LO VCO frequency is either 4/5 of the highband frequency or 8/5 of the low-band frequency. However, it requires four different divider circuits. Because it uses the two different IF frequencies in the transmitter, the IF filters of the TX offset PLL should be designed to select their cut-off frequency according to the target frequency band. D. Quad-Band Transceiver Architecture transceiver. In the low-band RX (GSM850/EGSM900) freof the quency plan shown in Fig. 3(a), the LO VCO runs at RF frequency, and the LO signal for direct down conversion is generated by the high-sided mixing of the signals from the divide-by-2 with the divide-by-8 signals of the LO VCO signals are generated through frequency. Note that the the divide-by-8. For the high-band RX (DCS1800/PCS1900) frequency plan in Fig. 3(b), the LO VCO runs at 4/5 of the signals are generated through the RF frequency and the divide-by-4 of the LO VCO frequency. Note that a single LO VCO in the receiver supports the quad bands by being shared between the low-band and high-band receivers. Consequently, We propose an efficient architecture for the single-chip GSM quad-band transceiver based on the detailed frequency plans, which can be implemented with CMOS technology. As shown in Fig. 5, the proposed architecture integrates most of the building blocks for the quad-band transceiver. The required external components are the RX band-select SAW filters, the matching circuits of the LNAs, and the TX power amplifiers. In the receiver, four separate LNAs are employed to improve the blocking performance for each band. In addition, two separate down-conversion mixers are used: one for the low bands (850/900 MHz) and the other for the high bands (1800/1900 MHz). The baseband circuits are shared for all four 1098 Fig. 4. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 TX block diagram based on the proposed frequency plan. (a) GSM850/EGSM900 bands. (b) DCS1800/PCS1900 bands. TABLE IV VCO TUNING RANGES REQUIRED FOR THE GSM QUAD-BAND TRANSCEIVER BASED ON THE PROPOSED FREQUENCY PLAN bands because their channel spaces are equal to 200 kHz. In the transmitter, the offset PLL is employed to meet the tight GSM spectral mask specifications. The offset PLL transmitter includes the offset UP/DN mixers, IF filters, TX VCO, loop filter, and preamplifiers. Because it employs a single TX VCO, it transmits the VCO signal directly for the high bands and through the divide-by-2 circuit for the low bands. We used the - fractional- synthesizer for the LO PLL, and all the operating modes and options of the transceiver can be set by a 3-wire serial peripheral interface (SPI). SONG et al.: 0.25- m CMOS QUAD-BAND GSM RF TRANSCEIVER USING AN EFFICIENT LO FREQUENCY PLAN Fig. 5. 1099 Block diagram of the quad-band GSM transceiver based on the proposed frequency plan. III. CIRCUIT DESCRIPTIONS A. LNA For each LNA, we used a single-stage differential LNA, as shown in Fig. 6(a), to improve its linearity. The differential LNA was employed to achieve a good IIP2 characteristic, although it requires a large area and consumes more current. We used down-bond wires as series feedback inductors to lower both the noise figure and the input voltage standing wave ratio (VSWR). The load of the LNA is composed of a resonant circuit using spiral inductors, which attenuates the out-of-band blockers. The impedance of the half circuit of its load, shown in Fig. 6(b), can be written as follows: (8) From (8), we can write and as follows: At the frequency of , the load impedance has its min, it is at its maximum value, and, at the frequency of should be designed to be , the receive imum value. band frequency, to achieve maximum LNA gain. We designed to be to prevent out-of-band blockers from being mixed-down with the third harmonics of the LO signal. Fig. 7 shows the simulation result for the PCS1900 LNA. Its power gain is 21 dB at 1960 MHz and its rejection at the third harmonic band (5880 MHz) is about 56 dB. Although this LNA has a better blocking performance, it occupies an area of about 0.3 0.3 mm due to the additional on-chip spiral inductor . B. RX Down-Conversion Mixer The down-conversion mixer, which is a key building block of the RF receiver, has a large influence on the noise figure and linearity of the receiver. The down-conversion mixer we used is shown in Fig. 8, where the NMOS current, , is 3 mA. Each PMOS current source, , reduces the bias current of its correnoise sponding LO switch, which is the main source of the in Gilbert-type mixers [15]. However, reducing the current of the switches too much will result in a severe degradation of conversion gain and linearity. In the mixers with a switch current less than the bias current, a small variation in the bias current can result in a large change in the output voltage. Thus, the output common-mode voltage is very sensitive to device mismatches and process variations. Instead of using the ac couplers, which have a long settling time and occupy a large area, we employed a common-mode feedback circuit with an operational amplifier to overcome these problems [16], as shown in Fig. 8. The simulation results for the down-conversion mixer are shown in Fig. 9. The rms output noise voltage in Fig. 9(b) is 1100 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 Fig. 8. Down-conversion mixer with common-mode feedback (CMFB). Fig. 6. LNA. (a) Schematic. (b) Equivalent circuit for a half circuit of the load. Fig. 7. Simulation result for the PCS1900 LNA. calculated over the frequency range 1–100 kHz. If the of the PMOS load is sufficiently large, the output load impedance is R . Thus, the load impedance is almost independent of the switch and load current. As a result, the conversion gain of the mixer can be maintained even though the switch current is reduced to a certain level. Fig. 9. Simulation results for the down-conversion mixer. (a) Gain and IIP3 versus I . (b) RMS output noise versus I . SONG et al.: 0.25- m CMOS QUAD-BAND GSM RF TRANSCEIVER USING AN EFFICIENT LO FREQUENCY PLAN Fig. 10. 1101 RX baseband block diagram. However, the conversion gain and IIP3 in Fig. 9(a) are seincreases more than verely degraded as the PMOS current 2 mA. There is a tradeoff between noise and linearity, and, thereis selected to be 2 mA, which is fore, the PMOS current near the point where reducing the output noise by increasing the PMOS current more has no further advantage. C. RX Baseband Circuits The block diagram of the RX baseband is shown in Fig. 10. It consists of a PreAGC, four PostAGCs, and three low-pass filters. The overall dynamic range of the RX baseband circuit is 75 dB. In order to loosen the linearity requirement of the baseband circuits, the LNA is designed to have about a 27-dB gain control range. Thus, the total dynamic range of the receiver is about 102 dB. The output of the RX down-conversion mixer is applied to the input of the PreAGC, as in Fig. 10. We allocated a larger area and more current to the PreAGC than the other baseband circuits, in order to allow both high linearity and low noise performance. Three low-pass filters reject the in-band interferers, which are implemented by third-order active-RC Butterworth filters. In the direct-conversion receivers, the dc-offset cancellation is very important. Although the ac couplers are a simple solution, they require a large area and a long settling time. We used the active dc-offset cancellation circuits (DCCs), which are connected to each AGC, as shown in Fig. 10. An AGC cell with the DCC is shown in Fig. 11, where we used MOS capacitors to reduce the area. A dc extractor integrates the offset voltage of the AGC output and the integrated offset voltage is subtracted from the AGC input through a feedback connection. For the AGC circan be written as follows: cuit in Fig. 11(a), the AGC output Fig. 11. VGA with DCC. (a) Schematic. (b) Its frequency response. The transfer function of (10) is drawn in Fig. 11(b). The corner frequency of the high-pass filter can be adjusted by changing the resistance in the dc extractor. D. TX Offset UP/DN Mixers From (9), the transfer function of the AGC can be written as follows: The nonlinear terms of the offset UP mixer will cause spurious emission in the transmit signal. Among them, the spurious tones from the baseband third harmonics are hard to remove because they appear very close to the transmit frequency. Fig. 12 shows the offset UP mixer used in this work, which improves linearity substantially using a gain-boosting operational ampliis a degeneration resistor and the transistors, M1 and fier. M2, operate as source followers. If the gain-boosting circuits are not added to M1 and M2, harmonic terms can appear when the varies due to the insufficient transconductance current of of M1 and M2. If the gain of the operational amplifier is sufficiently large, the differential current of M1 and M2 can be written as follows: (10) Because the signal bandwidth of the IN/INB is less than 100 kHz, it is not difficult to design an operational amplifier with a bandwidth wider than 100 kHz. From the simulation (9) 1102 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 Fig. 14. Simulation result for TX offset PLL: rms phase error and phase noise at 20-MHz offset versus loop bandwidth. Fig. 12. Offset UP mixer with improved linearity. Fig. 15. Microphotograph of the quad-band GSM transceiver. E. Offset PLL Loop Filter Fig. 13. Offset DN mixer with cascode stage. result, the offset UP mixer provides an IIP3 of 12 dBV, which shows an improvement of about 10 dB compared with the UP mixer without the gain boosting circuits. The offset DN mixer translates the VCO frequency into the IF frequency, which is applied to the phase frequency detector (PFD), as shown in Fig. 5. Because it is a relatively high frequency circuit, the signal couplings should be taken into account. Fig. 13 shows the offset DN mixer used in this work. The cascode transistors, M3 and M4, prevent the LO signals from directly coupling to the VCO/VCOB. If the LO signals are coupled to the VCO/VCOB, it will add spurious tones to the transmit signal. According to the simulation results, the cascode stack reduces the coupling from the LO to the VCO by more than 20 dB. The frequency of the Gaussian-filtered minimum shift keying (GMSK) modulated signal is deviated within the range from kHz to kHz according to the conveyed digital data. Thus, the output of the offset UP mixer, which corresponds to the reference input of the PFD, will also be deviated from the center IF frequency. If the bandwidth of the offset PLL is too narrow, the output of the offset PLL cannot track the reference deviation, which can result in a large rms phase error of the transmit signal. Fig. 14 shows the simulation result for the rms phase error along with the phase noise at 20-MHz offset versus the loop bandwidth of the offset PLL. There exists a tradeoff between the rms phase error and the 20-MHz wideband noise [8], [17]. In order to achieve an rms phase error of less than 0.6 and to minimize the wideband noise, we designed the loop bandwidth of the offset PLL to be 933 kHz. In designing the loop parameters of the offset PLL, the division factor should be calculated as 1. Because the VCO frequency is translated to the IF frequency by the offset DN mixer, the frequency deviation of the VCO output is not scaled down at all [18]. SONG et al.: 0.25- m CMOS QUAD-BAND GSM RF TRANSCEIVER USING AN EFFICIENT LO FREQUENCY PLAN Fig. 16. band. 1103 RX noise figure versus frequency. (a) EGSM900 band. (b) PCS1900 Fig. 18. Constellations of the GMSK demodulated signal at the RX output. (a) For the RX input power of 86 dBm. (b) For the RX input power of 102 dBm. 0 Fig. 17. RX IIP3 versus frequency. (a) EGSM900 band. (b) PCS1900 band. IV. EXPERIMENTAL RESULTS The quad-band GSM transceiver described in the previous section was implemented in 0.25- m 1-poly 5-metal CMOS technology, and its microphotograph is shown in Fig. 15. The 0 prototype chip occupies an area of 3.3 3.2 mm including its pads, which was assembled in a 40-pin quad flat no-lead (QFN) package. The RX RF circuits, such as LNAs and down-conversion mixers, are placed in the upper left corner and the RX baseband circuits, such as PGAs and LPFs, in the lower left corner. We allotted a large area to the RX baseband blocks to reduce the noise. The TX offset PLL including the TX VCO is located in the upper right corner and the LO VCO with a - fractional- synthesizer is located in the lower right corner. Their loop filters are integrated using the MOS capacitors. The type of each VCO is an LC oscillator with an external inductor, and its size is about 0.7 0.7 mm . Each VCO consumes about 5 mA. Fig. 16 shows a graph of noise figure versus frequency for the receiver. The measured chip noise figures (NFs) for the EGSM900 and PCS1900 bands are less than 2.9 and 3.4 dB, respectively. The NF variations in a band are related with the SAW filter ripple, impedance matching, and so on. We measured the NF with the inclusion of the external band-select SAW filter. From this, we compensated for the insertion loss of the 1104 Fig. 19. signal. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 Measured rms phase error at the TX output for the GMSK modulated SAW filter in order to calculate the chip NF. Although the insertion loss of the SAW filter at each channel (or frequency) must be strictly compensated for, we used a typical loss in a band for simplicity. Thus, the insertion loss variation of the SAW is included in the NF plot of Fig. 16. The SAW filters used in this work are the EPCOS B7701/B7706/B7716/B7717 components for GSM/EGSM/DCS/PCS, and their typical insertion losses are 2.3/2.6/3.0/2.6 dB, respectively. Fig. 17 shows a graph of IIP3 versus frequency for the receiver. The IIP3 values were measured by the two-tone test. The minimum receiver IIP3 is dBm for the EGSM900 band and dBm for about the PCS1900 band, which satisfies the specifications required for the GSM transceiver. The specifications shown in Fig. 17 were also calculated by assuming that the front-end loss is 4 dB. Fig. 18 shows the constellations of a GMSK demodulated dBm and (b) signal at the RX output for the input of (a) dBm. The measured rms phase errors are 2.9 and 4.6 , respectively, which are sufficiently less than the required rms error of 5 in the GSM specifications [5]. Fig. 19 shows the rms phase error at the TX output for the GMSK modulated signal. According to the experimental results, the rms phase errors for the PCS1900 and EGSM900 bands are 1.7 and 1.4 , respectively, which are also sufficiently smaller than the required RMS phase error of 5 in the GSM specification [5]. The GMSK modulated spectrums at the TX output are shown in Fig. 20, which also meet the GSM spectral mask specifications [5]. The prototype chip consumes about 56 mA in the RX mode and 58 mA in the TX mode at 2.8 V. Specifically, the LO generation circuitry with the exception of the synthesizer consumes about 10 mA. Table V summarizes the performance of the quad-band GSM transceiver. The overall receiver dynamic range is 102 dB. The maximum receiver gain is 107 dB and the minimum gain is 5 dB. For the high bands, the IIP2 performance is not sufficient to pass the AM suppression test. In order to improve the IIP2 at 1800/1900 MHz, we should reduce the mismatches between the differential signal paths, for example, the asymmetry of the PCB lines, the chip layout, and the pin assignment. The TX spectral mask performance at 400 kHz, as shown in Table V, is marginal. Fig. 20. GMSK modulated spectrums at the TX output. (a) EGSM900 band. (b) PCS1900 band. which is due to the nonlinearity of circuits, especially the third harmonics of the offset UP mixer. Thus, the IIP3 of the offset UP mixer should be improved in order to achieve better TX mask performance. We used a - fractional- synthesizer to meet the settling time requirement for the GPRS class 12. The measured RX and TX settling times are less than 200 and 220 s, respectively. Although the frequency plan used in this study has the advantage of reduced area and smaller power consumption, the undesirable mixing products from the LO generator affect the out-of-band blocking performance of the receiver. The front-end SAW filter on the receiver side should have enough selectivity to suppress the input frequency bands corresponding to the mixing terms. In order to improve the blocking characteristics, an L–C tuned amp for the LO buffer or a bandpass filter following the LO generation mixers should be added, which might increase the power consumption. Therefore, there is a tradeoff between performance and power consumption. V. CONCLUSION In this paper, we proposed an efficient frequency plan that is suitable for the GSM quad-band transceiver. We also presented a SONG et al.: 0.25- m CMOS QUAD-BAND GSM RF TRANSCEIVER USING AN EFFICIENT LO FREQUENCY PLAN 1105 TABLE V PERFORMANCE SUMMARY OF THE QUAD-BAND GSM TRANSCEIVER CHIP single-chip 0.25- m CMOS RF transceiver using the proposed frequency plan. The GSM quad-band transceiver includes only one LO VCO with a tuning range from 1318 to 1592 MHz. We used divide-by-4 and divide-by-8 circuits to generate all of the signals, which consume less power and are less sensitive to the process and frequency variations, compared with the phase shifters. Moreover, we selected the LO VCO frequencies to reduce the VCO pulling and pushing effects by separating them away from the RF frequency. According to the measured results, the receiver provides the maximum noise figure of 2.9 dB and the minimum IIP3 of 13.2 dBm for the EGSM band. The transmitter presents an rms phase error of 1.4 , which meets the GSM spectral mask specification. The prototype chip consumes 56 mA in the RX mode and 58 mA in the TX mode at 2.8 V. Thus, we conclude that the proposed GSM transceiver is suitable for low-cost low-power small-form factor solutions. ACKNOWLEDGMENT The authors would like to thank S.-W. Lee and J. Park for their discussion on the transceiver architecture, S. Hong for his helpful comments on the GSM standard, and Y. Ahn for his test equipment setup. REFERENCES [1] A. A. Abidi, “RF CMOS comes of age,” IEEE Microw. Mag., pp. 47–60, Dec. 2003. [2] B. Razavi, “RF CMOS transceivers for cellular telephony,” IEEE Commun. Mag., pp. 144–149, Aug. 2003. [3] [Online]. Available: http://www.gsmworld.com [4] S. Tadjpour, “A 900 MHz dual conversion, low-IF CMOS GSM receiver,” Ph.D. dissertation, Univ. of California, Los Angeles, 2001. ); [5] V8.11.0: Digital Cellular Telecommunications System (Phase Radio Transmission and Reception, Aug. 2001. ETSI TS 100 910. [6] T. D. Stetzler, I. G. Post, J. H. Havens, and M. Koyama, “A 2.7–4.5 V single chip GSM transceiver RF integrated circuit,” IEEE J. Solid-State Circuits, vol. 30, no. 12, pp. 1421–1429, Dec. 1995. [7] C. Marshall et al., “A 2.7 V GSM transceiver IC’s with on-chip filtering,” in ISSCC Dig. Tech. Papers, Feb. 1995, pp. 148–149. [8] T. Yamawaki et al., “A 2.7-V GSM RF transceiver IC,” IEEE J. SolidState Circuits, vol. 32, no. 12, pp. 2089–2096, Dec. 1997. [9] P. Orsatti, F. Piazza, and Q. Huang, “A 20-mA-receive, 55-mA-transmit, single-chip GSM transceiver in 0.25-m CMOS,” IEEE J. Solid-State Circuits, vol. 34, no. 12, pp. 1869–1880, Dec. 1999. [10] M. S. J. Steyaert, J. Janssens, B. De Muer, M. Borremans, and N. Itoh, “A 2-V CMOS cellular transceiver front-end,” IEEE J. Solid-State Circuits, vol. 35, no. 12, pp. 1895–1907, Dec. 2000. [11] R. Magoon, A. Molnar, J. Zachan, G. Hatcher, and W. Rhee, “A single-chip quad-band (850/900/1800/1900 MHz) direct conversion GSM/GPRS RF transceiver with integrated VCO’s and fractional-N synthesizer,” IEEE J. Solid-State Circuits, vol. 37, no. 12, pp. 1710–1720, Dec. 2002. [12] J. Strange and S. Atkinson, “A direct conversion transceiver for multi-band GSM application,” in Proc. IEEE RFIC Symp., Jun. 2000, pp. 25–28. [13] K. Lee et al., “A single-chip 2.4-GHz direct-conversion CMOS receiver for wireless local loop using multiphase reduced frequency conversion technique,” IEEE J. Solid-State Circuits, vol. 36, no. 5, pp. 800–809, May 2001. [14] A. Zolfaghari and B. Razavi, “A low-power 2.4-GHz transmitter/receiver CMOS IC,” IEEE J. Solid-State Circuits, vol. 38, no. 2, pp. 176–183, Feb. 2003. [15] D. Manstretta, R. Castello, and F. Svelto, “Low = noise CMOS active mixers for direct conversion,” IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 48, no. 9, pp. 846–850, Sep. 2001. 2+ 1f 1106 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 5, MAY 2005 [16] J. C. Rudell, J.-J. Ou, T. B. Cho, G. Chien, F. Brianti, J. A. Weldon, and P. R. Gray, “A 1.9-GHz wide-band IF double conversion CMOS receiver for cordless telephone applications,” IEEE J. Solid-State Circuits, vol. 32, no. 12, pp. 2071–2088, Dec. 1997. [17] E. Hegazi and A. A. Abidi, “A 17-mW transmitter and frequency synthesizer for 900-MHz GSM fully integrated in 0.35-m CMOS,” IEEE J. Solid-State Circuits, vol. 38, no. 5, pp. 782–792, May 2003. [18] J.-M. Hsu, “A 0.18-m CMOS offset-PLL upconversion modulation loop IC for DCS1800 transmitter,” IEEE J. Solid-State Circuits, vol. 38, no. 4, pp. 603–613, Apr. 2003. Eunseok Song was born in Korea in 1971. He received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 1996 and 1999, respectively, where he is currently working toward the Ph.D. degree. He has been working on CMOS analog circuit design, and his research interests include CMOS RF circuits and CMOS image sensors. Yido Koo (S’96–M’03) was born in Seoul, Korea. He received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from Seoul National University, Seoul, Korea, in 1996, 1998, and 2003, respectively. His doctoral dissertation includes the design of a fully integrated CMOS frequency synthesizer for CDMA applications. From 2000 to 2002, he developed the frequency synthesizer for CDMA and PHS wireless systems working with GCT Semiconductor, Inc., San Jose, CA, as a part-time Design Engineer. In 2003, after graduation, he joined the same company as a Manager of Analog Division, where he is now involved in the design and implementation of RF transceiver and building blocks for GSM and W-CDMA systems. He is the inventor of two and co-inventor of several U.S. patents. Dr. Koo was the recipient of the 2003 IEEE Best Student Award of the IEEE Solid-State Circuits Society Seoul Chapter. Yeon-Jae Jung was born in Korea in 1974. He received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from Seoul National University, Seoul, Korea, in 1997, 1999, and 2003, respectively. Currently, he is a Design Engineer with GCT Semiconductor, San Jose, CA. His main research interests are in RF and baseband CMOS circuits and system planning for wireless communications. Deok-Hee Lee was born in Korea on May 6, 1977. He received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 2000 and 2002, respectively. He is currently with GCT Semiconductor, Inc., San Jose, CA, where he works on the design and development of integrated CMOS transceivers for GSM and wireless LAN. Sangyoung Chu was born in Korea on August 11, 1973. He received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 1998 and 2000, respectively. In 2000, he joined GCT Semiconductor, Inc., San Jose, CA, where he is currently a Principal Engineer leading the development of wireless communication systems. Soo-Ik Chae (M’87) received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 1976 and 1978, respectively, and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 1987. He was an Instructor with the Electronics Department, Air Force Academy of Korea, Seoul, from 1978 to 1982. He also worked as a Manager of an ASIC Design Group, ZyMOS Corporation, Sunnyvale, CA, from 1987 to 1988 and a General Manager at Daewoo Telecom Company from 1988 to 1990. Since 1990, he has been with Seoul National University, where he is currently a Professor in the School of Electrical Engineering and the Director of the Center of SoC Design Technology. He was the Director of the Inter-University Semiconductor Research Center (ISRC) from 2001 to 2003. His research interests include digital system design, especially programmable DSP design for H.264 and three-dimensional graphics and ultralow-power circuits.