Electrical and Electronics Lab Manual

advertisement

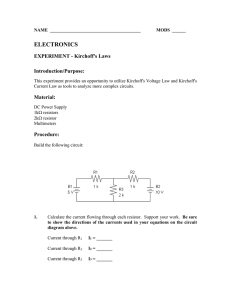

Department of Electronics and Instrumentation Engineering B.E.(CS&E), III Semester (2014-2015) ELECTRICAL AND ELECTRONICS LAB. ELECTRONICS LABORATORY LIST OF EXPERIMENTS 1. (a) VERIFICATION OF KIRCHOFF'S LAWS. (b) VERIFICATION OF OHM'S LAW. 2. (a) CHARACTERISTICS OF SEMI-CONDUCTOR DIODE. (b) CHARACTERISTICS OF ZENER DIODE. 3. CHARACTERISTICS OF TRANSISTOR. 4. CHARACTERISTICS OF FET AND DETERMINATION OF ITS PARAMETERS. 5. VERIFICATION OF SUPERPOSITION THEOREM. 6. RL AND RC TRANSIENTS. 7. HALF WAVE RECTIFIER WITH AND WITHOUT FILTER. 8. FULLWAVE RECTIFIER WITH AND WITHOUT FILTER. EXP NO: DATE : (A) VERIFICATION OF KIRCHOFF’S LAWS (B) VERIFICATION OF OHM’S LAW AIM To verify Kirchoff’s current law, Kirchoff’s voltage law and Ohm’s law experimentally. COMPONENTS REQUIRED Resistor 100Ω, 200Ω Resitor 470Ω Dc power supply Ammeter (0 -50 mA) Voltmeter (0-10V) - 2Nos. - 1No. - 2Nos. - 3Nos. - 3Nos. KIRCHOFF’S CURRENT LAW The sum of the currents entering a junction is equal to the sum of the currents leaving the junction. In other words, if the current flowing towards a junction is taken as positive and the current flowing away from the junction is taken as negative, then this law states that the algebraic sum of all currents at a junction is zero. KIRCHOFF’S VOLTAGE LAW The sum of the potential rises around any closed path in a circuit is equal to the sum of potential drops in it. In other words, the algebraic sum of the potential difference in a closed path is considered to be zero. OHM’S LAW At constant temperature, the current flowing through the conductor is directly proportional to the potential difference applied across its ends. V = I *R PROBLEM Verify Kirchoff’s current law at Junction A and voltage law at loop1 for the circuit shown in Fig. 1 100Ω + 10V - A 200Ω loop1 I1 loop2 470Ω I2 100Ω 200Ω Fig. 1 1 5V + From the circuit, the loop equations are For Loop1 10 = 100I1 + 470(I1 - I2) + 200I1 For Loop2 5 =100I2 + 470(I2 - I1) + 200I2 Simplifying the equations, we get 10 = 770I1 - 470I2 5 = -470I1 + 770I2 Writing the above equations in the form of a matrix, we get 770 − 470 I1 10 = − 470 770 I 2 5 By applying crammer’s rule I1 = ∆1 ∆ ;I2 = 2 ∆ ∆ ∆= 770 − 470 = 372000 − 470 770 ∆1 = 10 − 470 = 10050 5 770 ∆2 = 770 10 = 8550 − 470 5 Now, I1 = 27.02mA; I2 = 22.98mA Here I1 and I2 are the loop currents. From these, the branch currents I3, I4 and I5 are found as follows: I3 = I1 = 27.02 mA I4 = I2 = 22.98 mA I5 = I1 - I2 = 4.04 mA Here at node ‘A’, the current I3 is the entering and I4 & I5 are leaving. I3 = I4 + I5 27.02 mA = 22.98 mA + 4.04 mA Hence KCL is proved theoretically. 2 CIRCUIT DIAGRAM 0-50 mA m.c I3 + mA - 100Ω I4 A 200Ω 0-25 mA m.c + mA I5 + 10V DC - loop2 470Ω loop1 I2 + I1 mA 5V + DC 0-25 mA m.c 100Ω 200Ω Fig. 2 Practical Circuit to verify Kirchoff’s Current Law TABLE 1 Verification of Kirchoff’s Current Law Theoretical(mA) Current through 100Ω Current through 200Ω Current through 470Ω I3 = I1(entering current) I4 = I2 (leaving current) I5 = I1 - I2(leaving current) Practical (mA) 27.02 22.98 4.04 KIRCHOFF’S VOLTAGE LAW The sum of the potential rises around any closed path in a circuit is equal to the sum of potential drops in it. In other words, the algebraic sum of the potential difference in a closed path is considered to be zero. 3 0-10v mc - + V I3 - R4 V1 100Ω R1 + 10V DC - - R2 loop1 200Ω I5 + 470Ω V I1 V2 - 5V + DC 0-10v mc 200Ω R3 R5 V3 100Ω - V + 0-10v m.c Fig. 3 Practical Circuit to verify Kirchoff’s Voltage Law TABLE 2 Verification of Kirchoff’s Voltage Law Element R1 Current through the resistance (mA) I1 = 27.02 Resistance value (Ω) 100 Voltage drop (Volts) Theoretical V1 = 2.702 R2 I1 - I2 = 4.04 470 V2 = 1.899 R3 I1 = 27.02 200 V3 = 5.404 By KVL, Sum of potential rise = Sum of potential drops V = V1 + V2 + V3 10V = 2.702V + 1.899V + 5.404V 10V = 10V Hence KVL is verified. OHM’S LAW From Fig. 3, we measure the drop across the resistor R1 i.e V1 V1 = I1 * R 1 V1 = 27.02 *10−3 *100Ω V1 = 2.702 volts 4 Voltage drop (Volts) Practical TABLE 3 Verification of Ohm’s Law Theoretical value of V1 (V) Experimental value of V1 (V) 2.702 PROCEDURE 1. To verify Kirchoff’s current law, make connections as shown in Fig. 2. 2. Switch on the power supply, note down the ammeter readings and enter in theTable 1. 3. Check whether the algebraic sum of currents is zero. 4. To verify Kirchoff’s voltage law, make connections as shown in Fig. 3. 5. Switch on the power supply, note down the voltmeter readings and enter in the Table 2. 6. Check whether the algebraic sum of voltages is zero. 7. To verify ohm’s current law, make connections shown in Fig. 3. 8. Switch on the power supply, note down V1 and enter it in the Table 3. 9. Compare the experimentally obtained V1 with the theoretical V1. RESULT Thus the given Kirchoff’s current law, Kirchoff’s voltage law and Ohm’s law were verified experimentally. 5 6 EXP NO: DATE : (A) CHARACTERISTICS OF SEMI-CONDUCTOR DIODE AIM To obtain the volt-ampere characteristics of the semi-conductor diode. COMPONENTS REQUIRED DC voltage source – 1 No. Potential divider (1000Ω, 1.2A) – 1 No. Ammeter (0 - 50mA) - 1 No. Voltmeter (0 - 30V) – 1 No. Diode-1 No. THEORY Diode is a two layer uni-directional semi-conductor device. It has two terminals. i.e anode(A) and cathode (K). It will conduct only in the forward bias and not in reverse bias. This means that it provides very low resistance in the forward bias and a very high resistance in the reverse bias. It is used in the rectifier circuit for converting AC to DC. PRECAUTION 1. The potential divider should be kept at minimum potential position at the time of starting the experiment. 2. The junction diode should be connected with proper polarity. 3. Do not give connections when supply is switched ON. 4. Power supply should be switched ON only when the connections in the circuit are satisfied. PROCEDURE (a) Forward Bias 1. Connections are given as per the circuit diagram shown in Fig. 1. 2. By varying the potential divider from zero to maximum, corresponding voltmeter and ammeter readings are noted. 3. The above readings are tabulated and a graph is drawn with anode cathode voltage (VAK) along X-axis and anode current along Y-axis. 4. Find DC forward resistance and AC forward resistance as explained in the model graph. (b) Reverse Bias 1. Connections are given as per the circuit diagram shown in Fig. 2. 2. Vary the potential divider from zero to maximum and note down the corresponding voltmeter and ammeter readings. 3. The above readings are tabulated. 7 CIRCUIT DIAGRAM (0 - 150)mA MC + 10 00Ω , 1.2A − 10V + supply - mA + A IN4007 (0 - 15)V MC V K − Fig. 1 Forward Bias (0 - 150)mA mc 1 0 0 0Ω , 1.2A + 10V Supply _ − + mA + (0 - 15)V mc K V IN4007 − A Fig. 2 Reverse Bias 8 TABULATION Forward Bias VAk (Volts) IA (mA) Reverse Bias VAk (Volts) IA (mA) 9 MODEL GRAPH IA(mA) S B R O DC Forward Re sis tan ce = VAK (volts) P AQ OA OB AC Forward Re sis tan ce = = OQ − OP = OS − OR RESULT The Volt-ampere characteristics of the semi-conductor diode was drawn. The DC and AC Forward resistance were determined. DC Forward resistance of the junction diode = AC Forward resistance of the junction diode = 10 EXP NO: DATE : (B) CHARACTERISTICS OF ZENER DIODE AIM To obtain the volt-ampere characteristics of Zener diode. COMPONENTS REQUIRED DC voltage source – 1 No. Potential divider (3900Ω, 0.3A) – 1 No. Ammeter (0 - 50mA) - 1 No. Voltmeter (0 - 10V) – 1 No. Zener Diode FZ 6.2V -1 No. Resistor-1.5 k ohm-1 N0. SPECIFICATIONS Nominal Zener voltage at IZ Test current IZ Max. Dynamic impedance at IZ Max. Leakage current at VZR Leakage current test voltage VZR Typical temp. Coefficient - 6.2 Volts 20 mA 12 ohms 10 µA 3 Volts + 0.03 % THEORY Zener diode is a two layer bilateral semiconductor device. It is also called as a voltagereference, voltage regulator or breakdown diode. It consists of a PN junction and it is mainly operated in the reverse breakdown region. The break down voltage of a zener diode is set by carefully controlling the doping level during manufacture. It is having two terminals named anode (A) and cathode (K). APPLICATIONS Zener diode has a number of applications, yet the following applications are important. a) As a voltage regulator. b) As a fixed reference voltage in transistor biasing circuits. c) As peak clippers or limiters in wave shaping circuits. PRECAUTIONS 1. The potential divider should be kept at minimum potential position. 2. Zener diode should be connected with proper polarity. PROCEDURE 1. Give connections as per the circuit diagram. 2. Vary the potential divider in steps and note down the corresponding voltmeter and ammeter readings. 11 3. Same procedure is repeated by reverse biasing the zener diode. 4. Tabulate the readings and obtain the volt-ampere characteristics with voltmeter readings along X-axis and ammeter readings along Y-axis. CIRCUIT DIAGRAM 30 V DC + _ SUP PLY (0 - 150)mA mc + mA _ 3900Ω, 0.3A 1.5kΩ 0.5W A + (0 - 15)V mc FZ 6.2V V − Fig. 1 Zener Diode in Forward Bias 12 K TABULATION s FORWARD BIAS Forward Zener voltageVZF in volts Forward Zener current IZF in mA REVERSE BIAS Reverse Zener voltage VZR in Volts 13 Reverse Zener current IZR in mA MODEL GRAPH IZ F(mA) Forward Bias VZ VB (volts) VZ F(volts) Reverse Bias IZ R(mA) RESULT The volt-ampere characteristic of zener diode was obtained. 14 EXP NO: DATE : CHARACTERISTICS OF TRANSISTOR AIM: To determine the (i) Input characteristics and (ii) Output characteristics of the given transistor in common emitter configuration. COMPONENTS REQUIRED D.C Voltmeter (0-10V), (0-1V) D.C Ammeter (0-100mA)&(0-100µA) Rheostat of 3600 ohms and 0.3A Transistor SL 100 (NPN Transistor) DC Power Supply THEORY Input characteristics Fig. 1 shows a transistor in common emitter configuration. From Fig.1 it is clear that IB & VBE are the input quantities and IC & VCE are the output quantities. Study of input quantities keeping VCE as constant gives input characteristics. Output characteristics: Study of output quantities keeping IB as constant gives output characteristics. PROCEDURE Input characteristics 1. Give the connection as shown in Fig.1. 2. Voltage between collector and emitter is fixed say at 1V by varying Rheostat VBE is changed and corresponding IB is noted. 3. Collector to emitter voltage VCE is fixed at say 2V, 3V etc and the above procedure is repeated. 4. A graph between VBE & IB is drawn for various values of VCE. Output Characteristics 1. Give the connection as shown in Fig. 2. 2. The base current is kept at a value say 25µA with the help of the rheostat. The variation of collector current is noted by varying the collector voltage. 3. Repeat the above procedure for IB = 50µA & I = 75µA. 4. A graph between VCE & IC is drawn for various values of IB. 15 CIRCUIT DIAGRAM C 100KΩ B E + (0 -10V) m.c V + VBE V _ _ VCE (0 -10V) m.c (0 -100µA) m.c _ _ 10V RPS + Figure.1 Input Characteristics 16 3600Ω, 0.3A + 3600Ω, 0.3A A TABLE 1 Input Characteristics VCE = VBE (V) Volts IB (µA) V CE = Volts VBE (V) IB (µA) 17 VCE = VBE (V) Volts IB (µA) (0 -10mA) m.c _ A + IC + 100KΩ C B V E _ VCE (0 -10V) m.c SL100 (0 -100µA) m.c _ + 10V RPS Figure.2 Output Characteristics 18 3600Ω, 0.3A IB + 3600Ω, 0.3A A TABLE 2 Output Characteristics IB = VCE (V) µA IC (mA.) IB = µA VCE (V) IC (mA.) 19 IB = VCE (V) µA IC (mA.) MODEL GRAPH VCE1 VCE2 VCE3 IB (µA) IB VBE VBE (volts) Fig. 3 Input Characteristics IC (mA) IB1 VCE IB2 IC IB3 VCE (volts) Fig. 4 Output Characteristics RESULT 1. The study of input characteristics reveals that the transistor exhibits the characteristics of a forward biased emitter to base diode. 2. The study of output characteristics reveals that there are 3 regions of operation of a transistor. They are active, saturation and cur-off regions. In active region, the transistor can be considered to be a linear element. 20 EXP NO: DATE : CHARACTERISTICS OF FET AND DETERMINATION OF ITS PARAMETERS AIM To experimentally obtain the transfer and drain characteristics of the FET and estimate the mutual conductance and drain resistance. COMPONENTS REQUIRED n-channel FET (BFW11)-1 NO. DC Power supply(0-30V)-2 Nos. Potential divider (3600Ω, 0.3A) – 2Nos. Ammeter (0 – 25mA) – 1 No. Voltmeter (0 –30V) – 2 Nos. Resistors(3.3kΩ, 1.5 kΩ)-1No. SPECIFICATIONS - BFW11 Max. Drain source voltage – 30V Max. Gate source voltage – 30V. Total power dissipation – 30mw. Max. Drain current – 40mA. THEORY The JFET is a device in which the flow of current through the conducting channel is controlled by an electric field and hence gains the name JFET. As the current conduction is only by majority carriers (electrons or holes), is said to be a Uni-polar device. Depending on the majority carriers, JFET has been classified into N - channel with electrons as majority carriers, and P channel with holes as majority carriers. The value of drain and Mutual conductance are given as ∆VDS in Ω ∆I D ∆VGS Mutual conductance, g m = in mho ∆I D Drain resistance, rd = There are two types of characteristics namely, 1. Transfer characteristics and 2. Drain characteristics PRECAUTIONS 1. Both the potential dividers should be kept at the minimum potential position at the time of starting the experiment. 2. Biasing polarities should be checked before starting the experiment. 21 CIRCUIT DIAGRAM PROCEDURE Drain characteristics 1. Connections are given as per the circuit diagram shown in Fig.1 2. Keep the gate to source voltage (VGS) constant say 0V, and slowly vary the drain to source voltage (VDS) and note down the corresponding drain current (ID ) 3. The above procedure is repeated for various values of gate to source voltage (VGS). 4. Record the readings in Table 1. 5. A graph is drawn between VDS and ID which gives the drain characteristics. MODEL GRAPH ID(mA) ∆ID VGS1 VGS2 ∆VGS VGS3 VDS (volts) Determination of drain resistance from Drain Characteristics Drain resistance rd = ∆V DS ∆I D VGS constant It is defined as the ratio of change in drain to source voltage (VDS) to change in drain current (ID) at constant gate to source voltage (VGS). 22 TABLE 1 Drain Characteristics VGS = VDS in volts V VGS = ID in msA VDS in volts V ID in mA VGS = VDS in volts V ID in mA Determination of Drain saturation current and Pinch-off voltage 1. Connections are given as per the circuit diagram shown in Fig.1 2. Keep the drain to source voltage (VDS) constant at 0.2 V and slowly vary the gate to source voltage (VGS) and note down the corresponding drain current (ID ). 3. Obtain the ID versus VGS plot.. 4. The gate to source voltage at which the drain current (ID) becomes zero is the pinch-off voltage (VP).The drain current obtained at VGS=0 V is the drain saturation current IDSS. Measured VP (Volts) Measured IDSS TRANSFER CHARACTERISTICS PROCEDURE 1. Connections are given as per the circuit diagram shown in Fig.1. 2. Keep the gate to source voltage (VDS) constant and slowly vary the drain to source voltage. (VGS) and note down the corresponding drain current (ID ). 3. Choose the value of VDS in such a way that for all VGS, the device is in saturation. 4. For different values of VDS repeat the above procedure. 5. Record the readings in Table 2. 6. Draw a graph between VGS and ID keeping the drain voltage VDS constant. 23 TABLE 2 Transfer Characteristics VDS = V VGS in (v) ID in mA VDS = V VGS in (v) ID in mA VDS = VGS in (v) MODEL GRAPH I D(mA) VDS1 VDS2 VDS3 -VGS (v) 24 V ID in mA Determination of mutual conductance of from Transfer Characteristics ID(mA) IDSS VDS ∆ID ∆VGS - VGS (v) VP The mutual conductance is given by g m = ∆I D ∆VGS VDS constant It is defined as the ratio of change in drain current (ID) to change in gate to source voltage (VGS) at constant drain to source voltage (VDS). RESULT The transfer characteristics and drain characteristics were obtained experimentally. The measured values of the parameters are as follows: Parameter Measured Value Unit Pinch-off voltage(VP) Volt Drain saturation current(IDSS) mA Drain resistance(rd) Ohms Mutual conductance(gm) mho 25 26 EXP NO: DATE : VERIFICATION OF SUPERPOSITION THEOREM AIM To obtain the current through the load resistor RL using superposition theorem theoretically and experimentally for the given circuit. THEOREM The current through, or voltage across, an element in a linear bilateral network is equal to the algebraic sum of the currents or voltages produced independently by each source. THEORITICAL DETERMINATION OF IL Fig. 2 shows the given circuit considering the effect of E1 (30V source) To determine the current through RL (1K) resistor i.e. IL1 when E1 is present: The total resistance of the network as seen by the source RT1 = R1 + (R2 ׀׀RL) = 539.72 Ω The total current drawn by the network from the source IT1 = E1/RT1 = 55mA. Applying current divider rule, I2 = [R2/ (R2 + RL)] IT1 = 17.58mA = IL1 Figure 3 shows the given circuit considering the effect of E2 (10 V) source. To determine the current through RL (1K) resistor i.e. IL2 when E2 is present: The total resistance of the network as seen by the source RT2= R2 + (R1 ׀׀RL) = 650Ω The total current drawn by the network from the source IT2= E2/RT2= 15.3mA. Applying current divider rule, I2 = [R1/ (R1 + RL) ] IT2 = 2.75mA = IL2 Total current through RL, IL = IL1 + IL2(Since IL1 and IL2 flow in the same direction) = 20.33mA. 27 R2 = 470Ω R1 = 220Ω + E1 30V - + E2 - 10V RL = 1KΩ Fig. 1 Given circuit R2 = 470Ω R1 = 220Ω IT 1 I1 I2 + E1 30V - RT1 RL = 1KΩ Fig. 2 Considering the effect of E1 (30 V) source R2 = 470Ω R1 = 220Ω I1 I2 IT 2 RL = 1KΩ RT 2 Fig. 3 Considering the effect of E2 (10 V) source 28 + E2 10V - R2 = 470Ω R1 = 220Ω + E1 30V RL = 1KΩ - + (0-25mA)mc A - Fig. 4 Connection diagram for determination of IL1 R2 = 470Ω R1 = 220Ω + E2 10V - RL = 1KΩ + (0-25mA)mc A - Fig. 5 Connection diagram for determination of IL2 R2 = 470Ω R1 = 220Ω + E1 30V - + RL = 1KΩ + A (0-50mA)mc - Fig. 6 Connection diagram for determination of IL 29 E2 - 10V EXPERIMENTAL PROCEDURE FOR PRACTICAL DETERMINATION OF IL 1 2 3 Make connections as given in Fig 4, 5&6. After connections are verified, switch on the power supply and tabulate the IL1, IL2 and IL readings shown by the ammeters. Compare with the theoretical values. TABLE Verification of Superposition Theorem Current Theoretical value(mA) IL1 17.58 IL2 2.75 IL=IL1+IL2 20.33 Practical value(mA) RESULT The value of the current through RL determined using superposition theorem Theoretically = 20.33 mA Practically = mA 30 EXP NO: DATE : TRANSIENTS IN RL AND RC CIRCUITS AIM: To obtain the transient response of RL and RC circuits (I order) and to experimentally determine the time constants. THEORY: (RL CIRCUIT) Consider the Fig. (1) Applying KVL around the closed loop, Ri + L di/dt = Vi i(t) is the loop current Taking Laplace transform R I(s) +Ls I(s) = Vi/s Assume Vi = V U(t) Where U(t) is a step function. [R + Ls] I(s) = Vi/s Taking Partial Fraction, Taking Inverse Laplace Transform 31 But from the circuit, the voltage across R is VR = R*I = V When time t ∞ we have VR = V Hence we have VR = V When t = L/R we have V = V = 0.632 V The time constant of RL circuit is τ = L/R sec. from the transient response the time constant is the time taken to reach 63.2 % of maximum value. Hints • • • • • • • Remember that the order of components is arbitrary in a series circuit Capacitor voltage cannot change instantaneously Inductor current cannot change instantaneously An ideal unit step is zero volts until time zero whereas it instantaneously jumps to one volt To find the voltage transient equation for a resistor in a RC or RL circuit one must only subtract the capacitor or inductor voltage transient equation from that of the unit step [ Don’t forget to take into account the function generator’s output impedance ] A real inductor has both resistive and inductive components. Writing a voltage transient equation for a real inductor requires adding these two components together. [ Equations for VL assume ideal inductor, thus the value of the inductor’s resistance must be multiplied by the inductors current and must be added to VL to find the real inductor’s voltage transient equation ] The ideal inductor’s voltage at t=0+ will not be 0 PROCEDURE: 1. 2. 3. 4. 5. 6. 7. 8. Connect up the RL circuit as shown in figure 1. A square wave signal with 2 VPP and 50 Hz is given to the RL circuit. Connect the CRO across the Resistance. Adjust the CRO setting to obtain the waveform. Trace the voltage waveform, which is a rising transient. Calculate the time constant as time required for the response to reach 0.632 of maximum value. Compare this value of time constant with theoretically calculated value. Repeat the above steps for various values of resistance. Enter your observation and calculated results in Table1. 32 Figure.1 RL Circuit Figure.2. Voltage across the Resistor Table: 1. RL CICUIT Time Constant (L/R) (ms) R (Ω) L (H) 1000 0.2 0.2 1000 0.4 0.4 2000 0.4 0.2 Theoretical 33 Practical THEORY: (RC CIRCUIT) Consider the fig. (3) Applying KVL around the closed loop, Let R I(s) +Ls I(s) = Vi/s Assume Vi = V U(t) Where U(t) is a step function. Taking Laplace transform, Where K is the integral constant Initial Capacitor Voltage VC=0 0 = -V + K K=V But the voltage across the capacitor increases exponentially. 34 At time t=RC Therefore time constant maximum voltage applied. τ is the time taken for the capacitor voltage to reach 63.2% of the PROCEDURE: 1. 2. 3. 4. 5. 6. 7. 8. Connect up the RC circuit as shown in figure 3. A square wave signal with 2 VPP and 50 Hz is given to the RC circuit. Connect the CRO across the Resistance. Adjust the CRO setting to obtain the waveform. Trace the voltage waveform, which is a rising transient. Calculate the time constant as time required for the response to reach 0.632 of maximum value. Compare this value of time constant with theoretically calculated value. Repeat the above steps for various values of resistance. Enter your observation and calculated results in Table 2. 35 Figure.3 RC Circuit Figure.4 Voltage across the Capacitor Table: 2. RC CICUIT Time Constant (RC) (ms) R (Ω) C (µ F) 1000 0.1 0.1 1000 0.2 0.2 2000 0.2 0.4 Theoretical Practical RESULT: The transient response of RL and RC circuits was studied and the theoretically calculated and practically obtained values of time constant were verified. 36 EXP NO: DATE : HALF WAVE RECTIFIER WITH AND WITHOUT FILTER AIM To construct the half wave rectifier using IN4007 semiconductor diode and to find its performance curve. COMPONENTS REQUIRED Diode IN4007 Transformer (230 /12-0-12V) Resistor – 1K ohms Capacitor – 100 Micro Fared, 50 V PRECAUTIONS i. The ratings of the diode 1N4007 should not be exceeded. ii. Ranges and polarity of the meters must be checked before switching on the supply. THEORY In half wave rectifier, the diode is forward biased only during the positive half cycle. During the negative half cycle it is reverse biased. Hence the output voltage exists only during the positive half cycle. The ripple voltage will be same as the supply frequency and the ripple voltage will be more compared with other rectifier circuits. The output of the rectifier is a pulsating dc. The ac component of a rectifier output can be smoothed out or filtered by using a suitable circuit. Such a circuit is called a filter circuit. The Fig. 2 shows a half wave rectifier circuit with a single capacitor filter. During the positive half of the input the capacitor gets charged in the time interval between A and B. when the supply ac voltage falls below the dc voltage on the capacitor, the diode ceases to charge the capacitor. But the load current continuous because the filter capacitor discharges through the load. This discharge continuous up to the point C when the increasing supply voltage exceeds the capacitor voltage. The capacitor then starts charging. The above process repeats. The peak inverse voltage is nearly double the peak voltage Vm of the ac supply. 37 CIRCUIT DIAGRAM Fig. 1 Half Wave Rectifier without Filter Fig. 2 Half wave rectifier with filter 38 MODEL WAVEFORM Fig.3 The load voltage falls from B to C and again D to E and so on at rate determined by the time constant of the load resistance RL and filter capacitance C i.e. by C*RL. The diode recharges the capacitor from the point A to B, from C to D and so on. The load voltage waveform is therefore the line ABCDEF. PROCEDURE i. Connections are made as per circuit diagram. ii. Observing the precautions the power is switched ON. iii. Trace the waveforms using CRO and write your inference. RESULT The half wave rectifier using 1N4007 is constructed and performance with and without filter is verified. 39 40 EXP NO: DATE : FULLWAVE RECTIFIER WITH AND WITHOUT FILTER AIM To construct the full wave rectifiers using IN 4007 semiconductor diode and to find its performance curves. COMPONENTS REQUIRED Diode IN4007 Capacitor – 100 µf Transformer 230/ 12-0-12 Resistor THEORY During the positive half cycle of the AC supply if the top end of the transformer secondary becomes positive and the bottom end becomes negative, the voltages on the anode and cathode of four diodes are i. Anode of diode D2 is positive with respective to cathode ii. Anode of D4 is positive with respect to cathode iii. Anode of D1 is negative with respect to cathode iv. Anode of D3 is negative with respect to cathode The diode, which has its anode positive with respect to cathode, is forward biased. Therefore only diodes D2 and D4 will conduct. These two diodes will be in series through load. During the negative half cycle of the AC supply if the top end of the transformer secondary becomes negative and the bottom end becomes positive, the voltages on the anode and cathode of four diodes are i. Anode of diode D1 is positive with respective to cathode ii. Anode of diode D3 is positive with respect to cathode iii. Anode of diode D2 is negative with respect to cathode iv. Anode of diode D4 is negative with respect to cathode The diode, which has its anode positive with respect to cathode, is forward biased. Therefore only diodes D1 and D3 will conduct. These two diodes will be in series through load. 41 CIRCUIT DIAGRAM Fig. 1 Full Wave Rectifier without Filter Fig. 2 Full Wave Rectifier with Filter 42 MODEL WAVEFORM Fig.3 ripplevoltage DCvoltage rmsvalue of AC components = DC value of wave Vrms γ = Vdc Ripple factor = = i = Irms Idc Im π + Im 2 Im 2 Im sin wt − cos 2 wt − cos 4 wt 2 3π 15π or I = Idc +Ir Idc = Ir= Im π Im 2 Im 2 Im sin wt − cos 2wt − cos 4wt 2 3π 15π Irms2 = Idc2+ Irms2 γ = Vrms = Vdc Irms 2 −1 Idc2 43 PRECAUTIONS i. The polarity of electrolytic capacitor should be properly checked before switching on the supply. ii. The ratings of the devices used should not be exceeded. PROCEDURE i. Connections are given as per the circuit diagram shown in Fig 1 & 2. ii. Observing the precautions before switch on the power supply. iii. Trace the waveforms using CRO and write your inference comparing with Fig. 3 RESULT The Full wave rectifier using 1N4007 is constructed and performance with and without filter is verified. 44