ADI template color

advertisement

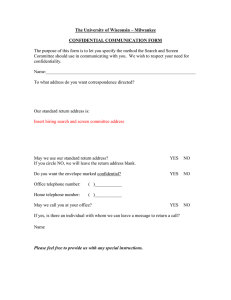

The World Leader in High Performance Signal Processing Solutions Lead Frame Package Design flow using CDS Electronics Packaging Designer (EPD) and Cadence Chip Package Design tools 1—Analog Devices Confidential Information— Take away from this paper CAD Design Software’s - Electronics Packaging Designer (EPD) provides the means to bring the lead frame packages into Cadence System in Package (SIP) tools. SIP tools are integrated with various EM field solvers which provide designers the flexibility to run analysis on an entire package design. Potential solution for connectivity management. Empowers 2 the designer to run the analysis on her/his own. —Analog Devices Confidential Information— SiP Design Flow Allegro Librarian Expert (PDV) SiP RF Layout Die.txt file Back annotation Package layout Symbol EPD Automatic Test-bench Generation NetlistFiles Allegro Librarian Expert Allegro Design Entry HDL (PDV) chip Allegro AMS Simulator PSpice Co-Design Die Virtuoso Layout Chip Top SiP RF Architect Logical Design Die.txt Agilent,Sigrity Virtuoso Platform Allegro Platform 3 Physical Design Package Design IC Design 3rd Party Electronic Package Designer (EPD) EPD is from the third party vendor CAD Design Software. EPD is built on AutoCAD tool; it adds intelligence to the package by adding the pin numbers on the package, tack points for wire bond connections and via-type connections at the Gull wings. The Gull wings connect to the PCB substrate. EPD converts the AutoCAD .dxf file as an input and translates, and instantiates it in a SIP database. The intelligence built on the lead frame package by EPD facilitates integration with system level electrical simulation tools. 4 —Analog Devices Confidential Information— The EPD software is built on AutoCAD tools. It adds extra menu options to the AutoCAD interface; for the recognition and manipulation of package input files. CDS Menu is added to the AutoCAD menus and contains commands to process Lead Frame Designs 5 —Analog Devices Confidential Information— User interface to select an existing technology file built on Custom Environment and Default Design Settings …. The .TCH or ‘Technology File’ contains default settings that can be shared with other users. After initial setup, the New Design Environment and Settings can be saved to a configuration file to be used again. 6 —Analog Devices Confidential Information— Create or Modify a Technology file. Set the Environment for Measurement Units, Design type, number of Layers and the Material Stack-up. Setting the Material Stack-up is used when Describing the Level Thickness, and Material Type that will be used in Cadence. Built-in and Custom Material Types are available. 7 —Analog Devices Confidential Information— Once the settings with units, material stack-up, thickness and tolerance is captured the following package drawing will be loaded into the Design environment. AutoCAD line or Polylines were used in the DXF to draft the design. Using Automatic the EPD tools, the design is first cleaned up and the polylines will be ‘Joined’ and ‘Closed’. Lead Frame Intelligence software can now analyze the drawing to make intelligent for processing and also make ready for Export to Cadence. 8 —Analog Devices Confidential Information— After the cleanup (Join and Closed polylines) and intelligizing, the package name and pin numbers are assigned. By specifying which entities are to be assigned as Metal, Nets, lead assignments etc, the LFINTEL command will block and create the Lead Tips and Paddels. 9 —Analog Devices Confidential Information— The tack points are added for the wire bond attachments from the die to the package Single or Multiple Tack points can be automatically added to the Intelligent Lead Tips. Additional points may be added manually. 10 —Analog Devices Confidential Information— Translation of the Lead Frame Package and instantiation in a SIP database Using the EPD2SKL conversion utility the Lead frame package is converted to the SKILL file. So <Package_name>.il and EPD2SKL.scr files are available to play. The 11 lead frame Package appears in the SIP layout XL —Analog Devices Confidential Information— Lead Frame Package imported into SIP. The gull wings at the backend of the Lead connects to the substrate The pin numbers are highlighted in red. The tack points at end of the leads for wirebond connection from the die. —Analog Devices Confidential Information— Lead Frame Package with the die placed in the package Die Placed in newly imported Lead Frame 13 —Analog Devices Confidential Information— Lead frame Package with the die and the wire bonds attached. Once the Package is in SIP, bring the Die from the schematic front end, place the die in the package and start wire bonding to the package. 14 —Analog Devices Confidential Information— Connectivity (Method 1) The netlist file is generated from SIP. For smaller Packages the net names for the wirebonds and the connectivity between the die and the package can be checked. 15 —Analog Devices Confidential Information— Connectivity (Method 2) Schematic symbol for the die and the package. Die and the Package in SIP with rats-nest attached. 16 —Analog Devices Confidential Information— Connectivity Driven Bonding diagram 17 —Analog Devices Confidential Information— 3D Viewer in SIP 18 —Analog Devices Confidential Information— Assembly rules in SIP 19 —Analog Devices Confidential Information— Constraint Manager in SIP 20 —Analog Devices Confidential Information— Reports generated in SIP 21 —Analog Devices Confidential Information— Export to Agilent ADS Momentum and Sigrity tools 22 —Analog Devices Confidential Information— Lead Frame Package in ADS Momentum Cookie cutter section of the package in ADS. 23 Full package in ADS —Analog Devices Confidential Information— Summarize advantages of bringing Leadframe Package in SIP Connectivity management for the Die and the package. Ability to generate the connectivity driven bonding diagram. 3D capability enhances the view of wire loops, vertical and horizontal separations of wire bonds. Access to assembly rules checker with about 40 assembly rule checks Wire bond reporting with Net Name, Pin numbers, Finger Name, wire angle etc Robust constraint management tool for all physical and spacing constraints Ability to export the Die and the Package data to Simulation tools 24 —Analog Devices Confidential Information— Conclusion The Sub-Contractors changing the design on is a biggest issue at present which can be avoided if we have greater control and verify everything at our end, before it goes to the sub-contractor This solution gives ADI greater control of the design database from early design exploration, through physical implementation to functional verification - by providing access to connectivity management, constraint management, simulation tools, and assembly rules checks. The control over design database is extremely important through out the design cycle to avoid many iterations with the Sub-Contractors —Analog Devices Confidential Information— Conclusion Continued… The entire design process flow is less error prone due to the efficiency gained in this solution. This solution not ONLY offers greater control of the design database to the business units/product lines, it also considerably reduces design cycle time, improves efficiency and overall product delivery to the ADI customer; thereby improving the Time to Market. —Analog Devices Confidential Information—