EE 340 Electronic Devices - Course Outline Lec A3 Fall 2010

U NIVERSITY OF A LBERTA , E LECTRICAL AND C OMPUTER E NGINEERING

EE 340 Electronic Devices - Course Outline

Lec A3 Fall 2010 web page : www.ece.ualberta.ca/~decorby/ee340.htm

1. Class Schedule

Lec A3: M W F 1200-1250, room : NRE2 001.

Sem E3: Tuesday 1300-1350, room : ETLE2 001.

Note: As always, please ensure that your registration is correct, and that you attend the lecture, seminar, and lab sections for which you are registered. Also, ensure that you have received credit for any prerequisite courses (i.e. EE250).

2. Professor Contact Information

Ray DeCorby

W6-035 ECERF

492-5585 decorby@ece.ualberta.ca

Office hours (by appointment)

I am glad to answer brief questions by email (please put ‘ee340’ somewhere in the subject line of the email). If you want to meet in person, please email with 2-3 possible timeslots and I will respond promptly.

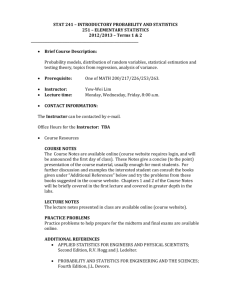

3. Course Content

Calendar Description

EE 340 Electronic Devices

*4.3 (fi 6) (first term, 3-1s-3/2). PN junction semiconductor basics, charge flow and diode equation. Zener diodes. BJT and MOSFET devices and operating regions. Amplifier basics: biasing, gain, input and output resistance, analysis and design. Large signal effects. Differential amplifiers. Prerequisite: E E 250.

Course Objectives

1.

A review of diodes, introduced in EE250. An introduction to some new circuits based on these elements.

2.

An introduction to the analysis of circuits containing nonlinear elements.

3.

An introduction to semiconductor physics and p-n junctions (semiconductor diodes are essentially p-n junctions).

4.

An introduction to transistors, 3 terminal devices in which a voltage at one terminal controls the flow of current between the other two terminals. This relatively humble device (i.e. the transistor) can be employed as an amplifier and as a switch, and is the principle building block for all of modern electronics. There are two main classes of transistors, and we will introduce both in EE340. The bipolar junction transistor (BJT) is based on a pair of back-to-back p-n junctions. In the field effect transistor (FET), the voltage at one terminal controls the resistance (conductance) between the other two terminals.

5.

An introduction to differential amplifiers , which are constructed using two transistors in a balanced circuit configuration. In one sense, this is the first time we look ‘under the hood’ of the op amp .

Page 1 of 4

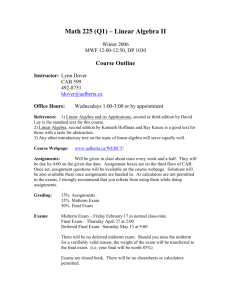

Approximate Lecture Timeline (see web page for more detailed timeline)

Concepts

1-2 Basics of diodes

2-3 Semiconductor physics and p-n junctions

Diode models, breakdown and Zener diodes, analysis of simple circuits containing diodes

Semiconductors, electrons and holes, doping of semiconductors, drift and diffusion, the p-n junction, another look at the diode models transistors (BJTs) transistors (FETs)

Basic structure and physics, modes of operation, npn and pnp transistors, i-v characteristics, BJT as an amplifier and as a switch, small and large signal models

Enhancement- and depletion-type MOSFETs, basic structure and physics, i-v characteristics, FET as an amplifier and as a switch, digital logic based on FETs, integrated circuits

FET differential pair, differential amplifiers with active loads 11-12 Differential amplifiers

Lectures and notes

1.

Lectures will be a combination of handouts and on-board notes. The handout parts (only) will be posted on the web page. A table on the web page correlates the lecture notes with sections in the textbook.

2.

Ideally, you should read 1-2 lectures ahead (i.e. read the associated sections in Sedra/Smith).

Handouts for a given lecture will be distributed at the beginning of that lecture, and then posted on the web page afterwards.

Seminars

Seminars will begin Tues. Sep. 14. The seminars will be a mixture of worked examples and practice problems.

Course Coordination (between sections)

There are 3 sections of EE340 in fall term 2010. In order to ensure consistency (in topics covered, course objectives, etc.), the instructors meet regularly. However, the coverage is not identical between sections, because each instructor brings his or her own particular experience to the task of teaching. We will not be using common lecture notes, assignments, or exams between sections. For this reason, it is very important that you attend the lectures and seminars for which you are registered. Students registered in this section

(lecture A3, seminar E3) will write my midterm and final exams, which will be based on the assignments and lecture notes that I provide.

4. Textbook

A.S. Sedra and K.C. Smith, Microelectronic Circuits, 6 th

ed., Oxford University Press (2010).

In EE340, we use parts of chapters 1 to 8. The problem set questions will be taken primarily from this textbook. Sedra/Smith is also used in EE350 at present, and is a valuable reference if you plan to take advanced courses or work in electronics (or in electrical and computer engineering, in general).

Note: please consider chapters 1-2 to be a reading assignment. Those chapters provide a good review of various topics from 2 nd

year.

5. Design Labs homepage for labs : www.ece.ualberta.ca/~ee340

Lab instructors : Ashok Masilamani ( ashok.prabhu@ualberta.ca

)

Rasoul Milasi ( milasi@ualberta.ca

)

Ziaur Rahman ( ziaur@ualberta.ca

)

Page 2 of 4

Note: The lab instructors are your primary point of contact for questions related to the lab . They will be assisted during the lab periods by a group of teaching assistants.

The term is divided into 2 principle design and implementation tasks: i.

Regulated DC power supply (2 lab periods). This lab requires knowledge about diodes and transformers, and involves mainly basic circuit analysis. ii.

Audio amplifier, powered by the power supply from the first task (3 lab periods). This lab requires knowledge about transistors, and involves a bit more signal analysis.

Some key points regarding the labs are: i.

Introduction to the lab sessions are scheduled the week of Sep. 13 to Sep. 17. See the lab web site for details. ii.

iii.

The manual for the labs is available immediately (EE Club). Please obtain it as soon as possible, as some preparatory work is required prior to your first lab period.

The labs require occasional bits of knowledge that are not provided in lectures. This is (by design) a chance for you to exercise your research skills; use your 2 nd

year notes, use the textbook. Ask the lab instructors if you are stuck and need hints.

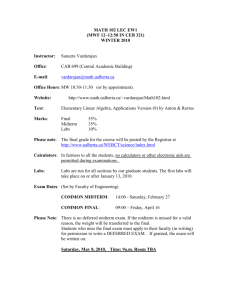

6. Marks and Grading

Midterm (Fri., Oct. 29) 30%

*You will be given both assignments (with due dates and to be marked) and problem sets (not to be handed in); each will be marked clearly as one or the other. Solutions will be posted on the web page.

Grading details i.

Letter grades will be assigned based on the raw marks outlined above. Raw marks will be converted to grades using the standard University of Alberta historical grade distributions as a guideline. ii.

To pass EE340, you must complete both labs and attain a cumulative lab mark of 50%. iii.

I will not fail anyone who does the following: completes all required exams (subject to valid excusal, discussed below), completes both labs and receives an overall grade of at least 50% on the labs, and receives a cumulative raw mark (for the overall course) of 50% or better.

Note: depending on the distribution of the class, you might pass with even lower cumulative score, but that can’t be guaranteed.

7. Exam Details

Midterm: 50 minute exam during scheduled lecture time on Fri. Oct. 29.

Final: As scheduled by the Registrar’s office.

Both exams will be closed book, and have a mixture of multiple choice, short answer, and short numerical questions.

Formula sheets

You will be allowed to bring your own formula sheets into the exams. I will set some limits on the length, etc. Details will be provided in lectures and on the web site prior to the exams.

Policies on Missed Examinations (see Section 23.4(3) of the University of Alberta Calendar)

Deferred examinations will be granted only for students with an acceptable excuse (see Section 23.5 of the

University of Alberta calendar). In such cases:

Missed midterm exam - students with valid excuse will be granted a waiver and the 30% raw marks from the midterm will be tacked on to the final exam.

Page 3 of 4

Missed final exam - students with valid excuse will write a deferred exam, with time and location to be determined by the Instructor in consultation with the department of Electrical and Computer

Engineering.

8. Miscellaneous

Code of Student Behavior and Academic Integrity

1.

Please refer to Section 26 of the University of Alberta Calendar for current policies on student misconduct and disciplinary measures.

2.

The University of Alberta is committed to the highest standards of academic integrity and honesty.

Students are expected to be familiar with these standards regarding academic honesty and to uphold the policies of the University in this respect. Students are particularly urged to familiarize themselves with the provisions of the Code of Student Behaviour (online at www.ualberta.ca/secretariat/appeals.htm

) and avoid any behaviour which could potentially result in suspicions of cheating, plagiarism, misrepresentation of facts and/or participation in an offence.

Academic dishonesty is a serious offence and can result in suspension or expulsion from the

University.

Calculator Policy

Make sure you are familiar with the Faculty of Engineering’s policy on calculators allowed in examinations

(see www.engineering.ualberta.ca/calculator.cfm

). Any approved programmable or non-programmable calculator is permitted in my exams.

Course Outline Policies

Policy about course outlines can be found in Section 23.4(2) of the University Calendar.

Page 4 of 4