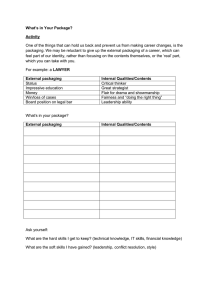

Packaging challenges

advertisement

On the Horizon: Semiconductor Packaging Trends, Challenges and Innovations Dr. Mahadevan "Devan" Iyer Director of WW SC Packaging Texas Instruments Outline • Semiconductors are at the center of a new era • Packaging’s role in product differentiation • Packaging trends and challenges • Emerging low power applications TI Information: Selective Disclosure Semiconductors enable great new products Industrial Motor Control, ATE & Automation Automotive Entertainment, NAV & Vision Medical Electronics Digital Cameras & Camcorders Communication Peripherals IP Phones, PoE & WAPs Growing Internet of Things requires personalization, connectivity Digital Radio & Audio Communication Infrastructure Gateway, Router & Switch TI Information: Selective Disclosure Multimedia Players Mobile Phones Computing TV &STB Video Conferencing & Surveillance We are at the center of a new era Total SC Market Cell phone Analog & Embedded 10 devices: 1 person Processing $1000B CD Personal Computers $100B Microprocessor Minicomputer $10B TTL/Logic Quality of Life Transportation $1B multimedia appliance Mainframe Transistors • Auto electronic power steering • Smart cars • Automatic parking, pilot 1960s TI Information: Selective Disclosure • • • • digital entertainment 1 device: 1 person 1 device: hundreds of people Security Education 1 device: thousands of people Smart houses Remote/home healthcare Wireless connectivity Lower cost/higher feature 1970s mobile phones 1980s • Health monitoring connection • Remote learning to home security • Mobile access to Web • Electronics that “know” the user • Enhanced use of video 1990scameras 2000s 2010s • Intelligent Analog and embedded processing are key drivers New solutions to old applications TI Information: Selective Disclosure New applications New markets Packaging enables convergence of products Intelligent and Autonomous Cars System Integration Needs Integration and Miniaturization enabling systems Smart Phones & Mobile Internet Devices Lab on Chip TI Information: Selective Disclosure Portable Medical Imaging Devices Packaging technology trends reflect applications and end equipments Sub Systems Integration Hi-Perf BGA HiCTE Ceramic Primary Package Platforms Hi Perf PGA FC BGA POP2 SIP BGA FC SiP/POP2 MCM 1 0 0 ’ s Passives Integration FC CSP/POP ML-CSP PGA BGA 1ML-CSP TSV POP1 QFN QFP Chip-on-MEMs MRQFN SO TQFP PLCC F2F SD/MCM QFN FC QFN (HoTRoD) SON WSP TAB HTQFP RFID Enabling technologies System applications DIP Embedded Si Embedded Si FC CSP DIP, PGA, PLCC, QFP SMT TI Information: Selective Disclosure BGA, u*BGA, CSP, FC BGA Bump, Flip Chip interconnect Thermal management 1990 2000 Stacking die, Wafer thinning Au-stud FC, POP, FC CSP, WSP, SON, QFN Embedded Si, Face-to-Face interconnect, bio-compatible Materials& packaging , ultra-thin, Thru Si via, substrateless pkg 2010 2020 Thin is in SOIC QFN 1.75 mm 1 mm PicoStar U*CSP 1 mm 1.2 mm 0.4/0.3 mm 0.6/0.5 mm MicroStar TSSOP TWCSP WCSP (NanoStar) 0.15/0.1 mm 0.45mm Thin QFN 0.8 mm PicoStar-2G X-QFN 0.075mm 0.4 mm Invisible to naked eye ~0.04 mm TI Information: Selective Disclosure Package family proliferation Each package type has a “sweet spot” combination of cost, performance, form factor and reliability, driven by: • • • • • • • • • Cost Electrical speed, power distribution and noise immunity Power dissipation Thickness, weight, PCB area consumption Board level reliability (BLR, drop) Environmental reliability Technical maturity vs. risk in high-volume manufacturing Testability Compatibility with Si process TI Information: Selective Disclosure Packaging challenges: Materials & assembly MC, D/A, LF • Low stress M/C & D/A, right adhesion promoters for LF & MC, Surface finishes of LF Underfills • Low stress underfills to support finer pitch bumps. • Right flow of properties to meet high through put requirements in manufacturing, CTE, Tg & Modulus selection for FC bonding Substrates Interconnect & assembly TI Information: Selective Disclosure • Cost effective high yielding organic substrates with finer LW/LS. • Coreless substrates to support advanced 3D packages • Finer pitch interconnections (Finer pitch FC, Solder Bump FC, Au & Cu wire) • High accuracy, high throughput finer pitch FC bonding Role of IC package materials Electrical Interconnection Structure Indirect Materials Supporting IC package materials must: Be cost neutral - Be electrically invisible - Provide thermal management - Enable device integration Processing Heat Dissipation Reliability Device Protection Performance Devices There is increasing pressure for package materials to meet these requirements in performance applications TI Information: Selective Disclosure Market demands • 3D integration in Power Packaging is a critical element to creating a strong value proposition Cost − Reduced parasitics and noise − Improved power density and thermals − Significant ease of use − Superior solution reliability and cost Reliability Ease of Use Power Density • Future integration − High voltage Thermal Performance − Isolation Electrical Performance − High accuracy current sensing − Integrated magnetics Increased functionality Power packaging and integration plays an increasingly important role. 12 Every application needs power Power management optimizes system performance: efficiency, responsiveness and reliability TI Information: Selective Disclosure TI: Power management for any application Portable Power Conversion • Power converters, backlighting, PMICs, power for power amplifiers • Extend battery runtime • High conversion efficiency • Integration TI Information: Selective Disclosure Battery Management • Chargers, gauges and protection for EVERY application • Battery life • Support for any battery chemistry • State-of-health Power Supply Control • AC/DC converters, power factor, protection, digital power controllers • Energy efficiency • Intelligent control Point-of-Load • DC/DC, voltage regulators, protection circuits • High-voltage POL • System protection • Low noise Power density: PowerStack™ Reduction of package parasitics RPCB Input Supply • • • LDRAIN Stacked NexFET™ , ~ 2X greater power density CINPUT Driver HS FET CLIP Low resistance Cu clips, ~ 30% lower power loss Ability to optimize and deliver higher efficiency Control FET PWM HS FET X LS FET CLIP LSOURCE Switch Node • Simple PCB layout for optimized performance LO IL LDRAIN IC LS FET Driver Sync FET X Improved thermal management and PCB layout Single grounded DAP CESL Package impact can be = to two generations on silicon X improvement! LSOURCE • CESR 15 CTOTAL CO Load Differentiating through technology • Telecom, industrial trends: – Higher current levels – Greater power density, efficiency • 25-A step-down converters with integrated NexFET™ – Highest power density, smallest package – Smallest total footprint – Highest efficiency (>90%) – Ease of use – Qualified in multiple fabs and assembly/test sites • Differentiated by: – Process technology – Packaging innovation TI Information: Selective Disclosure High Side Clip High Side NexFET Low Side NexFET DC/DC Controller Lead Frame Low Side Clip Summary • Advancements in packaging deliver differentiation, and a broad range of solutions are required • Materials and assembly processes are interlinked and play a major role in addressing next-gen challenges • 3D integration in Power Packaging is a critical element to creating a strong value proposition TI Information: Selective Disclosure