Lecture 21

advertisement

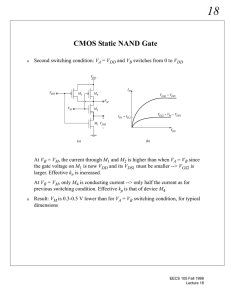

Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Lecture 21 LECT 20 Review Switching Speed of CMOS Inverter Approximate method versus exact calculation Static CMOS Logic Circuits Static Zero-Power CMOS Logic NOR, NAND CMOS Logic Device Sizing – NAND preference Complex Logic Circuits in Static CMOS Style 1 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Inverter Gate Delay - Input Low to High VDD vout1 = v in2 vin1 vout2 + - Stage(N) Stage(N+1) Delay The input Vin1 goes from low to high and Vout1 goes from high to low. The fall of Vout1 is delayed by an RC charging time. We need to identify all the contributions to the capacitance and the effective resistance Rn which charges the capacitance. 2 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Inverter Gate Delay - Input Low to High VDD vout1 = v in2 vin1 vout2 + - Stage(N) Stage(N+1) Delay Each transistor has two important capacitances: Gate to substrate and Drain to substrate. Thus each inverter has four capacitances. We will ignore for the moment all other capacitances (like wiring). (And much of the time we ignore the drain capacitances.) Lets briefly look at a cross-section to identify the capacitances. 3 Lecture 21 EECS 40 Spring2002 B Copyright Regents University of California CMOS LAYOUT A We can find the gates in cross-section B-B, but the PMOS gate is easier to see in A-A A We can find the drain space charge capacitances in B-B (where we have white color to emphasize space-charge) B A-A B-B CDp CGp CDn 4 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Stage N Gate Delay - Input Low to High VDD CDp vin1 + - Rn CGp vout1 v in2 vout2 CDn CGn Stage(N) Stage(N+1) Delay Load Stage (N) with Stage (N+1) Identify capacitive loads for output of stage N: 1) Drain capacitance CDn+CDp of stage N. When input goes high: 2) CGn+CGp of stage N+1. 1) PMOS turns off 2) NMOS turns on (replace by resistor Rn) The time delay in decay of Vout1 is causes by RC delay where R is Rn of the NMOS transistor of Stage N and C is the sum of 4 capacitances: CDn+CDp of stage N plus CGn+CGp of stage N+1 5 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Finding the effective resistance to use in RC delay analysis We replace the active transistor with an effective resistance Reff where Reff is chosen to correctly estimate the current charging the capacitive load. Clearly if the current is ID and the voltage is VDS then the effective resistance is VDS / ID at any point on the curve. Example: VDS = VDD , effective R is VDD /[IDS (1+λVDD )] (the blue line). But in the charging interval in which the VDS moves between VDD and VDD/2, the average VDS is 0.75VDS ; therefore we approximate the effective resistance as: ID ID = IDS (1+λ VDS ) at VGS = VDD Average R is 0.75VDD /(IDS (1+0.75λVDD ) And we have a formula for IDS: IDS = KVS(W/L) (VGS - VT ) IDS Example: 0.25µm technology: KVS = 75µA/V, VDD = 2.5V. Suppose VT = 0.5V, W/L =1/.25, Then IDS = 4X(2.5-.5)X75 =600µA. Rn = .75 X 2.5/[600 X 10-6 X (1+ .125 X .75)] = 2.86 KΩ VDD/2 VDD VDS 6 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Finding the Gate delay for a simple inverter cascade. We have found that the effective output resistance Rn of the (W/L = 1/.25) NMOS device MN1 to be 2.86KΩ We make the PMOS device MP3 twice as wide as the NMOS to get an equal value of Rp. (Remember IDS for PMOS is only half as large as NMOS for equal size and bias.) The input capacitance of the (identical) next stage (being driven by this 2.86KΩ resistor) is approximately CGp + CGn (In this example we ignore drain capacitors for simplicity). VDD MP3 vout1 = vin2 MN1 For a 5nm oxide thickness , Cox = 3.9 X 8.85 X 10-14 /5X 10-7 F/cm2 or 6.9 fF/µm2. NMOS: CGn = W x L x Cox =1.7 fF. PMOS : CGp = W x L x Cox =3.4 fF. Thus C= 5.2 fF The gate delay is 0.69RC or 10pS. Note that 0.69RC = 0.69 X 0.75 CVDD /(IDS (1+0.75λVDD ) 7 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Comparison of Exact Gate Delay with “Effective Resistor” Approximation We can actually compute the precise gate delay for this MOS model by solving the differential equation. (Note that we do this for proof only -the material on these two pages is for your curiosity only ) ID G ID ID = IDS (1+λ VDS ) IC D MN1 C = CGp + CGn Note at t=0, VD = VDD IC =C dv/dt =C dVD /dt But IC = - ID = - IDS (1+λ VD ) so dt = -C d VD /[IDS (1+λ VD )] IDS VDD/2 VDD VDS which we integrate from t =0 to ∆t and VD = VDD to VDD /2. 8 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Finding Exact Gate Delay dt = -C d VD /[IDS (1+λ VD )] which we integrate from t =0 to ∆t and VD = VDD to VDD /2. Special case λ = 0 Then ∆t = C VDD /2 IDS (versus 0.69 x 0.75 x C VDD / IDS = 0.52 x C VDD / IDS ) - about a 4% error using the simple RC approximation General case: Let U = (1+λ VD )] then the equation is dt = -C d U /[IDS λ U ] which we integrate from t =0 to ∆t and U = 1+λ VDD to 1+0.5λVDD SOLUTION: ∆t = -(C/λ IDS )[ ln(1+0.5λVDD )-ln(1+λVDD )] Example: VDD=5V, λ=.05 = (C/λ IDS ) ln[ (1+λVDD )/ (1+0.5λVDD )] 0.457 CVDD /IDS Versus the solution with the resistor approximation: 0.69RC = 0.69 X 0.75 CVDD /(IDS (1+0.75λVDD ) 0.473 CVDD /IDS less than 3% error. 9 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California CMOS DIGITAL LOGIC VDD NAND gate C= A B A B AB 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 Making a NAND gate: A B C A B NMOS portion: both inputs need to be high for output to be low Æ series PMOS portion: either input can be low for output to be high Æ parallel 10 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California CMOS NAND GATE NMOS switches in series from output to ground; PMOS switches in parallel from output to the supply VDD VDD vA vA vB vOUT vOUT vA vB OR vB 11 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California CMOS NOR GATE NOR function (two inputs) A B A +B C=A +B 0 0 0 1 0 1 1 0 1 0 1 0 1 1 1 0 VDD A B C Output is high only if both inputs are low Æ A B PMOS switches (between the supply and the output) in series Output is low if either input is high Æ NMOS switches (between ground and the output) in parallel 12 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California CMOS NOR GATE “Complementary” configuration to the NAND gate NOR NAND VDD vA VDD vA vOUT v OUT vB vB 13 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California NOR Gate Pull-Down Transient Model* VDD vA Depends on values of A and B inputs: If only A or B is high, one resistor of value Rn pulls the node down to ground. v OUT vOUT Rn Rn load vB This is the relevant part of the NOR gate in pull-down load But If both A and B are high, then two NMOS resistances are in parallel 14 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California NOR Gate Pull-Down Transient Model* Depends on values of A and B inputs: If only A or B is high, one resistor of value Rn pulls the node down to ground. This is the “worst” case and therefore should be used in timing calculations. This is the relevant part of the NOR gate in pull-down t=0 D Rn Rn CGp + vout1 - VDD CGn Worst case: RC = Rn (CGp + CGn ) This is the load on the NOR gate -- for simplicity we assume a simple inverter. * For first-order analysis we consider only gate capacitance. Remember: we must add drain and interconnect for accurate estimates. 15 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California NOR Gate Pull-UP Transient Model* VDD PMOS switches are in series Æ resistors are in series Rp Pull-up - both inputs switch low together τ = (Rp + Rp) (CGn + CGp) Pull-up vs. τ = Rn (CGn + CGp) Rp iC Pull-down CGp U + Remember these formulas assume fan-out of 1 into t = 0 a simple inverter (with capacitance [CGn+CGp] ) and are still ignoring the drain capacitances. vout1 - VDD CGn If we want equal rise and fall times we need to size devices so that R p = 12 Rn Example: Suppose NMOS devices are twice as W powerful as PMOS at the same device size (i.e. KVS is twice as large for NMOS. Then we require: L ≈4 p W L n 16 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California NAND Gate Pull-Up Model (with simple single-inverter load) VDD vA v Rp B v OUT vB vA Rp ⇒ C = CGn + CGp C One or both switches closed (worse case: one switch) τ = RC = RpC = R p (CGn + CGp ) 17 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California NAND Gate Pull-Down Model* VDD vA v Rn B v OUT vB vA Rn C C = CGn + CGp ⇒ Two Rn’s add in series, so RC = 2RnC = 2Rn ( CGn + CGp ) vs. R p (C Gn + C Gp ) for pull-up If at same device size, NMOS is twice as powerful as PMOS then 2Rn =Rp with identical device sizes. Thus this circuit is “automatically” balanced for equal rise and fall times. * For first-order analysis we consider only gate capacitance. Remember: we must add drain and interconnect for accurate estimates. 18 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Effect of larger Fanout 1 2 n Fanout leads to increased capacitive load (and higher delay) Procedure: Add all input capacitances of the logic blocks (gate capacitances of all devices connected to the node whose transient is being studied). 19 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Effect of larger Fanout - Example L2 X 1 L3 L4 For this example node X is pulled up by Rp of NAND gate 1 and loaded by 2CGp+2CGn of L2, CGp + CGn of inverter 3 and CGp + CGn of inverter 4. Thus ignoring drain capacitances in stage 1 and interconnect capacitances, the worst-case pull up stage delay is 0.69 Rp (2CGp2+2CGn2 + CGp3 + CGn3 + CGp4 + CGn4 ). 20 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Drain Capacitances For our simple estimates we will simply add the drain capacitance of every drain connected to the node being studied. Example: 2-input NAND VDD vA vOUT In this example the vOUT node has two PMOS device drains and one NMOS device drain connected to it. We estimate the capacitance from the circuit layout by multiplying the drain area by the average capacitance per unit area. vB 21 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Larger Fanout – Example: Drain Cap’s L2 1 X L3 L4 In this example the Node X is loaded by the input capacitances: (2CGp1+2CGn1 + CGp2 + CGn2 + CGp3 + CGn3 ). But the drain capacitances of stage 1 also load the node: 2CDp + CDn .Therefore the stage delay is given by: τLH = 0.69 Rp (2CGp2+2CGn2 + CGp3 + CGn3 + CGp4 + CGn4 + 2CDp + CDn ). τHL = 0.69 x2Rn (2CGp2+2CGn2 + CGp3 + CGn3 + CGp4 + CGn4 + 2CDp + CDn ). 22 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California More Complex Static CMOS Logic Functions VDD vC What is this logic function? vA vOUT How to ratio the devices so that the worst case rise and fall delays are equal? Under these conditions what is the effective resistance driving the output up or down? What are input capacitances of the three nodes? vB What are the drain capacitances loading the output? (See Prob. Set 12) 23 Lecture 21 EECS 40 Spring2002 Copyright Regents University of California Interconnect Capacitances Interconnect = thin-film “wire” connecting gates; typically aluminum Significant source of capacitance (and resistance if the line is long) May be 1cm long! We estimate the capacitance simply by multipying area of wire (length times width) times the dielectric constant of the insulator divided by the insulator thickness. Example ½ µm wide Al wire 10µm long on 1µm thick oxide. 1/2 ×10-4 ×10 ×10-4 × 3.9 × 8.85 ×10-14 C= = 0.17fF -4 10 24