CMOS VCO`s For PLL Frequency Synthesis In GHz Digital Mobile

advertisement

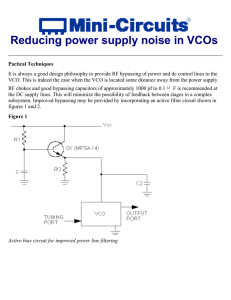

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 1511 CMOS VCO’s for PLL Frequency Synthesis in GHz Digital Mobile Radio Communications Manop Thamsirianunt and Tadeusz A. Kwasniewski, Member, IEEE Abstract— CMOS inductorless voltage controlled oscillator (VCO) design is discussed with the emphasis on low-noise, low-power, gigahertz-range circuits suitable for portable wireless equipment. The paper considers three VCO structures—one simple ring oscillator and two differential circuits. The design methodology followed optimization for high-speed and low-power consumption. The proposed linearized MOSFET model allows the accurate prediction of the operating frequency while the phase noise evaluation technique makes it possible to determine, through simulation, the relative phase-noise performance of different oscillator architectures. The measurement results of three VCO’s implemented in 1.2-m CMOS technology confirm with the simulation predictions. The prototype VCO’s exhibits 926-MHz operation with 083 dBc/Hz phase noise (@ 100 kHz carrier offset) and 5 mW (5 V) power consumption. Index Terms—CMOS oscillator, ECO, emitter coupled oscillator, linearized MOSFET model, multivibrator, phase locked loop, phase noise simulation, PLL frequency synthesizer, relaxation oscillator, ring oscillator, VCO, voltage controlled oscillator. I. INTRODUCTION T HE rapid growth in the use of digital mobile communicators and wireless portable telephones (digital wireless) has been met through steady reductions in cost, size, and power consumption. For the terminal manufacturers to remain competitive, terminal design remains a very challenging task driven by consumer-market demands. The key technology issues to be addressed relate to minimum complexity architecture, low power, and maximum use of very large scale integration (VLSI). Currently, the implementation of digital wireless components is of a strong research interest. Both CMOS and BiCMOS implementation paths are considered. Many of the recently reported implementations of frequency synthesizers use a mixture of high-speed semiconductor technologies, as shown in Fig. 1. To date, the voltage-controlled oscillator (VCO) and the dual-modulus prescaler are implemented in either bipolar or GaAs MESFET technologies, while most of the low-frequency digital circuits are implemented in CMOS technology. Although several CMOS frequency dividers have been recently reported which exhibit operating frequencies to a few gigahertz [1]–[3], there has been no report to date on the use of on-chip GHz-range CMOS VCO’s in wireless applications. Such conflicting mix of high and low frequency technologies inhibits the realization of a complete circuit integration and raises the component cost. Manuscript received June 21, 1994; revised April 28, 1997. M. Thamsirianunt is with Exar Corporation, Fremont, CA 94538 USA. T. A. Kwasniewski is with the Department of Electronics, Carleton University, Ottawa, ON, K1S 5B6, Canada. Publisher Item Identifier S 0018-9200(97)06317-8. The availability of the submicron MOS process has resulted in speeds of MOS phase-locked loops (PLL’s) that have significantly increased compared with PLL’s of the past. Recent papers indicate the potential for NMOS oscillators that operate to GHz frequencies [4], [5]. The challenge then is to develop CMOS analog-type circuits for high frequency applications. It is the objective of this work to demonstrate that a gigahertz frequency range and milliwatt power consumption of a monolithic CMOS VCO with good phase noise performance can be achieved. Several novel high-frequency CMOS VCO architectures are presented which have good potential to meet the demand for low-cost fully integrated RF circuitry. When used as components in PLL frequency synthesizers, these CMOS VCO’s offer phase noise performance comparable to known bipolar on-chip VCO designs [6]–[8]. A preliminary ac MOS model for CMOS VCO was developed together with the phase noise simulation technique for characterization of the proposed VCO’s. The techniques have shown high correlation between the simulation and the phase noise measurement of the prototype VCO’s. Both techniques allow more accurate VCO performance prediction and architecture comparison. In comparison to other silicon bipolar on-chip VCO designs in the past, the three implemented CMOS VCO architectures are based on the operation of circuit parasitic capacitors. With layout techniques, one of the VCO’s delivers phase noise level better than 83 dBc/Hz at 100-kHz carrier offset. The VCO designed with a fully differential architecture has phase noise better than 114 dBc/Hz at 1-MHz offset from the carrier, demonstrating performance comparable to those achieved with LC on-chip Si bipolar designs [6]. Section II reviews important performance parameters of VCO’s and their architecture comparison and describes an analysis of timing jitter or phase noise of a parasitic-only CMOS oscillator. Section III illustrates the three proposed VCO architectures and their design techniques. The ac MOSFET model for use in CMOS VCO’s circuit simulation is presented in Section IV with an evaluation of the proposed model accuracy and phase noise simulation techniques. Finally, the experimental results and summary are presented in Sections V and VI, respectively. II. DESIGN OF MONOLITHIC VCO’S A. Key Parameters General requirements for a high-quality VCO include high spectral purity, linear voltage-to-frequency transfer character- 0018–9200/97$10.00 1997 IEEE Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1512 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 Fig. 1. Typical building blocks for a modern RF PLL frequency synthesizer. istic, and good frequency stability to power supply and temperature variation. However, for digital wireless, the VCO must also have very low power consumption and low fabrication cost as well. While high linearity and wide tuning range may be necessary in some applications, in wireless communications where bandwidths are limited to a few tens of megahertz, tuning range and linearity do not present a problem. Longterm frequency stability as a function of temperature is less problematic if the rate of change of frequency drift is within the PLL bandwidth. The feedback action of the PLL suppresses the frequency error with a magnitude that is a direct function of the open loop gain. In effect, the significant VCO properties that must be considered are spectral purity, high operating frequencies while maintaining low power consumption, and suitability for circuit integration. V B. High-Speed, Low-Noise VCO’s A monolithic oscillator can be realized using i) a tuned oscillator whose frequency is determined by reactive elements, or ii) a relaxation oscillator, also called a multivibrator, which operates by alternately charging and discharging an energy storage element (usually a capacitor) between two initially set threshold voltage levels. Most low phase-noise oscillators often employ LC tank or resonant elements off chip due to the difficulty in controlling process variations which can lead to long-term frequency drift. Although current research has shown possibilities of implementing on-chip LC VCO’s, the achievable values remain low (about five) [6]. Moreover, the inductors built on silicon occupy a substantially larger area compared to other on-chip VCO designs. In contrast to LC VCO’s, a relaxation oscillators can be an emitter coupled oscillator (ECO) as shown in Fig. 2(a), or a simple ring oscillator in Fig. 2(b). Since relaxation VCO’s do not require any external components for oscillation, they are now becoming preferable in most high-frequency fully integrated PLL circuits. However, due to the absence of high passive component(s) in relaxation VCO’s, their free running spectral purity is inferior. The relaxation VCO architectures must have some forms of compensation, or use some special techniques, to accommodate the wide tuning range [7]. (a) (b) Fig. 2. Multivibrator oscillators: (a) emitter coupled multivibrator and (b) ring oscillator. C. Comparison of Bipolar ECO’s and MOS Relaxation Oscillators So far, the emitter coupled multivibrator shown Fig. 2(a) is the favored structure for high-speed PLL circuits. It is known to have good temperature stability and operates at high frequencies. Several papers including the ones by Sneep and Verhoeven [7], Abidi and Meyer [11], and Martin [12] have shown phase noise analyzes of relaxation oscillators based Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. THAMSIRIANUNT AND KWASNIEWSKI: CMOS VCO’S FOR PLL FREQUENCY SYNTHESIS 1513 (a) (b) (c) Fig. 3. Ring oscillator based on MOS inverter ring structure. (a) Ring oscillator and RC basic relaxation oscillator configuration, (b) generalized circuit for noise analysis, and (c) CMOS inverter with its parasitic and equivalent circuit for an integrator. upon ECO structures. These papers suggested techniques to improve the phase noise performance. However, their analyzes pointed out one common inherent drawback of the ECO’s—the phase noise is inversely proportional to the tail current that is used to charge and discharge the timing capacitor [see , where is the equivalent Fig. 2(a)]. The product of thermal noise resistance of the current source , indicates the power consumption of the oscillator. In order to achieve a good phase noise performance, a certain minimum power consumption in the current sources is unavoidable. Consequently, the lower phase noise ECO’s are only achieved by maintaining high current levels which are undesirable in our design goal. As a result, a relaxation ring oscillator based on the construction of all MOS devices as opposed to an ECO structure will be analyzed. The oscillation mechanism of a ring oscillator can be modeled as a basic RC relaxation oscillator, as illustrated in Fig. 3(a) [9]. Each inverter in this ring can be modeled as a Schmitt trigger and its associated timing , and , that form the oscillator. Inverter components , and that ring oscillators consist of timing elements can be circuit parasitics, and therefore result in a frequency of oscillation that can be maximized in a given technology. Although we appreciate the complexity of other VCO’s phase noise predictions (such work has been reported by others), we would like to present a simplified analysis which, in our opinion, helps us gain an insight into the phase noise/circuit parameters dependency. We begin by replacing the inverter cell with a voltage comparator as modeled by a Schmitt trigger as shown in Fig. 3(b). We postulate that at frequencies considered, each inverter cell in fact is a transconductance amplifier with its own circuit parasitics. From Fig. 3(b), the period of the oscillation is (1) At the threshold crossing point, the capacitor-charging current, , can be expressed as The random fluctuation of , where is the threshold voltage of or the inverter, induces corresponding fluctuations in (2) Assuming all inverter stages are identical and operate in the are functions of the device’s saturation region, both and Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1514 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 (a) (a) (b) Fig. 5. VCO2 modified D-latch ring oscillator. (a) Proposed new D-latch for VCO2 and (b) VCO2 pseudo-three-stage ring oscillator. obtains (5) Equation (4) can now be rewritten as (b) Fig. 4. VCO1 simplified three-stage modified ring oscillator. (a) VCO1 three-stage ring oscillator and (b) short-channel effect in the MOSFET saturation mode. can be represented by and or where are all constant coefficients, thus the phase noise in terms of fluctuations in time , as a function of threshold voltage variation, may be rewritten as (6) Because the oscillating frequency is proportional to the frequency of each inverter, i.e., , therefore geometries, (3) or (4) From (3) it can be seen that the timing jitter dependence on threshold variation decreases with both device’s length ( ) and device’s width ( ). Although the assumption was made that does not depend on , the above analysis can give some insights into the power supply and substrate noise coupling effects. Let us now consider the dependence on . One (7) to The phase noise is defined as a ratio of ), therefore it can be shown that for a maximumspeed VCO scaling process, where ratios remain constant, the phase noise sensitivity actually does not depend on . The rms voltage amplitudes of the input referred noise in CMOS devices (in saturation mode) also depend on device sizes. The thermal noise is proportional to while or flicker noise is proportional to . Scaling the and maintaining constant) of down (by decreasing a design does not change the phase noise contributed by the MOS device thermal noise. On the other hand, for a given MOS technology, the designs that operate at frequencies lower than the maximum, however, the phase noise due to the thermal noise will be smaller (also true when power and ratio increase). The flicker noise contribution might, Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. THAMSIRIANUNT AND KWASNIEWSKI: CMOS VCO’S FOR PLL FREQUENCY SYNTHESIS (a) 1515 (b) (c) Fig. 6. VCO3 (a) fully differential oscillator using double flip-flops, (b) the implemented circuit, and (c) redrawn with differential ring structure and regenerative circuits. (a) (b) Fig. 7. HSPICE equivalent circuit MOSFET. (a) Transient analysis and (b) ac analysis. however, increase unless the gate capacitance value is kept constant or larger. The same feature size CMOS processes noise because of their can experience differences in the process variations. This factor could play a more important noise contribution than the effect of role in evaluating the ], hence the actual flicker noise amplitude gate area [ could become a dominant factor in determining the VCO phase noise performance. Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1516 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 Fig. 8. A proposed linear ac model for MOS devices in oscillator circuits. (a) (b) Fig. 9. (a) Basic block diagram for representation of VCO in frequency domain, and (b) model of an injected noise current for actual analysis in oscillator circuit (Vn noise input voltage). (a) = The analysis above indicates a potential advantage of MOS relaxation oscillators over classical bipolar multivibrators, especially for a MOS relaxation oscillator structure that employs circuit parasitics. Parasitic MOS oscillator structures allow greater circuit integration and lower power consumption. However, the maximum oscillation frequency is related to device speed and device sizing, and therefore parasitic-only MOS oscillators have to be optimized for speed through architecture and layout techniques. D. of CMOS Relaxation Oscillators The multivibrator has only one energy storage element, i.e., a capacitor which by its nature results in a low- oscillator. In comparison to LC VCO’s, the equivalent of a multivibrator is 1/4 [13]. One of the primary design goals in the CMOS VCO design was to obtain a high factor without the use of LC tank circuits. The use of inverter integrators in a ring oscillator can provide higher equivalent than for a regular single stage relaxation oscillator. Section IV presents an approach which, by replacing the nonlinear delay stages with a linear models, allows prediction of the oscillating frequency of a CMOS VCO. (b) Fig. 10. Circuit used and frequency response for VCO1 (Input amplitude 10 A). In = III. HIGH-SPEED, LOW-POWER CMOS OSCILLATOR DESIGN A number of circuit techniques have been recently reported to improve the frequency stability and linearity of inductorless CMOS oscillators. For example, a VCO with improved linearity and jitter improvement was reported by Wakayama Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. THAMSIRIANUNT AND KWASNIEWSKI: CMOS VCO’S FOR PLL FREQUENCY SYNTHESIS Fig. 11. Fig. 12. VCO1 frequency response of the altered inverter 1 device sizes (Input amplitude In Simplified simulation setup for phase noise prediction technique. [14], while a CMOS VCO with temperature compensation was reported by Flynn [15]. These techniques demonstrate that CMOS oscillators are good prospects for achieving performance comparable to Si bipolar oscillators. Although the use of external circuits has been shown to result in improved oscillator characteristics, it has been at the expense of increased power consumption and decreased operating speed. Therefore, the speed of the CMOS oscillator has been to date the limiting factor that restricts its use to only low-tomid-frequency applications. The development of techniques to improve speed while maintaining low power is therefore the major challenge in a CMOS oscillator design. A. Design Guidelines Placing the highest priority on speed implies that the CMOS oscillator must be constructed using the simplest structures, such as an odd-number inverter ring oscillator based upon an RC relaxation oscillator, as described in Section II. To 1517 = 10 A). obtain high speed performance and low power the VCO design methodology follows the guidelines below. • Minimize all parasitics by using the circuits with minimum complexity. • Choose those architectures which enable circuits to operate at maximum speed. • Utilize unavoidable parasitics; no external reactive elements. To improve noise performance, the following techniques are also incorporated. • Employ a switching waveform with sharpest rising and falling edge [11]. • Balance timing of the waveform for a 50% duty cycle [16]. • Minimize the number of stages for the ring oscillator [12]. • Use a symmetrical layout design [4]. B. Proposed VCO Circuits 1) VCO1—Modified Ring Oscillator: The oscillator of Fig. 4(a) shows a simplified version of the proposed threestage ring oscillator employing a single-inverter delay cell. The frequency control is achieved by directly controlling the current through a series transistor of one inverter stage. The two remaining inverters are connected to form a closed-loop ring. The circuit contains the least number of components required for a functional relaxation oscillator. The unique frequency control mechanism of the oscillator exploits short-channel effect of the controlling transistor to control the overall circuit delay. This scheme adopts a gradual monotonic increase in the current of transistor around Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1518 Fig. 13. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 Simulated VCO spectra demonstrating phase noise correlations. the saturation region for a linear voltage to frequency control. Most mobile radio frequency bands are limited to a few tens of megahertz, therefore the operation of the VCO along the boundary of the saturated delay cell can be utilized. 2) VCO2—Modified D-Latch Ring Oscillator: Using the self-oscillating behavior of the D-latch circuit in [2] [see Fig. 5(a)], it is possible to realize a high-frequency oscillator. The arrangement needed to construct this type of oscillator is shown in Fig. 5(b), where a cross-coupled D-latch is combined with two loop inverter rings. and are used in this configuration to replace two complete inverters resulting in a pseudo-three-stage differential ring oscillator structure. Because the D-latch is a sequential input [shown in the schematic of circuit, when the ] is held high (logic 1) state transition occurs, Fig. 5(b) as enabling the rings to start oscillation. The dc level of should be held higher than the CMOS threshold level ( ) is inversely in order to start the oscillation. The dc level of and , hence proportional to the channel resistance of the transition time in the latch or frequency of oscillation can . be changed by varying the 3) VCO3—Fully Differential Ring Oscillator: As indicated in Section II, the standard emitter-coupled multivibrator design has conflicting design rules which dictate that the oscilla- tor consume high power in order to reduce phase noise. However, this standard approach has been modified to accommodate MOS implementations [4]. NMOS versions of this emitter-coupled-like oscillator, fabricated in a 0.75- m-NMOS process, show the use of grounded parasitic timing capacitors. A wide tuning range and maximum oscillating frequency of 1 GHz was achieved. A CMOS version of this architecture was explored and suggested but no details relating to the analysis nor implementation were given. Fig. 6 shows our proposed structure for a CMOS implementation. The oscillator was constructed using a constant currentcharge-discharge scheme. The latching operation which alternates the state of two current controlled inverters was achieved by the use of NOR double flip-flops. To understand the operation of the architecture, NOR flip-flops are broken down to a simple inverter level by viewing the structure as a two-loop differential ring oscillator, as shown in Fig. 6(b). It is clear that the rings are formed by common three-stage ring oscillators. To appreciate the presence of the differential ring configuration in the VCO, Fig. 6(b) has been redrawn to Fig. 6(c). The fully differential inverter rings were formed using two crosscoupled five-stage ring oscillators via regenerative inverter latches. Regenerative circuits are known for their potential for Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. THAMSIRIANUNT AND KWASNIEWSKI: CMOS VCO’S FOR PLL FREQUENCY SYNTHESIS 1519 speed improvement. In this aspect it also reduces the switching inconsistency of the ramp waveform across the parasitic timing capacitors in a relaxation oscillator. Although this VCO design is based on a proposed architecture found in the literature [4], significant optimization effort was required to achieve the desired low noise and maximum oscillating frequency. A simplified schematic of the complete VCO is shown in Fig. 6(b). C. VCO Implementation and Circuit/Layout Optimization This section describes the implementation issues of the proposed VCO’s presented in the previous section. The VCO circuits were optimized in both schematic and layout level prior to fabrication. Simulations and optimizations of the preliminary design for all three VCO’s were carried out at the schematic level using transient analysis to find the maximum possible oscillating frequency. Simulations showed that optimized circuits and device sizing had to be made through an iterative process due to the dynamic interaction between the loop ring component. The circuits were laid out using a 1.2- m double-poly double-metal N-well CMOS technology. The layout was custom designed and reoptimized to achieve symmetrical waveform and the largest swings throughout the circuits. The layout of VCO1, VCO2, and VCO3 circuits including buffer circuits have active areas of 84 m 50 m, 142 m 58 m, and 127 m 76 m, respectively. IV. FREQUENCY DOMAIN ANALYSIS OF A CMOS VCO USING THE DEVELOPED MOS MODEL AND PHASE NOISE SIMULATION A. Proposed MOS Model for AC Analysis The traditional approach to the design of relaxation-based oscillators depends solely on the time domain analysis. Section II refers to some of the existing analytical methods. The CMOS GHz-range oscillator design issue should, however, address the fact that speeds at which the circuits operate result in a switching behavior far from what is called a digital switching. Specifically, one observes continuously changing node voltages. The high/low states, if reached, occur for only a short period of time. In fact, the waveforms closely resemble sinusoidal shapes. Considering also the fact that the class of circuits of interest, namely ring oscillators, exhibits the positive feedback, it is more accurate and meaningful if the analysis is linearized and performed in the frequency domain. The problem can be classified as a large signal frequency domain analysis. Consider the SPICE ac model of the MOSFET transistor shown in Fig. 7(b) [17]. The model components depend on the transistor biasing point. This model, when used for ac analysis, requires a fixed biasing voltage and does not hold for large signal analysis. Following the approach used in the nonlinear circuit analysis [18] and microwave circuit analysis [19], we investigated the possibility of replacing the full nonlinear model by a simplified linear model of Fig. 8. The model linearization was obtained by taking average values of MOSFET parameters with reasonable assumptions for the operating point of MOS transistors. Since is a Fig. 14. VCO voltage-to-frequency transfer characteristic curves. parameter that is a function of biasing voltage, maximum results at equal to 5 V for NMOS and 5 V for PMOS (assuming the full swing of the CMOS inverter). The model was linearized by removing the diodes, as shown in Fig. 7(a). An acceptable approximation was achieved through several Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1520 Fig. 15. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 Spectra traces of VCO’s outputs at 1 kHz resolution bandwidth and the waveforms. simulation trials by setting the operating point for ac analysis at midpoint, i.e., equal to 2.5 and 2.5 V for NMOS and PMOS transistors, respectively. At these voltages, it is certain that both transistors are fully on, resulting in approximated linear values for elements , and . Some of the elements shown in Fig. 8 are bias dependent, and are a function of the device operating while state (on, switching, off). The worst case linearized value [20] which leads to a conservative result (high side capacitance) . estimates Fig. 9(a) shows a linearized feedback system with the ) transfer disturbance ( ) to the input ( ). The output ( function can be expressed by (8) The stability analysis can be performed with frequency domain simulation for which we propose to use the model shown in Fig. 9(b). The capacitor is the actual circuit capacitance at an arbitrarily selected node of the oscillator. is the sum of a voltage developed Note that the voltage by injecting the current and the voltage present on on in absence of . It is of interest to note that the transfer function results in the node output impedance—a parameter used in the microwave circuit analysis. B. Validation of the Proposed AC MOS Model Through Simulation To establish the validity of the proposed model, ac SPICE as input and simulation was conducted using injected noise the node voltage as output . The VCO1 circuit was used as an experimental prototype for developing the linearized ac model parameters. The model development procedure can be described as follows. After the fixed bias parameters of each MOS device were obtained from the SPICE transient analysis output ( , and ), they were recalculated and used in the linearized ac MOS model. The linearized MOS models are then encapsulated in subcircuits and used to replace all existing MOS transistors. The ac analysis simulation results (Fig. 10) with the developed linearized MOS model indicated a peak frequency of 760.32 MHz as compared with 759.90 MHz that was obtained by the transient analysis (SPICE Model). To verify the accuracy of the developed model, different device sizes were simulated. The inverter 1 layout of the VCO1 circuit was changed, with both the n and p MOS six times larger than those of the original circuit. The extracted layout simulation was then performed, and the transient analysis indicated an oscillating frequency of 673.40 MHz or 88.61% of the original circuit. New device parameters extracted from SPICE were then used to replace the ac MOS model parameters for ac simulation. The ac response of the oscillator produced a peak frequency of 701.45 MHz or 92.20% of original circuit, as illustrated in Fig. 11. The VCO2 and VCO3 were also verified with the linearized model. The simulated oscillating frequency results in ac analysis were also in close agreement with those of their transient analyzes. The results indicate that the proposed linearized model can indeed be used to predict the oscillating frequency. Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. THAMSIRIANUNT AND KWASNIEWSKI: CMOS VCO’S FOR PLL FREQUENCY SYNTHESIS (a) 1521 noise source used here was 100-mV sinusoidal signal at 1-MHz offset from the oscillator’s center frequency. The SPICE transient analysis output was processed to obtain the corresponding power spectrum. In order to obtain comparable results, each VCO was simulated under the same conditions. These include the oscillating frequency, sampling frequency, simulation step size, and number of points in the power spectrum density (PSD) analysis. However, since VCO3 has a maximum oscillating frequency of 520 MHz, a less extreme oscillating frequency for VCO3 of 500 MHz was chosen instead. Fig. 13 shows the resulting PSD’s for the three oscillators. It is worth noting that the PSD’s do not indicate the absolute phase noise figures due to the nonlinear behavior of the CMOS oscillator which extricates the analysis of absolute system noise gain. The topic of phase noise modeling in a CMOS ring oscillator is of our great research interest. Even some commercially available phase noise simulation programs to date still require calibration against the actual measurement. Therefore, the proposed simulation is intended only to compare and correlate the phase noise results among the implemented VCO’s. The top plots are the PSD’s of the VCO’s in free running condition. The bottom plots show the PSD’s after the noise was superimposed on the power supply. It can be interpreted from the power spectra that each VCO has a different degree of sensitivity to power supply noise. The VCO1 spectrum shows the widest area of modulation around its center frequency, while VCO2 exhibits less susceptibility to noise. Finally, VCO3 demonstrates the best noise rejection among the three VCO’s. V. EXPERIMENTAL RESULTS AND DISCUSSIONS A. VCO’s Performance (b) Fig. 16. (a) Power dissipation as a function of oscillating frequency and (b) frequency of oscillation as a function of supply voltage. C. Phase Noise Simulation A phase noise analysis of an oscillator can be achieved by adapting the method outlined by Sneep and Verhoeven [7]. Although this method gives fairly accurate phase noise predictions for the oscillator circuits that use a physical timing capacitor, it is expected that parasitic capacitors present in the high-speed VCO designs would complicate the theoretical analyzes. As a result, the conventional phase noise analysis and noise source modeling for the types of our proposed VCO’s may not be the most pragmatic method for prediction. The simplicity of the phase noise simulation technique proposed here comes from the fact that a spectrally pure VCO (high- oscillator) will reject noise regardless of its origin [21]. As a result, we can verify the phase noise of an oscillator by determining the noise rejection ratio from the oscillator output power spectrum. Fig. 12 shows the simplified simulation setup for the technique proposed. The modulated The VCO tuning range, power consumption, phase noise response, and the effect of power supply variation were measured and compared with simulation results. The plots of the voltage-frequency transfer characteristics (or VCO tuning range) of the three VCO’s are shown in Fig. 14. For comparison, the simulation results for each VCO are also included (dotted line). The VCO1, VCO2, and VCO3 minimum–maximum oscillating frequency measured at 320–926, 225–600, and 100–500 MHz, respectively. The VCO spectrum outputs and waveforms are shown in Fig. 15. Fig. 16(a) shows the VCO’s power consumption. The top and middle curves, the power consumed by VCO3 and VCO2, show that the dissipated power is a linear function of frequency. VCO2 and VCO3 dissipate a maximum power of 14 and 20.2 mW, respectively. Test results of VCO1 showed that the fabricated chip delivered 16% higher speed than the results obtained from simulation. The VCO1’s maximum power dissipation measured at 9.4 mW. However, if the power dissipated by pad capacitance and buffer (3.92 mW, at 820 MHz) are excluded, then the core circuit would consume only 5 mW of power. It should be noted that the devices do not drive 50- impedance because the design intent is to fully integrate the VCO into a PLL system in contrast to a discrete device implementation which mandates all 50- interfaces. Electro- Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1522 Fig. 17. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 Measured VCO1, VCO2, VCO3 residue FM/SSB phase noise using HP3804A. magnetic interference (EMI) and radiation are also minimized because of shorter on-chip interconnects. The VCO’s were also measured for their oscillation frequencies as a function of supply voltage ( ) as shown in Fig. 16(b). Note here that the VCO1 has the highest sensitivity to power supply noise because the structure is single-ended. It is necessary to include on-chip supply decoupling capacitors. Measurement of phase noise was done by placing the oscillator in a PLL phase noise measurement system. All measurements were performed through bonded IC’s, packaged Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. THAMSIRIANUNT AND KWASNIEWSKI: CMOS VCO’S FOR PLL FREQUENCY SYNTHESIS Fig. 18. 1523 Test setup for verification of phase noise prediction technique. with a standard ceramic 68-pin PGA type. Although onchip buffer circuits were used to condition the output signal from the core circuits, a substantial level of attenuation of the oscillator output was unavoidable due to the effect of huge bonding pad capacitance and package parasitics. The oscillator’s output was amplified by a high-input-impedance amplifier before connecting to the 50- measurement system. VCO1, VCO2, and VCO3 phase noise were measured at their highest oscillating frequencies and plotted on the top, middle, and bottom charts of Fig. 17, respectively. The phase noise at 100 kHz offset from carrier frequencies shows that VCO1 had the highest noise levels at 83 dBc/Hz, followed by VCO2 at 87 dBc/Hz. VCO3 delivered the lowest phase noise response among the three, at 90 dBc/Hz. Note that the phase noise measurements obtained from the test setup were predicted to be worse than the actual values due to the additional amplifier and interconnections. B. Measurement of Spectral Purity in the Presence of Power Supply Noise Verification of the phase noise prediction technique in Section IV-C was performed using the configuration depicted in Fig. 18. The test bed consisted of the VCO circuit board, a bias tee circuit, and other necessary measuring equipment. The VCO’s source supply ( ) was ac modulated through the bias tee circuit, while the VCO tuning input was driven by a clean dc source. A voltage divider across the terminals of dry battery cells allowed adjustment of dc voltage. A single tone sinewave signal of 13 mV at 10 kHz, 100 kHz, and 1 MHz was added to the 5-V dc regulated supply for testing. Fig. 19 shows the output spectra of the three VCO circuits with 100-kHz signal modulation. The observed spectra exhibit unavoidable amplitude modulation effect, the side bands at 100 kHz offset from the center frequency because the VCO output buffer did not use a dedicated power supply. The noise rejection capability of the three circuits is not as pronounced as in the simulation (Section IIIB). The simulation results show that VCO3 had the highest noise rejection capability followed by VCO2 and VCO1. The measured results also follow the order of noise rejection capability. One should also consider that the measurement results include all the noise sources in the physical circuit. Their effect will mask the spread of the center frequency peak which is due to the added sinusoidal noise source. Fig. 19. Measured VCO spectral output before and after adding power supply noise. TABLE I MEASUREMENT RESULTS: SUMMARIZED PERFORMANCE FROM THE VCO DESIGN, * INCLUDING THE OUTPUT BUFFER CIRCUIT, PAD, AND PACKAGE CAPACITANCE ( 2.77 PF) Table I summarizes the measured performance parameters of the three VCO’s and the photomicrograph of the chip is shown in Fig. 20. VI. CONCLUSION Three high-speed CMOS VCO’s were presented which simultaneously achieve high operating frequency and good Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply. 1524 Fig. 20. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 10, OCTOBER 1997 Die photomicrograph. phase noise through the use of several innovative architectural and circuit design techniques. These circuits, through simulation and measurement, demonstrated performance and speed in a gigahertz range which to date has not been realized in a conventional CMOS process. The maximum oscillating frequency and phase noise results were superior to any previously reported CMOS VCO’s. As well, the power consumption was lower than that of any VCO’s previously reported in compatible technologies. The proposed VCO’s required no external components yet exhibited good phase noise performance comparable to LC on-chip oscillators facilitated using a high level of integration. The authors are currently working on the evaluation of a complete fractional-N synthesizer [23]. Such a synthesizer might exhibit power consumption below 10 mW, one gigahertz maximum operating frequency, and be suitable for use in the personal communication devices. ACKNOWLEDGMENT The authors are grateful for the assistance of Canadian Microelectronics Corporation (CMC) for fabrication support. Also, the support of the Canadian International Development Agency (CIDA), the Telecommunication Research Institute of Ontario (TRIO), and Micronet are gratefully acknowledged. The authors are indebted to the members of Carleton’s VLSI for Telecommunication Research Group, T. Kenny and Dr. M. Copeland for their support of this work, and M. Abou-Seido for his contribution to the AC model development. REFERENCES [1] H. I. Cong et al., “Multigigahertz CMOS dual-modulus prescaler IC,” IEEE J. Solid-State Circuits, vol. 23, pp. 1189–1194, Oct. 1988. [2] N. Foroudi, “CMOS high-speed dual-modulus frequency divider for RF frequency synthesizers,” M. Eng. thesis, Carleton University, Ottawa, Canada, 1991. [3] R. Rogenmoser et al., “1.16 GHz dual-modulus 1.2 m CMOS prescaler,” in IEEE Custom IC’s Conf., 1993, pp. 27.6.1–27.6.4. [4] M. Banu, “MOS oscillators with multi-decade tuning range and gigahertz maximum speed,” IEEE J. Solid-State Circuits, vol. 23, pp. 1386–1393, Dec. 1988. [5] S. Khursheed and A. Abidi, “NMOS IC’s for clock and data regeneration in gigabit-per-second optical-fiber receivers,” IEEE J. Solid-State Circuits, vol. 27, pp. 1763–1774, Dec. 1992. [6] N. M. Nguyen and R. G. Meyer, “A 1.8GHz monolithic LC voltagecontrolled oscillator,” in IEEE Int. Solid-State Circuits Conf., 1992, pp. 158–159. [7] J. G. Sneep and C. J. M. Verhoeven, “A new low-noise 100-MHz oscillator,” IEEE J. Solid-State Circuits, vol. 27, pp. 1097–1100, July 1992. [8] C. J. M. Verhoeven, “A high-frequency electronically tunable quadrature oscillator,” IEEE J. Solid-State Circuits, vol. 27, pp. 1097–1100, July, 1992. [9] A. B. Grebene, Bipolar and MOS Analog Integrated Circuit Design. New York: Wiley, 1984, ch. 11. [10] M. Soyuer and J. D. Warnock, “Multigigahertz voltage-controlled oscillators in advanced silicon bipolar technology,” IEEE J. Solid-State Circuits, vol. 27, pp. 668–670, Apr. 1992. [11] A. A. Abidi and R. G. Meyer, “Noise in relaxation oscillators,” IEEE J. Solid-State Circuits, vol. SC-18, pp. 794–802, Apr. 1983. [12] F. L. Martin, “A BiCMOS 50-MHz voltage-controlled oscillator with quadrature output,” in IEEE Custom IC’s Conf., 1993, pp. 27.4.1–27.4.4. [13] D. H. Wolaver, Phase-Locked Loop Circuit Design. Englewood Cliffs, NJ: Prentice-Hall, 1991. [14] M. H. Wakayama and A. A. Abidi, “A 30-MHz low-jitter high linearity CMOS voltage-controlled oscillator,” IEEE J. Solid-State Circuits, vol. SC-22, pp. 1074–1081, Dec. 1987. [15] M. P. Flynn and S. U. Lidholm, “A 1.2-m CMOS current-controlled oscillator,” IEEE J. Solid-State Circuits, vol. 27, pp. 982–987, July 1992. [16] I. A. Young et al., “A PLL clock generator with 5 to 110MHz of lock range for microprocessors,” IEEE J. Solid-State Circuits, vol. 27, pp. 1599–1606, Nov. 1992. [17] “Analysis and methods,” Hspice User’s Manual, Meta-Software, Inc., 1992, vol. 3. [18] W. R. Kolk and R. A. Lerman, Nonlinear System Dynamics. New York: Van Nostrand Reinhold, 1992. [19] G. D. Vendelin, Design of Amplifiers and Oscillators by the S-Parameter Method. New York: Wiley, 1982. [20] J. P. Uyemura, Circuit Design for CMOS VLSI. Norwell, MA: Kluwer, 1992, chs. 2, 3, 6, 7. [21] M. J. Underhill, “Fundamentals of oscillator performance,” IEE Electron. Commun. Eng. J., pp. 185–193, 1992. [22] “HP 3048A phase noise measurement system,” Hewlett-Packard User’s Manual, 1989. [23] M. Thamsirianunt and T. A. Kwasniewski, “A 1.2mm CMOS implementation a low-power 900-MHz mobile radio frequency synthesizer,” in. Proc. CICC, May 1994, pp. 16.2.1–16.2.4. Manop Thamsirianunt received the B.E. degree in electronics from King Mongkut’s Institute of Technology (KMITL), Thailand, in 1988 and the M.E. degree in electronics from Carleton University, Ottawa, Canada, in 1993. Since 1993, he has been working in the area of integrated circuit design for communications. His research interests include PLL’s, clock recovery, and low-power/high-speed analog circuit techniques. He is now with the Communications Department at EXAR Corporation, Fremont, CA, where he designs mixed-signal chips for network and transmission interfaces. Tadeusz A. Kwasniewski (M’86) obtained the Ph.D. and M.S. degrees from the Institute of Nuclear Research and Warsaw University of Technology, Poland, in 1974 and 1980, respectively. He worked as a Research and Development Engineer in the Warsaw Institute of Nuclear Research and VOEST Alpine in Austria. In 1983, he joined Lakehead University and in 1985, Carleton University, Ottawa, Canada. His research interests include CMOS radio circuits and signal processing architectures. Authorized licensed use limited to: Carleton University. Downloaded on October 28, 2008 at 13:12 from IEEE Xplore. Restrictions apply.