Solvers for Real-Time Simulation of Bipolar Thyristor - Opal-RT

advertisement

21, rue d’Artois, F-75008 PARIS

http : //www.cigre.org

Type here your Paper number

RECIFE 2011

(To be centred)

Solvers for Real-Time Simulation of Bipolar Thyristor-Based HVDC

and 180-cell HVDC Modular Multilevel Converter for System

Interconnection and Distributed Energy Integration

C. DUFOUR

L.-A. GRÉGOIRE

J. BÉLANGER

Opal-RT Technologies (Canada)

SUMMARY

Thyristors-based converters are still today the most common type of HVDC links. Modular Multilevel

Converter based HVDC links are often considered for lower power rating projects like off-shore wind

farms. Both approaches present challenges in both the design and the testing of proposed circuit

topologies and control & protection system design. Conventional real-time simulators used by most

power electronic system manufacturers for testing thyristor-based AC-DC converter systems in HIL

mode encounter difficulties or simply cannot simulate MMC-based circuits composed very large

number of fast power electronic devices. This paper will demonstrate new solvers methods adapted

for both thyristors and MMC-based HVDC links. In the case of thyristors-based HVDC, a new solver

called State-Space Nodal implements an efficient real-time method to deal with the numerous

switched filter banks and valves groups found in these apparatus. The real-time and parallel simulation

of Modular Multilevel Converters with hundreds of switches, which is very difficult or impossible

with conventional solvers, is made with a pragmatic fixed-causality solver. System transients and

dynamic performance under several operating conditions evaluated in HIL mode with a prototype

controller-in-the-loop composed of several hundred of I/O connections will also be presented, using

the RT-LAB real-time digital simulator.

KEYWORDS

Real-time simulation, HVDC systems, Modular Multilevel Converter, Thyristor Converter, RT-LAB.

christian.dufour@opal-rt.com

1. INTRODUCTION

In 2012, the Rio Madeira HVDC link of Brazil, connecting the Amazonas to the São Paulo area, will

be the longest of its kind with a DC line length of more than 2,500 km. This link will mainly use

thyristors rectifiers and the link will have a capacity of more than 3GW. At the same time, a 2,000

GW, 64 km DC-link between Spain and France was recently announced to increase the mesh of the

main Europe grid. In this case, a more recent technology based on modular multilevel voltage

converter was selected.

High Voltage Direct Current transmission (HVDC) has indeed evolved and proven useful over the

years in overcoming many of the limitations inherent in AC transmission, while providing a cost

efficient alternative for long distance power transmission. Also, advancements in the HVDC

topologies have in turn forced the evolution of many other technologies, particularly fast-switching

power electronic devices.

As the number of HVDC projects around the world continues to grow, power system engineers must

concentrate on solving inherent problems that may surface. The investment on a robust and fast realtime simulator, that would allow for extensive studies of AC-DC interactions as well as control

scheme testing and approval, is therefore important to consider.

The most common type of HVDC link is build around thyristors valves technology and most often

consist on bipolar links with each pole consisting of 12 thyristors rectifier/inverter stations. At the ACsides, switched filter banks insure proper harmonic filtering and reactive control.

Recent advancements in power electronic technologies have fuelled the development and use of

Voltage-Source Converter (VSC)-based HVDC links. Insulated-Gate Bipolar Transistors (IGBT) are

now used in many VSC topologies to convert and carry DC power. A rapidly emerging VSC topology

is the Modular Multilevel Converter (MMC), which present several advantages such as low harmonic

content and excellent robustness in case of module malfunction. The switching frequency of such

devices presents a great challenge for developers of real-time simulation technologies and tools. In

fact, simulated frequencies of interest are pushing the limits of the computation capabilities of realtime simulators, which utilize fixed time-steps. And, as for the thyristors-based HVDC systems, the

number of switches is alone a great challenge for real-time simulation.

This paper will address the challenge of real-time simulation of these two types of HVDC links: linecommutated HVDC link based on thyristors, and Modular Multilevel Converter (MMC) HVDC links.

2. MODULAR MULTILEVEL CONVERTER (MMC) IGBT-BASED HVDC

Modular Multilevel converter (MMC)-based HVDC link[1] are a rapidly emerging technology for DC

current transport. They are Voltage Source Converters, as 3-level NPC-clamped IGBT inverter

(HVDC Light), and so can minimize filtering requirements and add flexibility to the active/reactive

control of the DC links. MMC HVDCs have the additional advantage of being very reliable and

maintainable by their modular nature: the links can continue to work correctly when a module fails

and even allow the replacement of this module without shutting down the link. This is an important

issue in site that are difficult to access like off-shore wind-farms for example.

1

2.1. Real-time

time simulation of a 180 module 720 switch MMC

MMC-based DC-link

link

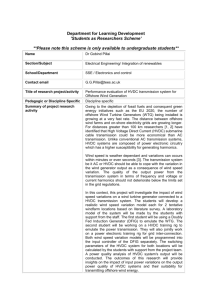

In this study, a real-time

time digital simulation of an MMC-based

MMC

back-to-back bipole HVDC

interconnecting two AC networks is presented. Such ac-dc-ac

ac

ac converter systems can be used, for

example, for low-voltage

voltage converters used in the integration of distributed generation systems, such as

wind farms.

In the system presented in this paper, the sending-end and receiving-end

end converters, as well as the

sending-end controller, are modelled together on the same multi-core real-time

time digital simulator. The

receiving-end

end controller is simulated in a separate simulator and interconnected through IOs and

cables, enabling HIL testing of an MMC. The transformer models include their respective core

saturation characteristics, providing for a realistic evaluation of the performance of the converters in

the face of ferromagnetic nonlinearities.

Fig. 1 60-level

60

MMC HVDC link and external controller

Solver

The complete model is simulated in SimPowerSystems with ARTEMi

ARTEMiS real-time plug-in.

in. The

ARTEMiS solver will be explained in more depth in the next section. A key part of this model is the

MMC modules which are simulated

mulated using a fixed-causality

fixed

solver [2] with high-impedance

impedance capability.

In order to efficiently compute the capacitor voltage of each cell, a few things can be pointed

ointed out. A

cell is considered turn ON when the capacitor is connected in the circuit. When the cell is turn OFF,

the current goes in the lower switch and the voltage capacitor stay the same. The ccurrent

urrent is the same

for all the cells in the

he upper arm and the lower arm, all the capacitor has the same value, in farad. For

these reasons, there is only one voltage variation to compute for all the cell turn ON. This simplify a

lot the computing load, but SPS does not allow such simplification, therefore using Simulink block

bloc

and matrix computing of MATLAB

MATLAB,, our own block was design. Using this method, a computing time

of 7µs can be achieved

Hardware set-up

The complete MMC HVDC link and AC-feeder

AC

circuits were simulated on a RT-LAB

LAB simulator using

the latest dual hexa-core PCs, for a total of 12 available cores. This model was developed for

Hardware-In-the-Loop

Loop (HIL) simulation in which one of the MMC stations will be controller by a

controller implemented on separate and independent RT-Lab

RT

simulator. The other MMC station has

its controller simulated within the model. This

T is used to test the equivalent of a real physical

controller connected to the real-time

time simulated MMC system. The external controller requires a total

2

of 360 digital signals and 180 analog signals. This setup was done using eMEGAsim simulator with

OP5142 board from OPAL-RT.

RT. OP5142 board are used to manage the IOs. One of these boards can

ca

handle a maximum of 64 analog and 128 digital, therefore 3 boards per simulator are required. Fig. 2

shows the tow simulators and their expansion box for the extra

extra OP5142. The controller uses a dual

quad core 2.4Ghz CPU, the plant uses the dual six core 3.3GHz from Intel.

Fig. 2 RT-LAB

LAB simulator connections for the real-time

time simulation of MMC link (controller is on the left

simulator, MMC on the right simulator)

Real-Time Simulation Results

Fig. 3 Simulation results of the MMC (real-time

(real

vs. SPS 1µs off-line) AC-side

side fault case.

3

The results presented here are compared with a reference obtained using SimPowerSystems from

Simulink, with a time step of 1 µs. The Figure below shows the result when a fault is applied on the

AC side. This is one of the worst conditions that can be applied to a system, both model, the one in

real-time using our solver, and the one using SPS has very similar results. See [5] also.

Real-time simulation timings

Table I Real-time simulation’s timing performance of MMC DC-link

CPU frequency3.3 GHz

cpu

subsystem

Ts

Tcal

Ts min

(microseconds) (microseconds) (microseconds)

1

Ac grid

20

2

2

Arm-A left

20

3

3

Arm-B left

20

3

4

Arm-C left

20

3

5

Arm-A right

20

3

15

6

Arm-B right

20

3

7

Arm-C right

20

3

8

Dc link

20

1

9

PWM gen left

20

5.4

10

PWM gen right

20

5.4

11

controller

20*5

3.8

Table I shows the computation time required to simulate the model in HIL simulation. Ts, the third

colum gives the computation time, Tcal is the required time to compute the local solution on each CPU

and the last give the required time for accessing the IOs and the communication between CPU.

3. LINE-COMMUTATED THYRISTOR-BASED HVDC

‘Classic’ thyristor-based HVDC link have been around since the 70’s and are still being built these

days. This type of HVDC link benefits from a greater power capability than their VCS counterparts,

although improvements in semi-conductor technology tend to slowly close this gap.

From a simulation point of view, this type of installation requires the use of different solvers than

MMC for many reasons, mainly related to switches. Thyristor-based HVDC systems requires many

filters, most of them switched, on the AC- and DC-sides. On the AC side notably, these filters are

important for reactive power control, i.e. AC voltage level support. Because of the presence of such a

high number of switch in the circuit, and also because this switches cannot be simulated like MMC

switches, a State-Space Nodal (SSN) solver was developed.

3.1. State-Space Nodal Solver

The State-Space Nodal (SSN) method described hereafter is a generalisation of the Dommel method

and uses arbitrary sized state-space described clusters of electrical elements and combines them with

the nodal admittance matrix using an EMTP-like nodal method.

In the classic EMTP method, a fixed set of basic elements (such as R, series RL, series RLC,

transformer) are discretized individually. Their discretized equivalents are solved simultaneously with

the use of a nodal admittance matrix. Because the basic elements are small and numerous, the resulting

nodal matrix can be huge and therefore pose a challenge during real-time simulation. The SSN solver

makes use of pre-grouping of the network to be simulated to obtain a reduced size nodal matrix.

4

In SSN, the discrete equations of all groups is directly derived from their ABCD state-space

representation. From the continuous Laplace state-space equations, the discrete equations are first

found through the use of the trapezoidal or higher order rule of integration. These groups’ discrete

equations are then inserted into a nodal matrix like EMTP from which the complete netwkr solution

can be found.

Suppose there is a group of resistance, inductance, capacitance and transformer sources, and other

electrical elements connected to a terminal of unknown voltage and current (a ‘nodal connection

point’). The state-space equation exists:

x ′ = Ak x + Bk u

y = C k x + Dk u

(1)

where

x: states of the system

u: inputs of the system

y: output of the system

Ak , Bk , Ck , Dk : state space matrices corresponding to the k-th permutation of switches and

other piecewise linear element segments.

When discretized, these equations result in:

xn+1 = Ad xn + Bd 1u n + Bd 2u n+1

y n +1 = C d xn +1 + Dd u n+1

(2)

where:

Ad, Bd1, Bd2, Cd, Dd : discrete state matrix for the present pattern of binary switches modeled inside the

group. The trapezoidal rule of integration will produce Bd1=Bd2. Subscript n and n+1 indicate the time

instants. The k subscript was dropped for the sake of simplicity.

un+1: unknown sources of the state-space model at the present time n+1. This represents the nodal

voltage or the current injection that can only be resolved by simultaneous solution of all groups

connected to the nodes of the network.

yn+1: nodal output of the state-space model. This is the voltage output or current output of the group

that needs to be solved simultaneously along with all groups connected to the system nodes.

The following relation can now then be derived:

yn+1 = Cd {Ad xn + Bd1un + Bd 2un+1}+ Ddun+1

(3)

Now if y is a current and u is a voltage, the equation can be viewed as a current injection known from

past history and forced internal source known at present time n+1:

I hist = Cd { Ad xn + Bd 1un }

(4)

in parallel with a discrete admittance, i.e. discrete ratio of input-output values,

Y = Cd Bd 2 + Dd

(5)

Similar deduction can be made if the nature of y and u are reversed. The method can be generalized to

state-space groups with internal source. From the above equations, the formation of a nodal admittance

matrix is the same as in the classic EMTP method. See REF for more details.

5

Switch management in Real-Time applications

A key aspect of the SSN method lies in the management of switches. In SNN, the switches are treated

in two steps:

Inside the state-space group, the circuit modes are precomputed for all possible combinations of

switch positions. For a group with 6 switches for example, a set of 2^6=64 ABCD discrete matrices

will be pre-computed before entering the real-time loop.

In the global nodal matrix, all the groups ‘discrete resistance’ matrix are assembled dynamically,

within the real-time loop, depending on the switch positions of each group at a particular time. This

step produce a Y=VI matrix problem for which a LU triangularisation is made at each time step.

With a mixed method composed of nodal and state-space solutions, an effective and balance solution

can be found. Consider a system with a three-phase connection point in the middle (Fig. 4, lower part)

using the SSN method.

Brk0

xn+1=

Ak

π

xn +

π

Bk

SSN method with 2 groups of x/2 states each

Brk0

Brk1

un+1

matrix sets

k=1...64

xn+1=

A1m

A2n

π

U_no

State space method with x states

xn +

I_non+1= Y3,3

π

Brk1

B1m

B2n

un+1

matrix sets

m=1...8

m=1...8

u_non+1

Fig. 4 Large network state-variable allocation: states-space (upper) , state-space nodal (lower)

In the SSN method, two SSN groups separated by 3 nodal connection points (separating the complete

network in two equal part let say) can be defined. In this case, the algorithm would imply 2 state-space

system iterations with x/2 state variables each, plus a 3x3 nodal matrix inversion (for the sake of

clarity, the dependence of the 2 pi-line section capacitance at the nodal junction is neglected). This

would cut approximately by half the total number of operations required by the state-space iterations

and add a 3x3 matrix inversion. Indeed, Fig. 4 shows that the SSN method makes the complete statespace equations block-diagonal by virtue of the decoupling induced by the approach. The decoupling

is partial, however, as the nodal solution links all parts of the network equations. Using a single CPU

approach, the computational gain can approach a factor of 2 if the state-space iteration becomes more

important, in comparison to the same 3x3 matrix inversion.

Furthermore, the problem of memory storage of switch permutations is solved here: each group

contains only the pre-calculated set of matrices for the switch contained within the groups. Taking

again the specific example of Fig. 4, which is composed of two three-phase breakers, full precalculation of circuit modes in the standard state-space approach would require the storage of 2^6=64

permutations of states-space equations of x states. In the SSN approach, two sets of 2^3=8 system

matrices need to be stored (one for each group), thus drastically reducing memory requirements.

Separation of switches is always possible because they can be modeled as a separate group in the

proposed method. In that case, only the D matrix subsystem is non-empty, and the group admittance is

included directly in the global admittance matrix in way similar to standard nodal method.

6

3.2. Simulation of a bipolar 12-pulse HVDC link with switched filter banks.

The SSN solver is built-in the ARTEMiS real-time plug-in for SimPowerSystems. SSN is used to

simulate in real a complete 12-pulse bipolar HVDC link with switched filter banks. This test model is

a 2000 MW (500 kV, 2 kA at each pole) HVDC link used to transmit power from a 500 kV, 5000

MVA, 60 Hz network to a 345 kV, 10 000 MVA, 50 Hz network. The rectifier and the inverter are 12pulse converters and the link is bipolar. The rectifier and the inverter are interconnected through two

300 km distributed parameter line using 0.5 H smoothing reactors. The transformer tap changers are

not simulated and fixed taps are assumed. The tap factor used on the primary voltage is 0.90 on

rectifier side and 0.96 on inverter side. Reactive power required by the converters is provided by a set

of capacitor banks plus 11th, 13th and high pass filters for a total of 600 MVAR on each side. These

capacitors and filters can be switched; each station has 7 switched banks.

Line (300 km)

transfo

6-pulse

thyristor

rectifier

6-pulse

thyristor

rectifier

500kV

60 Hz

AC filters (600 MVars)

345kV

50 Hz

AC filters (600 MVars)

Line (300 km)

Fig. 5 Bipolar 12-pulse HVDC link with switched filter banks

In Fig. 5, the SSN state-space groups are indicated by the colors. Stations (with pair of poles) on both

sides of the lines are simulated on two different cores of the RT-LAB simulator. The natural delay of

transmission line enables this decoupling. Each station circuit, comprising the two 12-pulse rectifiers

are each simulated with a single SSN solver instance, without decoupling delays. To increase the

simulation speed, decoupling at the transformers secondary has been demonstrated to be efficient and

accurate [4].

Simulation Results

As a test case, we made the DC-link energization. Then, when the DC-link reached its nominal

current, we began to connect filter banks 1 to 6 at 0.4 sec. intervals, followed by simultaneous

disconnection off all banks at 5 sec. As expected and shows in Fig. 6 , each time a filter bank is put

on-line, it provides the AC network reactive power, i.e. raising the AC voltage amplitude and DC-link

controllers reacts by raising the firing angle to keep the DC-link current at nominal level.

7

Fig. 6 Bipolar DC-link filter bank switching test

The SSN method implements ‘Inlined Thyristor Valve Compensation’ algorithm (ITVC). The ITVC

method is used to maintain the simulation accuracy even when the thyristor switching occurs between

time-steps. Fig. 7 shows the effect of the ITVC algorithm: it decreases by 50% the jitter caused by the

sampling of thyristors gate signal by the fixed-time step simulation time frame. It must be understood

that this simulation imprecision, with ITVC algorithm is turned off, is caused by fixed step sampling

and would be similar in any fixed step software like EMTP, PLECS or PSCAD. The figure also

shows a very regular current pattern with ITVC in action.

Fig. 7 ITVC algorithm effect on the DC-current of the HVDC link

8

Table II: Real-time simulation results of the bipolar DC-link with switched filter banks.

cpu

1

2

3

CPU frequency 3.3 GHz

Ts

Tcal

Ts min

(microseconds) (microseconds) (microseconds)

Rectifier pole

49

46

49

1&2

Inverter pole

49

46

1&2

Controllers

45

40

subsystem

The bipolar HVDC link with switched filters can be simulated at a time step of 49 µs on 3 cores of a

3.3 GHz PC running under RT-LAB 10.1.

CONCLUSION

This paper detailed the real-time simulation of two different types of HVDC links, namely a bipolar

12-pulse HVDC link with switched filter banks and a 60-level MMC-based HVDC links.

In the case of the MMC HVDC, the numerous switches were solved using a fixed-causality solver

with a high-impedance capability. This is a very pragmatic approach that was demonstrated very

efficient for this difficult problem. The 12-pulse bipolar HVDC link was solved using a more ‘classic’

approach, very similar to the EMTP approach, but with state-space pre-grouping of elements

combined with a nodal method to better deal with the numerous switches in the model (88 breakers,

thyristors and faults switches).

The RT-LAB simulator was used to obtain real-time results. The simulator is not only fast enough to

compute system differential equation but also provides a sufficient number of I/Os point for this type

of HIL studies. The MMC case demonstrated the simulator capability to handle several hundred of I/O

connection in HIL mode with a MMC controller running on a 2nd RT-LAB system, 360 digital inputs

and 180 Analog outputs in the case presented. RT-LAB system can be configured to handle even more

I/Os, if it is required to control both MMC stations by HIL.

BIBLIOGRAPHY

[1] M. Hagiwara, H. Akagi, "PWM control and experiment of modular multilevel converters," Power

Electronics Specialists Conference, 2008. PESC 2008. pp.154-161, June 15-19, 2008

[2] M. Harakawa, C. Dufour, S. Nishimura, T. Nagano, “Real-Time Simulation of a PMSM Drive in

Faulty Modes with Validation Against an Actual Drive System”, Proc. of the 13th European

Conference on Power Electronics and Applications(EPE-2009), Barcelona, Spain, Sept. 8-10, 2009

[3] C. Dufour, J. Mahseredjian , J. Bélanger, “A Combined State-Space Nodal Method for the

Simulation of Power System Transients”, Paper accepted for publication in IEEE Transactions on

Power Delivery (2011)

[4] C. Dufour, S. Abourida, J. Bélanger,V. Lapointe, “InfiniBand-Based Real-Time Simulation of

HVDC, STATCOM, and SVC Devices with Commercial-Off-The-Shelf PCs and FPGAs”, Proc.

of IEEE Industrial Electronics Society (IECON-06), Paris, France, November 7-10, 2006

[5] J-N. Paquin, C.Dufour. L.-A. Grégoire, J. Bélanger “Real-Time Simulation of a 180-cell 720switch Modular Multilevel Converter for HVDC Transmission Studies”, Proc. of CIGRÉ Canada

Conference on Power Systems, Vancouver, October 17- 19, 2010.

9