Diam-MEMS-Pack_Zhu - College of Engineering, Michigan State

advertisement

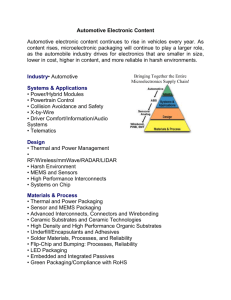

396 JOURNAL OF MICROELECTROMECHANICAL SYSTEMS, VOL. 13, NO. 3, JUNE 2004 The Fabrication of All-Diamond Packaging Panels With Built-In Interconnects for Wireless Integrated Microsystems Xiangwei Zhu, Dean M. Aslam, Senior Member, IEEE, Yuxing Tang, Brian H. Stark, and Khalil Najafi, Fellow, IEEE Abstract—To explore polycrystalline diamond (poly-C) as a packaging material for wireless integrated microsystems (WIMS), a new fabrication technology has been developed to fabricate thick WIMS packaging panels with built-in interconnects. An ultrafast poly-C growth technique, used in this study, involves electrophoresis seeding and filling of dry-etched Si channels by undoped poly-C followed by removal of Si. A second layer of highly B-doped poly-C, which acts as a built-in interconnect, is deposited on the backside of undoped poly-C layer. The lowest resistivity values demonstrated on control samples are in the range . The results show that, by increasing the from 0.003 to 0.31 -wide Si channels, poly-C growth areas through the use of 2the poly-C growth time can be reduced by a factor in the range from 2.75 to 10.5 depending upon the aspect ratio of Si channels. The poly-C packaging technology, which is expected to provide new structures/concepts in MEMS/WIMS packaging, is being reported for the first time. [1127] cm m Index Terms—Built-in interconnects, diamond dry etching, diamond MEMS, MEMS packaging, polycrystalline diamond, poly-C technology, ultrafast diamond growth. I. INTRODUCTION I N THE PAST few years, a number of studies have focused on MEMS packaging. MEMS packaging is so application-specific that different MEMS applications require different types of packages, such as metal packages, ceramic packages and thin-film multiplayer packages, to optimize microsystems in terms of cost, performance and reliability [1]. Closely tied with the IC silicon-processing technology, which is widely used currently, MEMS packaging can take advantage of these mature chip-scale packaging techniques, including flip-chip and ball-grid-array techniques [2]–[4]. Recently, the developments in MEMS area have led to growing interests in MEMS packaging at wafer level. Various approaches in this area can be characterized into two categories: integrated encapsulation process [5], [6] and wafer bonding process [7]. Unfortunately, Manuscript received August 4, 2003; revised December 8, 2003. This work was supported by the Engineering Research Centers Program of the National Science Foundation under Award EEC-9986866. A version of this paper, “AllDiamond Packaging for Wireless Integrated Micro-System Using Ultra-fast Diamond Growth,” was presented in IEEE MEMS’ 2003, Japan, January 2003. Subject Editor L. Lin. X. Zhu, D. M. Aslam, and Y. Tang are with the Electrical and Computer Engineering, Michigan State University, East Lansing, MI 48824 USA (e-mail: zhuxiang@egr.msu.edu). B. Stark and K. Najafi are with the Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109 USA. Digital Object Identifier 10.1109/JMEMS.2004.828739 while the integrated processes suffer from the drawbacks of process-dependency, the wafer bonding process suffers from the requirement of high temperature and flat surface of bonding. To protect MEMS device on the wafer-level, a unique approach of MEMS packaging by localized heating and bonding was proposed [8]–[10]. Applications of wireless integrated microsystems (WIMS) in biomedical and environmental systems places special requirements on WIMS packaging. To protect WIMS from external environments, an ultrathin hermetic package using electroplated gold [11] and a hermetic glass-silicon package using anodic bonding technique [12], [13] have been reported. The integration of WIMS devices into a system also requires multichip packaging and three-dimensional (3-D) packaging technologies. While the multichip module (MCM) technology has progressed rapidly in the past decade [14], a compact multisubstrates package with a zero-insertion-force (ZIF) microconnector is being developed for WIMS applications [15]. The development of conventional packaging technologies are emphasizing the need for new material technologies, especially for harsh environments. WIMS packages are expected to provide MEMS devices and on-chip circuits with functions such as mechanical support, protection from environment, electrical interconnection and thermal management. Due to its extreme hardness, chemical and mechanical stability, large band gap and highest thermal conductivity, chemical vapor deposited (CVD) poly-crystalline diamond (poly-C) is expected to be an excellent material for WIMS packaging. As a new emerging technology, poly-C MEMS technology has been intensively studied recently. The fabrication of freestanding diamond structures using Si molds [16], IC-compatible technique [17] and diamond-on-silicon microacceleration sensors [18] have been reported. However, the application of poly-C films in packaging is mostly focused on thermal management as heat sink [19]. The development of a WIMS package with embedded interconnects, in which both mechanical support and interconnects are made completely out of poly-C, is reported in this paper. Although many poly-C deposition methods, including the dc-arc jet CVD [20] and multiple-pulsed laser process [21], have been developed for high-deposition rate applications, the typical poly-C deposition systems (Hot-filament CVD and Microwave Plasma CVD) (see have a low growth rate in the range from 0.1 to 10 Table I and [22]). The multiple-pulsed-laser process is very costly, and dc-arc jet CVD involves relatively small substrate and contaminations. Therefore, they are not size 1057-7157/04$20.00 © 2004 IEEE ZHU et al.: FABRICATION OF ALL-DIAMOND PACKAGING PANELS FOR WIRELESS INTEGRATED MICROSYSTEMS 397 TABLE I COMPARISON OF DIFFERENT POLY-C DEPOSITION METHODS Fig. 2. Fabrication sequence for ultrafast diamond growth: (a)–(c) Si-mold fabrication; (d) diamond seeding; (e)–(f) first poly-C layer deposition; (g)–(h) second poly-C layer deposition and surface polishing. Fig. 1. Concept of an all-diamond package using flexible metal ribbons for interchip connections. compatible with a MEMS type processing. To keep the fabrication cost of thick poly-C films for WIMS package low, a new fabrication technology is desired. In this paper, an ultrafast poly-C panel fabrication technology has been developed to produce an inexpensive package for WIMS (see Fig. 1). The built-in interconnects in the panels can be used for interchip as well as for chip-to-package communications by using flexible metal ribbons. For the chip-to-package connections hole can be laser-drilled [23] and filled with metal as shown in the top panel in Fig. 1. This technology allows the formation of very thick and high aspect ratio structures, and, as a result, one can fabricate thick structures faster than a conventional fabrication process for poly-C. In a typical panel fabrication process, high aspect ratio channels etched in Si are filled with poly-C using microwave plasma CVD (MPCVD). Si is then chemically dissolved and another layer of poly-C is grown on the backside of the first layer to fabricate 20–100- -thick poly-C panels. The second layer of poly-C is boron doped with resistivities in the range from 0.003 to 0.31 Ohm-cm. The growth time for the new technique is reduced by a factor in the range from 2.75 to 10.5, depending upon the aspect ratio. The use of such a fast growth technique to fabricate poly-C panels with built-in interconnects, with Fig. 3. Electrophoresis setup. potential applications to WIMS packaging, are reported for the first time. II. EXPERIMENTAL PROCEDURE In a typical poly-C gowth on nondiamond substrates diamond seeding (nucleation sites) is required. High doping and low resistance metal/poly-C contacts are important for poly-C panels. A testchip was designed to study these and other parameters important for the panel fabrication. A. Test Chip Design A test chip was designed and fabricated using the fabrication process illustrated in Fig. 2. Different structures (wells and 398 Fig. 4. JOURNAL OF MICROELECTROMECHANICAL SYSTEMS, VOL. 13, NO. 3, JUNE 2004 Diamond seeding results: (a) uniform seeding,; (b) nucleation density of 1.5 channels) are etched in Si using DRIE. All structures on the chip are 20- -deep and have feature sizes in the range from 2 to , resulting in different aspect ratios. All structures on the 20 chip are used to study ultrafast poly-C film growth while the channel structure is also used to study the fabrication of poly-C panels with built-in interconnects. B. Diamond Particle Seeding To provide seeding before poly-C growth, diamond powder with average particle size of 100 nm can be applied inside Si channels using either the 1) diamond-loaded photoresist (DPR) technique [24] or 2) electrophoresis seeding method [25]. However, in the current work, the DPR technique did not provide high enough seeding density inside the 2- -wide channels. Consequently, the electrophoresis seeding method was used to provide high seeding density in the channels [26]. The Si molds were rinsed in isopropyl alcohol (IPA, from J.T. Baker, 99.9%) and suspended vertically in a solution, which was prepared by mixing 0.15 g of diamond powder (Engis, Hyprez diamond powder, size 100 nm) in IPA. In the electrophoresis setup, shown in Fig. 3, the separation between an iron cathode and the Si mold was 1.5 cm. A 75-V bias was applied to the silicon mold for 30 or 60 min in an ultrasonic bath (Branson 1200). The positive charge on the wafer has been shown to attract negative surface groups on diamond in organic solvents [27]. The SEM pictures of diamond seeding results are illustrated in Fig. 4. 210 cm ; (c) and (d) seeding inside channels. TABLE II POLY-C DEPOSITION PARAMETERS OF MPCVD parameters, which are standard conditions for this laboratory [28], are listed in Table II. Deposition times are in the range from 5 to 48 h. After the first layer of poly-C was fabricated, the Si substrate (1:1:2). The freewas etched away using standing poly-C structures are shown in Fig. 5. The second layer of poly-C was grown on the backside of the first layer using the standard growth condition (see Table II). To fabricate a poly-C film with built-in interconnects, trimethylboron (TMB) diluted in hydrogen (0.098%) was introduced into the reaction gas mixture during the growth of the second layer of poly-C. The built-in interconnects were fabricated by dry etching the surface of doped poly-C layer [see Fig. 2(h)]. Raman spectroscopy performed on deposited poly-C films displayed carbon bonding) at 1332 a sharp diamond peak ( indicating a good diamond quality (a very high ratio) as shown in Fig. 6. It may be pointed out that the technology of low-resistance metal-diamond contacts has been extensively investigated and is currently well established [29]–[34]. D. Poly-C Etching Using Microwave ECR System C. Poly-C Growth The diamond seeded Si mold was placed in an MPCVD chamber to grow the first layer of poly-C. The deposition Since diamond is an extremely hard and inert material, wet chemical etching of diamond is not possible. The microwave electron-cyclotron-resonance (ECR) system has been reported ZHU et al.: FABRICATION OF ALL-DIAMOND PACKAGING PANELS FOR WIRELESS INTEGRATED MICROSYSTEMS Fig. 5. 399 m channels array, (b) 4-m channels array, (c) 10-m channels array, and (d) 20-m wells array. Freestanding poly-C microstructures: (a) 2- TABLE III ECR PLASMA ETCHING PARAMETERS Fig. 6. Raman spectrum of poly-C film. to perform ECR plasma dry etching of CVD poly-C [35]. The ECR systems differ from other microwave systems in their capability of coupling microwave power to the plasma at a very low pressure of around 1 mtorr resulting in surface-damage free processing, high anisotropic etch rate and excellent uniformity [36]. The boron-doped poly-C layer was dry etched using Plasgas mixture environmaQuest ECR system in an ment [37]. The optimized parameters for the plasma dry etching of doped poly-C are list in Table III. III. RESULTS AND DISCUSSION A. Ultrafast Fabrication Model The aspect ratio of structures, which affects the total available growth surface, plays an important role to reduce the poly-C Fig. 7. Ultrafast growth model: (a) first poly-C deposition and (b) second poly-C deposition. film fabrication time. As shown in Fig. 7, DRIE-etched channels (with spacing between the channels equal to the width of the channels) lead to a relatively large poly-C growth area. After the deposition of the first layer of poly-C, silicon is chemically dissolved and a second layer of poly-C is deposited on the back- 400 JOURNAL OF MICROELECTROMECHANICAL SYSTEMS, VOL. 13, NO. 3, JUNE 2004 m Fig. 8. Twenty to 35- -thick diamond films fabricated by ultra-fast method using: (a) 2 wells array. side of the first layer. For a specified thickness, the higher the aspect ratio of channel, the shorter the fabrication time. are the actual poly-C growth Assuming that , , and rate, channel width and height, respectively, the time to fill the channel is given by m channels, (b) 6 m channels, (c) 10 m channels, and (d) 10 m TABLE IV FABRICATION TIME OF ULTRA-FAST GROWTH MODEL (1) where the actual deposition thickness is given by (2) After double-side growth (see Fig. 7), the total fabrication time is: (3) The total thickness of freestanding poly-C is given by (4) If the effective diamond growth rate, , (3) and (4) give . Thus, the higher aspect ratio leads to shorter fabrication time. To test this model, a series of poly-C panel fabrication deep) with experiments were performed on channels (20 different aspect ratios. By defining as the growth time for a typical poly-C growth method (on a flat substrate), a comparison of and is shown in Table IV. The total thickness of the panels, , was measured from SEM pictures as shown in Fig. 8, and was measured for each experiment. The poly-C growth rate of 0.25 was , according to (6), is given used to calculate . The ratio of by , is defined by (7) (5) (6) is the aspect ratio. Therefore, the diamond where . In other growth rate will be increased by a factor of words, the fabrication time will be shortened by a factor of As shown in Fig. 9, the experimental values of , comvalues, correlate well with the puted using the measured theoretical values computed using aspect ratios (see Table IV). B. Poly-C Panel With Built-In Interconnects Boron is widely used for in-situ doping of diamond. An intensive study of boron-doped poly-C was conducted to find the ZHU et al.: FABRICATION OF ALL-DIAMOND PACKAGING PANELS FOR WIRELESS INTEGRATED MICROSYSTEMS Fig. 9. 401 Comparison of experimental and theoretical values of (1 + AR). Fig. 11. Fabrication process of built-in interconnects. for the interconnect layer and the samples, is 0.31 for the undoped section of the panel. As 2.34 shown in Fig. 10, the resistivity of interconnects can be reduced . Further polishing experiments are needed to to reduce the surface roughness of the dry-etched poly-C film. Fig. 10. Poly-C resistivities for 1-m-thick films deposited at 700 C. The inset shows resistivity data from an earlier study (annealing temperature is 600 C). lowest resistivities, using trimethylboron (TMB) diluted in hydrogen (0.098%) as the source of doping. The resistivity of boron doped poly-C films varies with the doping concentration, deposition temperature, grain size and post-growth anneal. The films synthesized in hydrogen plasma contain a hydrogenated surface layer which is approximately 20-nm thick [38]. The surface layer shows p-type conductivity even in undoped films. The postgrowth anneal will dehydrogenate the surface layer but will not affect the boron concentration in the film. Consequently, anneal will affect resistivity of poly-C only for lightly doped or undoped films, as seen in Fig. 10. The study of the resistivity of boron doped poly-C layer (see Fig. 10), conducted on control samples fabricated in the current work, reveals the lowest resistivity of 0.003 Ohm-cm. As evident from an earlier study [39] focusing on the effect of poly-C growth temperature on resistivity, resistivity values lower than 0.003 Ohm-cm are achievable as shown in the inset of Fig. 10. To fabricate poly-C panel with built-in interconnects, the second layer of poly-C is highly doped with boron. The fabrication process is shown in Fig. 11. The built-in interconnects isolated by undoped poly-C layer can be fabricated after the surface of the doped poly-C layer is dry etched down to the line labeled as “polishing interface” indicated in Fig. 11. The ECR dry etching parameters are shown in Table III. A comparison of poly-C panel before and after ECR plasma etching is shown in Fig. 12(a) and (b). The top surface of doped poly-C layer was etched down until the doped poly-C channels are isolated by the undoped poly-C layer, as shown in the Fig. 12(c) and (d). The resistivities of this poly-C panel, measured on one of C. Filling of Si Molds Area that requires an improvement in the current work is the partial filling of Si molds for channels with high aspect ratios. Figs. 8 and 12 both reveal key holes (voids) formed in the high-aspect ratio channels due to the increasing edge effect restricting the transportation of growth-related plasma species into the bottom areas of the channels. This premature filling of high aspect ratio channels, though a problem for the fast growth process, can lead to poly-C channels for microfluidic applications [25]. To find the highest aspect ratio of a channel which yields best poly-C filling, a study was conducted to deposit poly-C inside channels with aspect ratios in the range from 1 to 10. As shown in Fig. 13(a) and (b), channels with aspect ratio can be totally filled but the channels with higher aspect ratios lead to voids as see in Fig. 13(c) and (d). Therefore, to fabricate a poly-C panel with complete filling, channels with aspect ratio less than three should be applied to avoid any reliability concerns. D. Assembly of Poly-C Panels To build an all-diamond WIMS package, it is important to develop a diamond-diamond bonding technology. Although diamond brazing techniques [40] were developed earlier, the bonding technology of two poly-C samples is new. The poly-C film bonding process concept is shown in Fig. 14. The top film, with trench structures, was put on the substrate film. The trenches on the top film allow reaction gas to flow into inner areas. Although the CVD deposition of poly-C inside the trenches bonded the two films, some problems were also identified in this study. As shown in Fig. 15, for areas at the edge and at the front of the trenches, where sufficient reaction gases are available, 402 JOURNAL OF MICROELECTROMECHANICAL SYSTEMS, VOL. 13, NO. 3, JUNE 2004 Fig. 12. SEM image of poly-C panel with built-in interconnects: (a) poly-C panel before dry etching, (b) poly-C panel after dry etching, (c) top view of poly-C panel, and (d) side view of poly-C panel. Fig. 13. Filling properties in channels with different aspect ratio: (a) a channel with aspect ratio 2, totally filled; (b) a channel with aspect ratio 3, totally filled; (c) a channel with aspect ratio 4, void formed; (d) a channel with aspect ratio 5, void formed. the CVD bonding between two films is very successful. How), the ever, due to the small size of trenches ( flow of poly-C growth related species into the deeper areas of the trenches is limited. Thus, the CVD bonding mostly happened near the front region of the trench, which is approxialong the trench, as shown in Fig. 15(a). Due mately ZHU et al.: FABRICATION OF ALL-DIAMOND PACKAGING PANELS FOR WIRELESS INTEGRATED MICROSYSTEMS Fig. 14. Bonding process concept of poly-C films: (a) before and (b) after poly-C bonding. Fig. 15. SEM images of two bonded poly-C films bonding. to the lack of reaction gases, there is no bonding between the two films in the deeper areas, as shown in Fig. 15(c). To address this problem, current experiments (which require the design of new masks for the testchip) focus on providing an access-hole array, which will be subject of subsequent publications. IV. CONCLUSION An ultrafast poly-C growth technique, developed to fabricate WIMS packaging panels with built-in interconnects, involves electrophoresis seeding and filling of dry-etched Si channels by undoped poly-C followed by removal of Si. A second layer of highly B-doped poly-C, which acts as a built-in interconnect, is deposited on the backside of undoped poly-C layer. The lowest resistivity values demonstrated on control samples are in the range from 0.003 to 0.31 - . By increasing the poly-C growth areas through the use of 2- -wide Si channels, the poly-C growth time can be reduced by a factor in the range from 2.75 to 10.5 depending upon the aspect ratio of Si channels. The poly-C packaging technology, which is expected to provide new structures/concepts in MEMS/WIMS packaging, is being reported for the first time. 403 REFERENCES [1] B. Stark and R. D. Gerke, Eds., “MEMS Reliability Assurance Guidelines for Space Application,” Jet Propulsion Laboratory, California Institute of Technology, Pasadena, CA, JPL Publication 99-1, 1999. [2] J. Kloeser, E. Zake, Z. Bechtold, and H. Reichl, “Reliability investigations of fluxless flip-chip interconnections on green tape ceramic substrates,” IEEE Trans. Compon., Packag., Manufact. Technol., pt. A, vol. 19, pp. 24–33, Mar. 1996. [3] J. Giesler, G. O’Malley, M. Williams, and S. Machuga, “Flip chip on board connection technology: Process characterization and reliability,” IEEE Trans. Compon., Packag., Manufact. Technol., pt. 8, vol. 17, pp. 256–263, Aug. 1994. [4] D. Suryanarayana, T. Y. Wu, and J. A. Varcoe, “Encapsulant used in flip-chip packages,” IEEE Trans. Compon., Packag., Manufact. Technol., vol. 16, pp. 858–862, Dec. 1993. [5] K. Ikeda et al., “Silicon pressure sensor with resonant strain gages built into diaphragm,” in Proc. Dig. 7th Sensor Symposium, 1988, pp. 55–58. [6] L. Lin, R. T. Howe, and A. P. Pisano, “Microelectromechanical filters for signal processing,” J. Microelectromech. Syst., vol. 7, pp. 286–294, Sept. 1998. [7] B. Ziaie et al., “A hermetic glass silicon micropackage with high-density on-chip feedthroughs for sensors and actuators,” J. Microelectromech. Syst., vol. 5, pp. 166–179, Sept. 1996. [8] L. Lin, “MEMS packaging at the wafer level,” J. Mater. Process. Manufact. Sci., vol. 8, no. 4, pp. 347–349, 2000. [9] , “MEMS post-packaging by localized heating and bonding,” IEEE Trans. Adv. Packag., vol. 23, pp. 608–616, Nov. 2000. [10] Y. T. Cheng, L. Lin, and K. Najafi, “Localized silicon fusion and eutectic bonding for MEMS fabrication and packaging,” J. Microelectromech. Syst., vol. 9, pp. 3–8, Mar. 2000. 404 JOURNAL OF MICROELECTROMECHANICAL SYSTEMS, VOL. 13, NO. 3, JUNE 2004 [11] B. Stark and K. Najafi, “An ultra-thin hermetic package utilizing electroplated gold,” in Proc. Transducers ’01/Eurosensors XV, Munich, Germany, June 2001. [12] B. Stark, M. Dokmeci, T. Harpster, and K. Najafi, “Improving corrosion-resistance of silicon-glass micropackages using boron doping and/or self-induced galvanic bias,” in Proc. IEEE International Reliability Physics Symposium, Orlando, May 2001. [13] T. J. Harpster and K. Najafi, “Long-Term testing of hermetic anodically bonded glass-silicon packages,” in Proc. IEEE 2002 Int. Conference on MEMS, Las Vegas, NV, Jan. 2002, pp. 423–426. [14] J. Butler, V. Bright, R. Saia, and J. Comtois, Extension of High Density Interconnect Multichip Module Technology for MEMS Packaging, vol. 3224, SPIE, pp. 169–177. [15] A. Ucok, J. Giachino, and K. Najafi, “Compact, modular assembly and packaging of multi-substrates microsystems,” in Proc. Transdcuers ’03, Boston, MA, June 8–13, 2003, pp. 1877–1878. [16] H. Bjorkman, P. Rangsten, U. Simu, J. Karlsson, P. Hollman, and K. Hjort, “Diamond microstructure replicas from silicon masters,” in Proc. IEEE 1998 Int. Conference on MEMS, Germany, Jan. 1998, pp. 24–29. [17] M. Aslam and D. Schulz, “Technology of diamond microelectromechanical systems,” in Proc. Transducer’95, vol. 287-PA11, 1995, pp. 222–224. [18] E. Kohn, P. Gluche, and M. Adamschik, “Diamond MEMS—A new emerging technology,” Diamond Rel. Mater., vol. 8, pp. 934–940, 1999. [19] K. A. Moores and Y. K. Joshi, “High performance packaging materials for improved thermal management of power electronics,” Future Circuits Int., no. 7, pp. 45–49, 2001. [20] J. A. Smith et al., “Diamond deposition in a DC-arc jet CVD system: Investigation of the effects of nitrogen addition,” Diamond Rel. Mater., vol. 10, pp. 370–375, 2001. [21] P. Mistry, M. C. Turchan, G. O. Granse, and T. Baurmann, “New rapid diamond synthesis technique; using multiplexed pulsed lasers in laboratory ambients,” Mater. Res. Innovations, vol. 1, no. 3, pp. 149–156, Dec. 1997. [22] A. Lettington and J. W. Steeds, Thin Film Diamond, 1st ed: Chapman & Hall, 1994, pp. 31–51. [23] K. Sienski, D. Schaefer, and R. Eden, “3-D electronic interconnect packaging,” in Proc. IEEE 17th Aerospace Applications Conference, vol. 1, 1996, pp. 363–374. [24] G. S. Yang and M. Aslam, “Ultra-High nucleation for growth smooth diamond films,” Appl. Phys. Lett., vol. 66, pp. 311–311, 1995. [25] J. L. Valdes et al., “Selected-area nucleation and patterning of diamond thin films by electrophoretic seeding,” J. Electrochem. Soc., vol. 138, no. 2, pp. 635–635, 1991. [26] S. Guillaudeu, X. Zhu, and D. M. Aslam, “Fabrication of 2- wide poly-diamond channels using silicon molds for micro-fluidic application,” Diamond Rel. Mater., vol. 12, pp. 65–69, 2003. [27] D. G. Lee and R. K. Singh, “Synthesis of (111) oriented diamond thin films by electrophoretic deposition process,” Appl. Phys. Lett., vol. 70, no. 12, pp. 1542–1542, 1997. [28] G. S. Yang, M. Aslam, K. P. Kuo, D. K. Reinhard, and J. Asmussen, “Effect of ultra-high nucleation density on diamond growth at different growth rates and temperatures,” J. Vac. Sci. Technol. B, vol. 13, no. 3, pp. 1030–1030, 1995. [29] H. Shiomi et al., “Electrical characteristics of metal contacts to borondoped diamond epitaxial films,” Jpn. J. App. Phys., vol. 28, pp. 758–762, 1989. [30] K. L. Moazed et al., “Diamond/metal interfaces,” in Extended Abstract (EA-19): Materials Research Society, 1989, pp. 167–169. [31] S. A. Grot et al., “The effect of surface treatment on the electrical properties of metal contacts to boron-doped homoepitxial diamond film,” IEEE Electron Device Lett., vol. 11, pp. 100–102, 1990. [32] M. Werner et al., “The effect of metallization on the ohmic contact resitivity to heavily B-doped poly-crystalline diamond films,” IEEE Trans. Electron Device, vol. 42, no. 7, pp. 1344–1351, 1995. [33] S. Sahli, “Electronic Characterization and Fabrication of CVD Diamond Piezoresistive Pressure Sensors,” Ph.D. dissertation, Michigan State University, East Lansing, 1997. [34] A. Bachi et al., “A novel metallizations scheme for diamond,” in Proc. Applications of Diamond Films and Related Materials, 3rd International Conf., Washington, DC, 1995, pp. 157–160. [35] S. J. Pearton, A. Katz, F. Ren, and J. R. Lothian, “ECR plasma etching of chemically vapor deposited diamond thin film,” Electron. Lett., vol. 28, no. 9, pp. 822–824, 1992. [36] J. Asmussen, “Electron cyclotron microwave discharge for etching and thin film deposition,” J. Vacuum Sci. Technol., vol. A7, no. 3, pp. 883–893, 1989. m [37] R. N. Chakraborty, “Post-Deposition Processing of Diamond Film using ECR Plasma,” Ph.D. dissertation, Michigan State University, East Lansing, 1995. [38] H. J. Looi, L. Y. S. Pang, A. B. Molloy, F. Jones, J. S. Foord, and R. B. Jackman, “An insight into the mechanism of surface conductivity in thin film diamond,” Diamond Rel. Mater., vol. 7, pp. 550–550, 1998. [39] X. Zhu, S. Guillaudeu, D. M. Aslam, U. Kim, B. Stark, and K. Najafi, “All diamond packaging for wireless integrated micro-systems using ultra-fast diamond growth,” in Proc. IEEE 2003 Int. Conference on MEMS, Kyoto, Japan, Jan. 2003, pp. 658–661. [40] P. D. Gigl, “The strength of polycrystalline diamond compacts,” in High Pressure Science and Technology, K. D. Timmerhaus and M. S. Barber, Eds. New York: Plenum, 1979, vol. 1, pp. 914–922. Xiangwei Zhu was born in Suichang, China, in 1974. He received the B.S. and M.S. degrees in physics from Beijing University, China, in 1996 and 1999, respectively. He received the Master’s degree in electrical engineering in August 2002. He is currently pursuing the Ph.D. degree in electrical engineering with a major in Electronic Materials and Devices from the Department of Electrical and Computer Engineering, Michigan State University, East Lansing, in August 2001. From 2001 to present, he works on research projects supported by NSF Engineering Research Center—Wireless Integrated Micro-System. His work focused on the design, fabrication, and packaging of diamond MEMS devices. His research interests include MEMS design, fabrication and packaging, diamond MEMS technology, and thin-film deposition technology. Dean M. Aslam (M’87–SM’93) received the M.S. and Ph.D. degrees from Aachen Technical University, Aachen, Germany, in physics and electrical engineering in 1979 and 1983, respectively. He was a recipient of German DAAD Fellowship during 1975–1983. Currently, he is Associate Director of NSF ERC (awarded to three Michigan universities; UM, MSU, and MTU) for wireless integrated microsystems (WIMS) and Associate Professor of Electrical and Computer Engineering at Michigan State University. Before joining MSU in 1988, he held a research associate position at Aachen Technical University during 1983–1984, and faculty positions at PAF College of Aeronautical Engineering (Pakistan) during 1984–1986 and Wayne State University during 1986–1988. His current research focuses on carbon-based micro- and nanotechnologies for WIMS. He Heads a group of researchers and became the first to report 1) piezoresistivity in polycrystalline (poly-C) and crystalline diamond in 1991 and 2) an intragrain piezoresistive gauge factor over 4000 in poly-C films in 1996. His group also demonstrated a gated poly-C field emission display for the first time in 1995. He has published over 75 papers and holds eight U.S. patents in the field. Yuxing Tang was born in Guizhou, China, in 1974. He graduated from Peking University, China, and received the Bachelor’s and Master’s degrees in physics in 1997 and 2000, respectively. He has been currently pursuing the Ph.D. degree in electrical engineering with a major in electronic materials and devices at the Michigan State University, East Lansing, since September 2001. He expects to receive the Ph.D. degree in July 2005. He is engaged in MEMS application by applying the diamond position sensor and diamond film coating to a cochlear prosthesis. His research interests include CVD diamond and carbon-nanotube techs, microfabrication techs (lithography, film deposition, pattern, and SEM, etc.) and related measurements. He is also familiar with the MEMS designs and simulations with ANSIY and COVENTERWARE, and familiar with the integrated circuits designs for MEMS application with CADENCE. ZHU et al.: FABRICATION OF ALL-DIAMOND PACKAGING PANELS FOR WIRELESS INTEGRATED MICROSYSTEMS Brian H. Stark was born in Boston, MA, in 1977. He graduated from Phillips Academy in Andover, MA, in 1995. He received the B.S. degree in electrical engineering, cum laude, from Cornell University, Ithaca, NY, in 1999 and the Master’s degree in electrical engineering in May 2002. He has been pursuing the Ph.D. degree in electrical engineering with a major in solid-state theory and a minor in circuits and microsystems from the University of Michigan, Ann Arbor, since June 1999. He expects to receive the Ph.D. degree in May 2004. During his undergraduate career, he interned at the Jet Propulsion Laboratory, Pasadena, CA, where he worked on processes related to MEMS reliability. His work there culminated with his authorship of a MEMS reliability guideline, which remains the only published book on MEMS reliability. From 1997 to present, he has also presided as the CEO of Stark Software, a small company that has created software packages for the medical community. He has published 12 conference papers and four journal papers since 1997. 405 Khalil Najafi (S’84–M’86–SM’97–F’00) was born in 1958. He received the B.S., M.S., and the Ph.D. degrees in 1980, 1981, and 1986, respectively, all in electrical engineering from the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor. From 1986 to 1988, he was employed as a Research Fellow, from 1988 to 1990 as an Assistant Research Scientist, from 1990 to 1993 as an Assistant Professor, from 1993 to 1998 as an Associate Professor, and since September 1998, as a Professor and the Director of the Solid-State Electronics Laboratory, Department of Electrical Engineering and Computer Science, University of Michigan. His research interests include: micromachining technologies, solid-state micromachined sensors, actuators, and MEMS; analog integrated circuits; implantable biomedical microsystems; hermetic micropackaging; and low-power wireless sensing/actuating systems. Dr. Najafi was awarded a National Science Foundation Young Investigator Award from 1992 to 1997, was the recipient of the Beatrice Winner Award for Editorial Excellence at the 1986 International Solid-State Circuits Conference, of the Paul Rappaport Award for coauthoring the Best Paper published in the IEEE TRANSACTIONS ON ELECTRON DEVICES, and of the Best Paper Award at ISSCC 1999. In 2001, he received the Faculty Recognition Award, and in 1994, the University of Michigan’s “Henry Russel Award” for outstanding achievement and scholarship, and was selected as the “Professor of the Year” in 1993. In 1998, he was named the Arthur F. Thurnau Professor for outstanding contributions to teaching and research, and received the College of Engineering’s Research Excellence Award. He has been active in the field of solid-state sensors and actuators for more than eighteen years, and has been involved in several conferences and workshops dealing with solid-state sensors and actuators, including the International Conference on Solid-State Sensors and Actuators, the Hilton-Head Solid-State Sensors and Actuators Workshop, and the IEEE/ASME Micro Electromechanical Systems (MEMS) Conference. He is the Editor for Solid-State Sensors for IEEE TRANSACTIONS ON ELECTRON DEVICES, an Associate Editor for IEEE JOURNAL OF SOLID-STATE CIRCUITS and the JOURNAL OF MICROELECTROMECHANICAL SYSTEMS, an Associate Editor for the Journal of Micromechanics and Microengineering, Institute of Physics Publishing, and an editor for the Journal of Sensors and Materials.