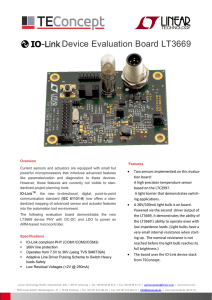

General description Functional description Package and pin

advertisement

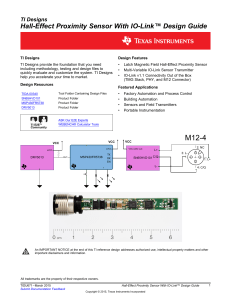

HMT7742 shortform datasheet GENIE IO-LINK DEVICE PHY Alfred-Aebi strasse 75, 2503 Biel, Switzerland Tel: +41 32 365 1181 Fax: +41 32 365 8280 www.hmt.ch ● internal data buffer for up to 15 octets ● transparent UART mode for special applications ● IO-Link clock extraction and frame generation at 38.4kBaud and 230.4kBaud. No quartz required for communication. ● outputs configured to be high-side, low-side or pushpull (<10Ω) ● fast switching time (<1μs) ● configurable short circuit current limit and reporting ● zener limits for rapid inductive load switch off ● 5V to 35V supply range ● support for unequal supplies between the microcontroller and the HMT7742 ● device reset reporting ● configurable 5V or 3.3V, 50mA linear regulator ● full zero current reverse polarity protection ● over-voltage protection to 35V ● configurable under-voltage detection ● ESD protection to 4kV ● EMC surge protection to IEC 60255-5 (2A/50µs) SS MOSI MISO SCK INT registers VPLUS short detector M-seq. control surge sigout CQ vbg PGND GND LED driver LED1 LED2 Fig. 1: Block diagram In normal operation, the device may be run either in IO-Link mode, where data is transferred with UART frames, or in SIO mode where the CQ line is driven according to the sensor state. In SIO mode the outputs can be configured to be highside, low-side or push-pull and are designed to drive capacitive, inductive and resistive loads. The output stage includes short-circuit, over temperature, surge and reverse polarisation protection. Configuration of the microcontroller is typically carried out at product delivery via the IO-Link cable. VPLUS VSNS 3) CSNS RWAKE CBLK LED1 LED2 XL CQ SS ● 7-bit, calibrated, temperature measurement ● two configurable current mode LED outputs ● Small format DFN 12LD 4mm x 3mm package Functional description At start-up power is applied via the cable on VPLUS, and the microcontroller and sensor are supplied with a 3.3V or 5V supply from the HMT7742's linear regulator. On leaving reset the microcontroller proceeds to configure the HMT7742 to the desired operating mode. MOSI MISO 1) μC thermal shutdown, configurable level allows protection of neighbouring devices and packaging CEMC 2) PGND GND SCK INT HMT7742 further SPI slaves 1) Example sensor configuration shown 2) IO-Link master is used for IO-Link mode and device configuration 3) XL (high- or low-side) in Single Input Output mode. XL has max. reactive parts CLOAD_MAX and ILOAD_MAX Fig. 2: Application diagram Package and pin-out If the microcontroller places the HMT7742 into listen mode, or a wake-up request is generated by the IO-Link master, then the HMT7742 waits for an M-Sequence on the CQ line. Once this is received, its checksum and parity are checked by the HMT7742 and an interrupt is generated on INT. The microcontroller now reads the data octets contained within the HMT7742's data buffers, and composes a return microelectronic AG 3.3V/5.0V regulator PLL IO-Link Master single octet UART mode for unlimited M-Sequence lengths. VSNS pack ● ● HMT7742 integrated UART peripheral with M-sequence handling (inc. checksum) for all IO-Link specification 1.1 MSequences unpack ● data buffer The HMT7742 GENIE IO-Link DEVICE PHY is a transceiver between a microcontroller with a sensor or actuator function and a 24V power and signalling cable, specified to support IO-Link. Features include: response in the HMT7742 via the SPI interface. The HMT7742 adds a parity and checksum and transmits the return frame on the CQ line, using a clock trimmed to the master clock. data buffer General description Alfred-Aebi Strasse 75, CH2503 Biel/Bienne, Switzerland Tel: +41 32 365 1181 web: www.hmt.ch e-mail: mailbox@hmt.ch GND SS MOSI VSNS LED2 VPLUS CQ PGND GND MISO SCK Bare die available on request INT LED1 DFN 12LD 4mm x 3mm (top view) NB: GND flag and GND pin to be connected on PCB Fig. 3: Package and pin-out HMT7742 Shortform Rev: F Page: 1/1