Centris Platform

advertisement

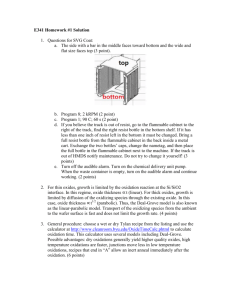

Because Innovation Matters™ Silicon Systems Group Toru Watanabe President, Applied Materials, Japan Semicon Japan November 30, 2010 SILICON SYSTEMS GROUP External Use Safe Harbor This presentation contains forward-looking statements, including those regarding the Applied Silicon Systems Group’s performance, strategic positions, products and opportunities. These statements are subject to known and unknown risks and uncertainties that could cause actual results to differ materially from those expressed or implied by such statements, including but not limited to: the level of demand for Applied’s products, which is subject to many factors, including: uncertain global economic and industry conditions, business and consumer spending, demand for electronic products and semiconductors, and customers’ utilization rates and new technology and capacity requirements; Applied’s ability to (i) develop, deliver and support a broad range of products, expand its markets and develop new markets, (ii) align its cost structure with business conditions, (iii) plan and manage its resources and production capability, (iv) implement initiatives that enhance global operations and efficiencies, (v) maintain effective internal controls and procedures, (vi) obtain and protect intellectual property rights in key technologies, and (vii) attract, motivate and retain key employees; risks related to legal proceedings and claims; and other risks described in Applied’s SEC filings. All forward-looking statements are based on management’s estimates, projections and assumptions as of November 30, 2010, and Applied undertakes no obligation to update any forward-looking statements.. SILICON SYSTEMS GROUP External Use Silicon Systems Group Overview #1 in the WFE and advanced packaging markets In 2010, expect increased market share in each SSG business In 2011, expect to grow WFE market share for the 3rd consecutive year Growth fueled by new product innovations aligned to technology inflections Source: Gartner, April 2010 3 SILICON SYSTEMS GROUP External Use Innovations Enable Inflections ADVANCED PATTERNING WAFER-LEVEL PACKAGING TRANSISTOR INTERCONNECT Centris™ Etch Tetra X™ Silvia™ Etch Eterna™ FCVD Aera3™ Avila™ CVD Avenir™ PVD/ALD Mesa™ Etch InVia™ CVD Siconi™ for Epi Centinel™ PVD UVision® 4 Brightfield Raider-S™ ECD Astra™ DSA Anneal Reflexion® GT™CMP Accelerating innovations – 15 new products in 15 months 4 SILICON SYSTEMS GROUP External Use Applied Materials Conductor Etch Innovations Ellie Yieh VP and GM, Etch Business Unit Semicon Japan November 30, 2010 SILICON SYSTEMS GROUP External Use Conductor Etch is Fastest Growing Etch Segment Conductor etch ~ $1.6B market in 2010 New steps in advanced transistors, double patterning and advanced packaging driving growth Applied already leads in advanced DRAM transistor critical etch Source: Gartner, Sept 2010 6 SILICON SYSTEMS GROUP External Use Innovations Enable Inflections ADVANCED PATTERNING WAFER-LEVEL PACKAGING TRANSISTOR INTERCONNECT Centris™ Etch Tetra X™ Silvia™ Etch Eterna™ FCVD Aera3™ Avila™ CVD Avenir™ PVD/ALD Mesa™ Etch InVia™ CVD Siconi™ for Epi Centinel™ PVD UVision® 4 Brightfield Raider-S™ ECD Astra™ DSA Anneal Reflexion® GT™CMP Accelerating innovations – 15 new products in 15 months 7 SILICON SYSTEMS GROUP External Use Applied’s Conductor Etch Competitive Position VERTICAL SCALING Leading in Advanced DRAM HORIZONTAL SCALING (BBL/BWL architectures) Expanding Positions in Double Patterning NAND, Foundry, Logic and DRAM Requires <1 % Depth Non-Uniformity 8 SILICON SYSTEMS GROUP Requires <1 nm, 3σ CD Non-Uniformity External Use Gap in Litho Roadmap is Etch Opportunity 10 Resolution (µm) 1 Above Wavelength 2 Near Wavelength Below Wavelength Hard Mask Insertion 1.5 1 DUV λ=248nm 0.6 g-line λ=436nm 0.5 0.35 i-line λ=365nm 0. 1 193 (dry) λ=193nm 0.25 0.18 1990 193 (immersion) λ=193nm 0.13 Lithography Gap 0.09 0.065 0.01 1980 Double Patterning 2000 0.045 0.032 2010 0.022 2012F Year of Production Hard masks and double patterning enable below-wavelength patterning Sources: 2010 ITRS Roadmap, Applied Materials 9 SILICON SYSTEMS GROUP External Use Adding up the CD Variation Logic / Foundry Double Patterning Scheme L1 = First litho CD variation E2 = First hard mask etch CD variation L3 + L4 = Second litho CD + overlay variation E5 = Second hard mask etch CD variation Yield impacted by CD variation: (L1 , E2 , L3 , L4 , E5) Tighter etch CD uniformity can give wider process window for litho 10 SILICON SYSTEMS GROUP External Use How Precise is the Etched Critical Dimension? Red Blood Cells Etched CD variation range of 0.8 nm: 10,000X smaller than a red blood cell diameter, matched over thousands of wafers 11 SILICON SYSTEMS GROUP External Use Patterning Etch Steps Growing +6 steps NAND 2X nm NAND 4X nm +10 steps Logic 45 nm Logic 22 nm +10 steps DRAM 2X nm DRAM 4X nm Added steps increase process cost for customers Source: Applied Materials estimate 12 SILICON SYSTEMS GROUP External Use $ / MB Relentless Cost-per-Bit Reduction F Cost reduction is key for customers Source: Gartner, Applied Materials 13 SILICON SYSTEMS GROUP External Use F Improved CD Control Applied’s Etch Leadership in Productivity and Technology Centris Platform Traditional Platform Lower Cost-Per-Wafer (normalized) 30% lower cost-per-wafer with leading critical etch performance 14 SILICON SYSTEMS GROUP External Use Applied’s Centris Platform: Performance Worth Repeating Combines industry-leading Mesa chambers with high-productivity Centris platform 15 SILICON SYSTEMS GROUP External Use Building a Productivity Powerhouse with Centris 6 Mesa Chambers DualBlade Robot En-Route Abatement FourFOUP Interface Optimized Gas Panel SILICON SYSTEMS GROUP External Use Seijo™ En-Route Abatement Doubles the Number of Etch Chambers Centris Platform Traditional Platform 3 Etch Chambers 6 Etch Chambers Abatement Chamber 4 process chambers total SILICON SYSTEMS GROUP 2 Seijo Abatement Chambers 8 process chambers total External Use AdvantEdge Mesa Chamber: Angstrom-level Precise Etch Mesa Source Extending Silicon Etch Memory leadership 1st ultra-flat uniformity ICP* etcher enabling ≤3xnm node <1nm CD Uniformity <1% Etch Depth Uniformity Rapid adoption with >200 chambers in 9 months Pulsync™ Source * Inductively Coupled Plasma Pulse Pulse Bias Advanced plasma control Microloading benefit 18 SILICON SYSTEMS GROUP External Use Mesa Source: Breakthrough Etch Rate Uniformity Traditional Limited Electrical Field Tunability Mesa Electrical Field Decoupled and Tunable Limited Uniformity Improved Uniformity Breakthrough Mesa source delivers ultra-flat etch rate map 19 SILICON SYSTEMS GROUP External Use Mesa Pulsync Mitigates Microloading Challenge: Bi-Modal Trench Depth Distribution with Spacer Double Patterning SEVERE LOADING – No Pulsing MINIMAL LOADING – With Pulsync Mesa’s Pulsync technology minimizes micro-loading in etch depth SEM image used with customer permission 20 SILICON SYSTEMS GROUP External Use Centris Enables the Same CD Every Time 6 Mesa Chambers, AutoCalibrated to Same Standard Central Reference Standards AutoCalibration Management Software E3™ software identifies excursions SILICON SYSTEMS GROUP External Use Improved Process Parameter Repeatability via Auto-Calibration OLD CONTROL LIMIT NEW CONTROL LIMIT Base Pressure Autocalibration off SILICON SYSTEMS GROUP 22 Patent Applied For Time (days) Autocalibration on External Use Ch A Ch B Ch C Ch D Ch E Ch F Centris Etch Matching of 4,000 Wafers Post-Process CD (nm) 43.0 42.0 Upper Spec Limit 41.0 40.0 Lower Spec Limit 39.0 38.0 0 250 500 750 1000 Number of wafers Chamber matching demonstrated at 0.8nm range across 4,000 wafers 23 SILICON SYSTEMS GROUP External Use Device Yield Benefit from Tighter Controls Centris Platform Device Yield Device Yield PRODUCT PERFORMANCE PROCESS PERFORMANCE Traditional Platform 24 SILICON SYSTEMS GROUP External Use Capital Productivity Benefit for Customers NAND 2Xnm at 250K WSPM, One Etch Application 3 ETCH, 1 ABATEMENT PLATFORM 6 ETCH, 2 EN-ROUTE ABATEMENT PLATFORM Unique 8-chamber architecture enables best-in-class productivity SILICON SYSTEMS GROUP External Use “Green” Benefits of Lower Facilitization Costs ~35% improvement in energy savings from standard etchers One Platform saves an Olympicsize swimming pool of water per year Lower CO2 emissions per Platform: equivalent to taking 50 cars per year off the road Green benefits contribute one-third of cost-per-wafer savings Assumes SEMI S23 standard calculations 26 SILICON SYSTEMS GROUP External Use Applied’s Conductor Etch Platforms are Well Positioned at Leading Customers AdvantEdge Chamber >1500 chambers 27 SILICON SYSTEMS GROUP AdvantEdge Mesa Chamber Centris Platform >200 chambers in first 9 months 5 customers; includes entry into 2 new customers External Use Applied’s Centris Platform: Performance Worth Repeating Precise Intelligent Productive Auto-calibrating Industry-leading at 30% lower cost-per-wafer Tightest CD uniformity Tightest depth uniformity on each wafer 28 SILICON SYSTEMS GROUP External Use SILICON SYSTEMS GROUP External Use