Lecture 9 - ECE Users Pages

advertisement

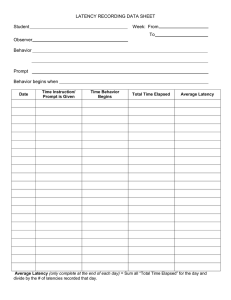

EE/CS 6760 Parallel Computer Architecture Lecture 9 Pipeline Scheduling & Synchronous vs Asynchronous • Pipelines may be clocked synchronously, or data passed asynchronously A A R R CLK EE/CS 6760 Lecture 9–2 Pipeline Speedup & Efficiency • Pipeline cycle τ is the maximum stage delay plus the latch overhead • A pipeline k stage pipline can process n tasks in T k = ( k + n – 1 )τ cycles • EE/CS 6760 T1 nkτ S k = ------ = --------------------------------Tk kτ + ( n – 1 )τ Lecture 9–3 Nonlinear Pipelines • Pipeline stages may be reused over time X S1 EE/CS 6760 S2 S3 Lecture 9–4 Reservation Tables • A reservation table describes the usage of the pipeline resources over time, for example: 1 S1 S2 S3 2 3 4 5 X 6 7 X X 8 X X X X X • Each X indicates that stage Si is busy at time t EE/CS 6760 Lecture 9–5 Collision Free Schedules • Issue latency is the number of cycles between successive executions. • A forbidden latency causes a collision between operations. • A latency cycle is a possibly repeating sequence of issue latencies. • Average latency is the average over the latencies in a latency cycle. • Maximum forbidden latency m ≤ n – 1 , for reservation table with n columns. EE/CS 6760 Lecture 9–6 Collision Vector • A collision vector defines the permissible and forbiden latencies • C = ( C m …C 1 ) where C i is a one if latency i causes a collision and zero otherwise 1 S1 S2 S3 2 3 4 5 X 6 7 X X 8 X X X X X • C X = ( 1011010 ) • Derived from distance between Xs EE/CS 6760 Lecture 9–7 State Diagram • The initial state is identical to the collision vector • A a permissible latency p is identified by shifting the initial state right p times until a zero is shifted out • The next state is constructed by ORing this shifted version of the previous state with C EE/CS 6760 Lecture 9–8 State Diagram 8+ 1011010 3 6 1011011 3 6 EE/CS 6760 1 8+ 1111111 Lecture 9–9 Minimum Average Latency • A simple cycle has each state appear only once • A greedy cycle contains the minimum permissible latency on each edge EE/CS 6760 Lecture 9–10