REVISION HISTORY REV ENG DESCRIPTION DATE ADDRESS

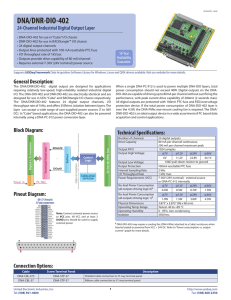

advertisement

5 4 3 2 1 REVISION HISTORY NOTES - UNLESS OTHERWISE NOTED: 1. RESISTANCE VALUES ARE IN OHMS 2. CAPACITANCE VALUES ARE IN MICROFARADS (uF) 3. ALL 0.1uF and 0.01uF CAPACITORS ARE FOR DECOUPLING PURPOSES AND SHOULD BE PLACED CLOSE TO THE IC THEY ARE SHOWN NEAR ON THE SCHEMATIC. REV 1 DESCRIPTION DATE ORIGINAL SCHEMATIC - BASED ON EQCOLOGIC REFERENCE DESIGN. ENG 05-19-14 D D VDD_3V3 DGND C PAGE PAGE PAGE PAGE PAGE PAGE PAGE PAGE VDD_5V0 AGND 1 2 3 4 5 6 7 8 - Title Page - Index- Revisions Block Diagram HSMC IO Connectivity Power Supply Circuitry CXP-6 Channel 0 CXP-6 Channel 1 CXP-6 Channel 2 CXP-6 Channel 3 C B B I2C ADDRESS TABLE BUS0 REF DEVICE ADDRESS U8 ADS1015 0X48 U9 ADS1015 0X49 I2C ADDRESS TABLE BUS1 REF DEVICE ADDRESS <Core Design> D3 Engineering 1057 E Henrietta Rd Rochester, NY 14623 p. (585) 429-1550 f. (585) 429-1551 www.d3engineering.com A A CoaXPress HSMC Interface Title Page www.D3Engineering.com 4 3 2 CAGE CODE B SCALE Monday, May 19, 2014 5 SIZE 1:1 DWN BY: REV DWG NO <Doc> 3V6D5 MRL APRVD BY: WKM 1 SHEET 1 1 OF <Page Count> 5 4 3 2 1 D D C C B B <Core Design> D3 Engineering 1057 E Henrietta Rd Rochester, NY 14623 p. (585) 429-1550 f. (585) 429-1551 www.d3engineering.com A A CoaXPress HSMC Interface Block Diagram www.D3Engineering.com 4 3 2 CAGE CODE B SCALE Monday, May 19, 2014 5 SIZE 1:1 DWN BY: REV DWG NO <Doc> 3V6D5 MRL APRVD BY: WKM 1 SHEET 2 1 OF <Page Count> 5 4 3 VCC_3V3 CXP-HSMC I/O Interface Connects the CXP-HSMC to the host board (e.g. FPGA). D VCC_3V3 PoCXP Current Sense ADC Used to control EQCx_PoCXP_CTRL signals, to enable and disable power. f_SCL <= 3.4MHz C31 0.1uF 25V 20% U8 [5] EQCO0_PoCXP_SENSE EQCO1_PoCXP_SENSE EQCO2_PoCXP_SENSE EQCO3_PoCXP_SENSE 4 5 6 7 AIN0 VDD AIN1 ADDR ALERT/RDY SDA SCL AIN2 AIN3 GND 8 1 2 9 10 R21 10K_1% 1% 1/16W 3 I2C Address = 0x48 ADS1015 DGND C TP15 TEST-POINT 1 TP16 TEST-POINT 1 Note: The pull-up resistors are implemented on this board, therefore, they should not be implemented on the Host board. PoCXP Power On Current Sense ADC C30 0.1uF 25V 20% [5] EQCO0_PSeq_SENSE B EQCO1_PSeq_SENSE EQCO2_PSeq_SENSE EQCO3_PSeq_SENSE 4 5 6 7 AIN0 VDD AIN1 ADDR ALERT/RDY SDA SCL AIN2 AIN3 GND ADS1015 8 1 2 9 10 3 R34 10K_1% 1% 1/16W 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 101 103 105 107 109 111 113 115 117 119 121 123 125 127 129 131 133 135 137 139 141 143 145 147 149 151 153 155 157 159 VCC_3V3 Used in detecting the power on sequence current (using a voltage divider) and a known current input. U9 J3 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 [5] EQCO0_ULINK R22 EQCO2_ULINK 10K_1% 1% [5] EQCO0_PoCXP_CTRL 1/16W EQCO2_PoCXP_CTRL R35 10K_1% 1% 1/16W I2C Address = 0x49 DGND 161 163 165 167 169 171 A 2 VCC_12V0 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80 82 84 86 88 90 92 94 96 98 100 101 103 105 107 109 111 113 115 117 119 121 123 125 127 129 131 133 135 137 139 141 143 145 147 149 151 153 155 157 159 102 104 106 108 110 112 114 116 118 120 122 124 126 128 130 132 134 136 138 140 142 144 146 148 150 152 154 156 158 160 DGND1 DGND3 DGND5 DGND7 DGND9 DGND11 1 DGND2 DGND4 DGND6 DGND8 DGND10 DGND12 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 Unused XCVR_RXnp/n pins connected to DGND, as per the HSMC specification (Pins 2, 4, 6, 8, 10, 12, 14, & 16). D XCVR_RXp3 XCVR_RXn3 XCVR_RXp2 XCVR_RXn2 XCVR_RXp1 XCVR_RXn1 XCVR_RXp0 [5] XCVR_RXn0 [5] 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80 82 84 86 88 90 92 94 96 98 100 EQCO1_ULINK EQCO3_ULINK EQCO1_PoCXP_CTRL EQCO3_PoCXP_CTRL C 102 104 106 108 110 112 114 116 118 120 122 124 126 128 130 132 134 136 138 140 142 144 146 148 150 152 154 156 158 160 B <Core Design> 162 164 166 168 170 172 D3 Engineering 1057 E Henrietta Rd Rochester, NY 14623 p. (585) 429-1550 f. (585) 429-1551 www.d3engineering.com A CoaXPress HSMC Interface DGND ASP-122952-01 DGND HSMC IO Connectivity Note: Unused pins on the physical connector are included in this element. This also includes are three banks of the HSMC connector. 5 4 3 www.D3Engineering.com SIZE SCALE Tuesday, May 20, 2014 2 CAGE CODE B 1:1 DWN BY: REV DWG NO <Doc> 3V6D5 MRL APRVD BY: WKM 1 SHEET 3 1 OF <Page Count> 5 4 3 2 1 D D 1.2V @ 0.24A Supplies the Eqcologic chips with power (VCC). VCC_3V3 TP-LOOP-RED VCC_1V2 U5 TP8 1 1 C17 4.7uF 6.3V 10% 3 2 TP3 VIN SW 5 1 L2 2 1 TP-LOOP-RED 0.77A 2.2uH EN GND FB C18 10uF 6.3V 20% 4 LM3671-1.2 DGND C C 24V @ 1.28A Supplies the PoCXP modules with power (VCC). VCC_12V0 VCC_24V0 TP9 TP-LOOP-RED 8.5A 1 10uH L3 1 2 1 3 9 C19 10uF 50V 10% B C20 4.7uF 25V 20% 4 R14 127K_1% 1% 1/10W 5 C21 0.027uF 25V 10% 6 11 12 13 VIN SW SW SW EN FREQ FB 2 1 B540C 5A 40V U6 2 TP10 D1 1 15 16 PoCXP Indicator LED R16 187K_1% 1% 1/10W Lights up when the PoCXP is connected VCC_24V0 8 D4 C24 4.7uF 50V 10% SS SYNC COMP AGND PGND PGND PGND NC NC TP-LOOP-RED 7 10 14 R15 1/10W 4.02K_1% 1% C22 33pF 50V 5% C23 0.022uF 50V 10% C28 NP <Voltage> <Tolerance> R17 10K_1% 1% 1/10W C29 NP <Voltage> <Tolerance> R26 1/8W 25.5K_1% 1% A C YELLOW-GREEN 1mA Vf=1.9V These DNPs were added in case the capacitance (recommended by the reference design here) would not be enough. TPS55340 DGND B DGND <Core Design> D3 Engineering 1057 E Henrietta Rd Rochester, NY 14623 p. (585) 429-1550 f. (585) 429-1551 www.d3engineering.com A A CoaXPress HSMC Interface Power Supply Circuitry Note: The CXP HSMC card also utilizes 3.3V for the current sensing circuitry. This voltage level is supplied through the HSMC port. 5 4 3 www.D3Engineering.com SIZE SCALE Monday, May 19, 2014 2 CAGE CODE B 1:1 DWN BY: REV DWG NO <Doc> 3V6D5 MRL APRVD BY: WKM 1 SHEET 4 1 OF <Page Count> 5 4 3 2 1 1 PoCXP_24V C8 1uF 50V 10% 2 L1 10uH 0.9A D R6 1/16W 1K_1% 1% C7 50V 1 Channel 0 The primary CXP input channel. [3] EQCO0_ULINK R4 3.90K_1% 1% 1/10W VCC_1V2 R13 1/16W R12 1/10W C3 25V C4 25V [3] XCVR_RXn0 [3] XCVR_RXp0 U2 10K_1% 1% 1.20K_1% 1% 7 6 11 0.1uF 20% 0.1uF 20% 10 17 12 1 4 9 FB1 1000ohm 500mA VCC_1V2 RiseR AmpR VCC VCC SDOp SDIp SDOn SDIn LFI C R5 1K_1% 1% 1/16W FB2 1000ohm 500mA 2 TEST-POINT 2 1 DGND 1 DGND TP1 D 0.01uF 10% PGND GND GND GND GND 13 16 J2 2 R1 1/10W R2 1/10W 3 15.0_1% 1% 15.0_1% 1% 0.1uF 50V C2 25V 1 5 2 C1 10% 0.1uF 20% R3 1/16W 75.0_1% 1% 4 3 Amphenol 282121-75 5 DGND NC1 NC2 NC3 C16 0.01uF 50V 10% 8 14 15 C9 0.01uF 50V 10% C6 0.1uF 25V 20% C C5 0.1uF 25V 20% EQC062R20.3 DGND PoCXP Control VCC_24V0 Enables/disables the PoCXP module for this CXP-6 channel. This circuit is the physical interface that shuts the PoCXP down when U7 there is an overcurrent. VCC 4 B GND R29 1/4W VCC_3V3 D7 1 3 R31 1/10W 1.50K_1% 1% B PoCXP_24V BAS16 100V 200mA R30 27.0K_1% Gain = 27 (Vo/Vin) 1% 1/10W R36 750K_1% 1% 1/10W Maximum reverse voltage drop = 20.7V (24V - 3.3V). This happens during normal operation of the PoCXP. DGND The capacitor filters noise on the power source. EQCO0_PSeq_SENSE [3] R37 100K_1% 1% 1/10W 1 1 TP12 TEST-POINT 2 EQCO0_PoCXP_SENSE [3] C26 0.1uF 25V 20% PoCXP_24V 0.10_1% 1% Note: Make these Test Points a Kelvin connection R28 51K 1/10W 5% 1 VIN+ INA139 Q1 ZXMP4A16G TEST-POINT 1 OUT Used as a feedback input to the host to determine when to enable/disable the PoCXP module. TP14 VIN- 3 Current Sensing (Device Detection) VCC_3V3 5 TP11 TEST-POINT DGND TP13 1 <Core Design> TEST-POINT D3 Engineering 1057 E Henrietta Rd Rochester, NY 14623 p. (585) 429-1550 f. (585) 429-1551 www.d3engineering.com 3 A 1 Q2 Switches Q1. This confiiguration acts as a low(er) voltage control signal for a high(er) voltage switch. A CoaXPress HSMC Interface 2 [3] EQCO0_PoCXP_CTRL Q2 2N7002L 115mA 60V CXP-6 Channel 0 DGND Note: This design is based upon the Eqcologic reference design. The primary addition to this is the power circuitry, which features a switch circuit, and current sense circuit (Top-Left). 5 4 3 www.D3Engineering.com SIZE SCALE Tuesday, May 20, 2014 2 CAGE CODE B 1:1 DWN BY: REV DWG NO <Doc> 3V6D5 MRL APRVD BY: WKM 1 SHEET 5 1 OF <Page Count>