Methodology for Thermal Evaluation of Multichip Modules

advertisement

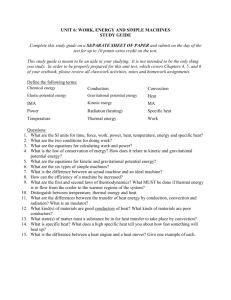

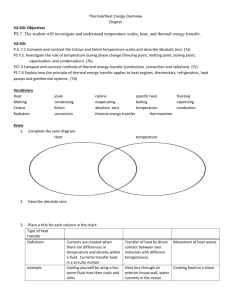

758 IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY-PART A, VOL. 18, NO. 4, DECEMBER 1995 Methodology for Thermal Evaluation of Multichip Modules Balwant S. Lall, Bruce M. Guenin, Member, IEEE, and Ronald J. Molnar, Member, IEEE Abstract-Multichip Modules provide shorter interconnection lengths between the chips, higher speeds and lower costs. This higher system performance is the driving force for advances in MCM packaging technology. A potential limitation is the ability to remove heat from these packages. With higher chip densities, the thermal management of multichip modules poses a real challenge to the package manufacturer. There is a need to define the junction-to-ambient and junction-to-case thermal resistances for multichip modules in a more rigorous manner while reducing the number of thermal tests needed to evaluate an MCM and provide information to predict junction temperatures under arbitrary powering up of the individual dice. For high reliability, it is critical that maximum specified operating junction temperatures are not exceeded. Experiments were performed for non-uniform powering up of an MCM mounted on a vertical board in natural and forced convection. The package tested was a 208-lead Amkor PMCM®. The average chip temperature due to multiple sources within the module was considered as the reference temperature for evaluating the junction temperature rise of the particular chip. The concept of superposition of temperatures was found to capture the effect of the background heating of the chip due to its neighbors as well as the individual power dissipation from the chip in question. This approach offers a more refined methodology for evaluation of non-uniformly powered multichip modules compared to previous methods. Index Terms-Microelectronic packaging, thermal performance, multichip module, superposition technique, experimental methodology, natural convection, forced convection. n Q q T NOMENCLATURE Number of chips in module. Total power dissipation for package [W]. Power dissipation from die [W]. Temperature [oC]. Greek Symbols θ Thermal resistance [oC/W] ζ Die-specific thermal resistance [oC/W] Subscripts amb Ambient avg Average Manuscript received April 19, 1995; revised September 21, 1995. This paper was presented at the 11th SEMITHERM Symposium, San Jose, CA, February 7-9, 1995. B.S. Lall is with Amkor Electronics, Inc., Advanced Products Operations, Chandler, AZ 85224 USA. IEEE Log Number 9415938. 1 PMCM is a registered trademark of Amdor Electronics, Inc. Fig. 1. Schematic of a single chip package. i j x Die location Junction Reference I. BACKGROUND I T IS a standard practice to define a lumped junction-toambient and a junction-to-case resistance for a package. For a single die package, it is fairly simple to define a θjx based on the reference temperature and the power dissipation from the package as shown by Harper [1]. Figure 1 shows a schematic of a single chip package mounted on a board and exposed to ambient air. Measurements of the current and voltage drop across the heater in the thermal die provide the power input into the die. By energy balance , this is equal to the power dissipation from the package. θjx = (Tj - Tref ) / q (1) where, q is the power dissipation from the die, Tj is the junction temperature and Tref is the reference temperature. The reference temperature could be the ambient temperature or the case temperature for the measurement of θja and θjc, respectively. The board conduction is a significant path for heat removal from the package and has a effect on θja. The convection from the package is governed by the flow pattern over the package, which determines the convective heat transfer coefficient. For θja, therefore, the following thermal circuit shown in Fig. 1 is considered. However, for the case of MCM’s , the approach to the evaluation of θjx is not as straightforward since the MCM can distribute the same total power in many ways among the chips inside of it. There are two present approaches to the determination of package θja for the multichip module. In the general case, the chips are powered differently and this will lead to different 1070-9886/95$04.00 1995 IEEE LALL et al: METHODOLOGY FOR THERMAL EVALUATION OF MULTICHIP MODULES 759 values of junction temperatures for the chips. One approach to define the junction-to-ambient thermal resistance is to consider the average junction temperature of the four chips, Tj, avg. If one takes the power dissipation (Q) of the entire package into consideration, equation (1) is modified to provide an average junction-to-ambient thermal resistance, θja-avg. θ ja − avg = Tj , avg − Tamb Q (2) The above approach is similar to the one used for a single chip package. But for multichip modules, it can be applied if the chips are of identical geometry and power dissipation as shown by Bar-Cohen [2]. However, it cannot account for different powers to chips within the same package. Also, it cannot provide accurate results when the chips are of different geometries. Since each of the dies can be powered independently, an alternate choice for the θjx is the use of the power dissipation of that particular die as shown by Sullhan et al [3]. It is possible to define a chip-location-specific junction-to-ambient thermal resistance, θja-i, which is defined in terms of the local power dissipation at the chip location. For the chip #i, the following expression can be written for this definition of θja-i θ ja − i = Tj , i − Tamb qi (3) where Tj,i is the junction temperature of the ith chip when it is powered at qi . . Kromann [4] tested a five-chip cavity-down MCM in forced convection for the range of 1 to 5 m/s with different external heat paths. He considered (3) in the calculation of the chip-to-ambient thermal resistance. The problem with the above definition of θja is most obvious when the die in question is not powered, but the neighboring dies are powered. The neighboring dies will heat up the die #1, but upon application of (3), the denominator is zero. The definition of θja as provided by (3) is therefore not appropriate. There are therefore two aspects that have to be considered. First, the total package power and second, the distribution of it within the package. The disadvantage of using (2) for the definition of the junction-to-ambient thermal resistance is that it cannot capture the variation of power levels within the multichip module. The drawback of (3) is that it is a function of the background power levels and is not valid for the unheated dies. Thus, there is great anomaly regarding the application of the correct formulation for the multichip module’s θja. A potential approach to eliminate this anomaly is the concept of adiabatic temperature. The adiabatic temperature of an electronic component on a board is the equilibration temperature achieved in the absence of self-heating. It therefore takes into account the background heating of the package due to surrounding components, or in the case of MCMs, neighboring chips. To assimilate the effects of the background heating, the concept of adiabatic temperature is applied here. It has been found to be a useful reference temperature for correcting substrate conduction due to the influence of neighboring components by Ortega and Kabir [5]. It was clarified as the reference temperature for defining the heat transfer coefficient in convective cooling of electronic Fig. 2. Thermal resistance network for the PMCM. equipment by Ortega and Lall [6]. The concept of adiabatic temperature was introduced into the lexicon of electronics packaging by Arvizu and Moffat [7] for forced flows, and Ortega and Moffat [8] for buoyancy induced flows. The adiabatic temperature approach does not work effectively in the case of natural convection when the die in question is the one that is dissipating a majority of the heat from the package. Aghazadeh et al [9] used a superposition principle to obtain thermal resistance for a two-chip 68-lead ceramic pin grid array (CPGA) and two-chip ceramic leaded chip carrier (CLCC). It was found that the junction-to-ambient thermal resistance is calculated using the total module power for natural convection and is independent of power for forced convection. No procedure was indicated for total die power levels other than those actually tested. More tests are required (n2) with this technique to determine junction temperatures in natural convection than the technique proposed here (n+3). II. THE MODEL The PMCM consists of four chips mounted within it. As shown by the thermal network for such a multichip module in Fig. 2, the dies, numbered 1 thru 4, can each be powered to a power, qi . The thermal resistances are shown in the figure to connect the various nodes in the thermal network. The conduction thermal resistance between two dies, numbered k and l is represented by θkj . Each of the dies (i) is connected to the environment through a convective thermal resistance, θja-i. The approach presented in this paper defines an average die temperature based on the overall heat flow from the entire package. Based on how much the individual chip power differs from the package-averaged power, the junction temperature for each chip is calculated by weighting this difference in power with a package-specific parameter that controls the interaction between the chips. The superposition of temperatures takes into account the background heating of the chip due to its neighbors. The chip power factor, ζi, for the ith chip is defined in terms of chip temperature rise above the average die temperature upon 760 IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY-PART A, VOL. 18, NO. 4, DECEMBER 1995 Fig. 3. Schematic of the plastic multi-chip module. powering it up by (4): ζ= Tj ,i − Tj − avg Q , where qi ≠ Q n qi − n (4) where Tj,i is the junction temperature of die i when the power qi ,o is applied to it. Tj-avg is the average die temperature for n dies within the package and Q is the total power dissipation form the package. The results in the following section will help clarify the validity of superposition for PMCMs. Experiments were performed to obtain a set of values of θja-avg and ζi for the PMCM® package. The junction temperatures were predicted using these values of the θja-avg and ζi and the applied power levels and compared to experimentally measured ones. The formalism proposed for calculating the junction temperatures of #1 die in an n-chip MCM is as follows Tj , i = θja − avg (Q) + ζi ( qi − Q ) + Tamb n (5) where qi is the power for die i and Q comprises the total power dissipation from the entire package for the n dice in the package. The present approach is motivated to reduce the number of tests needed to characterize the multi-chip module. For a multichip module with n chips, the number of tests necessary to produce a general results for arbitrary powering up of the dies is (n+3), where 3 tests are needed to test the die so that they have the same power dissipation per unit die area. The three power levels will provide a graph of θja-avg as a function of total power, Q. Thereafter, only n experiments need to be done with different power levels for the n die to arrive at the chip power factor, ζi , for each one. The package is powered to the same power level in each case but with the dies powered differently. From the resulting data, the value of ζi can be derived using equation [4]. Now, this value of ζi can be applied to any arbitrary heating conditions in the MCM to obtain the junction temperatures at each die, using equation [5]. Therefore, the total number of experiments to evaluate an MCM package containing n dice is (n+3). 1 4 2 3 Fig. 4. Location of thermal dies within the package. III. EXPERIMENTAL PROCEDURE Experiments were performed on a 208 lead MQFP PMCM package soldered to a board. A schematic of the PMCM construction used in this evaluation is shown in Fig. 3. There are four chips mounted cavity-down on a high density multilayer board. Bond wires are used to connect the chips to the multilayer board and the board to the copper leadframe. A low stress mold compound is used to package the multichip module. The enclosure for natural convection measures 12” on a side in conformance with the SEMI-spec. For forced convection, experiments were performed in a closed-loop recirculating low speed, laminar flow wind tunnel with variable free-stream temperature. The test section in the wind tunnel is 12” square in cross section with a 24” length. Air speed is continuously variable upto 1200 lfpm, with less than 1% variation from the mean, free-stream velocity. A schematic of the package is shown in Fig. 4. Delco PST-5 thermal test dice measuring 7.77 mm square are located at the sites 1 through 4. Each die has a series diode that was used for the determination of the junction temperatures by measuring the forward voltage produced by a 1 mA current. The four thermal dice can be powered up independently. The package was soldered to a single-layer circuit board, having traces of 1 oz. copper covering 20% of the board surface for a distance of 2.5 cm beyond the package periphery. Air temperature was measured from a thermocouple in the enclosure. The board is mounted in the vertical orientation for both natural convection and forced convection measurements. The experimental procedure was automated using a Hewlett-Packard data acquisition system. The dies can be powered up in a variety of patterns. Fig. 5 shows the various cases that were evaluated in this study. Case Fig. 5 Schematic of different possibilities of powering up of thermal dies in the PMCM. LALL et al: METHODOLOGY FOR THERMAL EVALUATION OF MULTICHIP MODULES 761 Case (a) Case (b) AVG THETA_ja (degC/W) 28 Case (c) Case (d) Case (e) Fig. 5. Schematic of different possibilities of powering up of thermal dies in the PMCM. TABLE I RANGE OF EXPERIMENTS PERFORMED IN NATURAL CONVECTION Die #1 POWER 1W 2W 3W Experimental Matrix BACKGROUND POWER 0W n n n 1W n n n 2W n n n 3W n n n 26 24 22 20 0 1 2 3 4 5 6 7 TOTAL POWER, Q (Watts) Fig. 6. Dependence of θja-avg on Total Power Q. powered up to arrive at (6). The average junction-to-ambient thermal resistance θja-avg is found to follow the following relation: 4W n (a) represents the powering up of a single die in the package. Two dice can be powered in two possible manners - case (b) when adjacent dice are powered up, and case (c) when diagonally opposite dice are powered up. Case (d) occurs when all dice, except one are powered up. All four dice are powered up in case (e). A series of tests were performed in which the power to each die was independently varied. The test die was die #1 and the background power level refers to the sum of power dissipation from the other dice within the MCM. For natural convection, the following array of experiments as shown in Table I was performed to study the significance of powering up of the MCM : For forced convection, a few variations of the power were studied to verify the application of the superposition theory. A constraint on the powering up of the dice was that the maximum power from the package was restricted to 6 W total. This was to prevent excessive heating of the package and permanent damage to the die. The system was allowed to reach a steady-state after each change of power. IV. RESULTS AND DISCUSSION Experiments were done for both natural convection and forced convection. A. Natural Convection Figure 6 shows the average junction-to-ambient thermal resistance as provided by (2) for the entire package as a function of the total power dissipation, Q. As is evident, a higher total power Q leads to a lower θja-avg since the higher surface temperatures produce a higher convective and radiative heat transfer coefficient. This trend was observed for all background power levels. Three tests were performed with all four die θja-avg = 25.4 (Q)-0.084 (6) Then, tests were performed with only one die powered up to determine the value of ζ I for that die by applying equation [4]. The value of ζi is fairly uniform at 22.9 oC/W for all power levels for the symmetric dies in the package under investigation. The parameter is weakly dependent on the background power level, being lower for higher background power levels. This will manifest as a lower junction temperature rise for the chip at higher background power levels. The observed variation in the value of ζi , was within 2% of the mean value for different powering levels and cases (a)-(e). The total number of tests performed to determine the values of θja-avg and ζ i,i=1…4 is seven. The model is now used to compare the predicted values to the measured values of junction temperatures for cases (a) through (e). In Fig. 7 through 11, the symbols represent the measured value and the lines represent the predicted values respectively. Fig. 7 depicts the powering up of a solitary die at different power levels as in case (a). Equation (5) was used to predict the temperatures at die #1. The model uses only one die powered up at 1, 2 and 3 watts and the rest unpowered. This yields the temperatures of the unpowered dies to be equal. In the actual physical situation, the adjacent dies have a higher temperature than the diagonal die due to conduction in the board within the package. Despite this phenomenon, the model results are found to be in good agreement with the measured data. For adjacent dice powered up, case (b), Figure 8 shows the comparison of predicted and measured values for different power levels. Die #2 is powered at 1 Watt while die #1 is powered at 1, 2 and 3 Watts. When both dies 1 and 2 are powered equally, there is negligible error between the two values of temperature. At higher power levels, the conduction effects become more significant producing lesser agreement between the predicted and measured temperature at the die that is located diagonally across from the hottest die. Case (c) of diagonally opposite dice powered up is shown in Figure 9. The results are shown for the dice powered up to the same level. The thermal symmetry of the package under conditions of natural convection is evident from these results. 762 IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY-PART A, VOL. 18, NO. 4, DECEMBER 1995 240 q1=q3=1W 160 q1=q3=2 W Die Temperature (degC) 200 Die Temperature (degC) 1W 120 2W 3W 80 40 q1=q3=3 W 160 120 80 40 0 0 1 1 2 3 2 4 Die Location Fig. 7. Experimental (symbols) vs. Predicted (lines) Junction Temperature at die location 1 through 4 for case (a) - only die 1 powered up. 3 4 Die Location Fig. 9. Experimental (symbols) versus predicted (lines) junction temperature rise above ambient at die location 1 through 4 for case (c) - diagonal dice 1 and 3 powered up. 200 160 q1=q2=q3=1W q1=q2=q3=2 W Die Temperature (degC) Die Temperature (degC) q1=1W, q2=1W 120 q1=2W, q2=1W q1=3W, q2=1W 80 40 0 1 2 3 4 Die Location Fig. 8. Experimental (symbols) versus predicted (lines) junction temperature rise above ambient at die location 1 through 4 for case (b))-adjacent dice 1 and 2 powered up. Figure 10 shows the case (d) with three dice powered up. First the dice were powered equally at 1 W and then at 2 W each. Then a general power distribution in which the dice are powered at 1, 2, and 3 Watts respectively is considered. An important observation is that the temperature of the unpowered die remains constant while the power of the other three dies is held constant at 6 W. This reinforces the concept of superposition of temperatures for MCMs, irrespective of the power distribution among the other dice. Figure 11 depicts case (e) with all four dice powered up. The power of die #2-4 is maintained at 1 W each and the power to die #1 is varied from 1 to 3 W. The model predicts the die temperatures closely for all power levels except when the die #1 is powered at 3 W where it leads to a conservative estimation of the junction temperature, which is useful. A quantitative calculation of the error between the model and measured values normalized on the measured value for cases (a)-(e) is shown in Table II where Pi represents power in Watts and Ei is the percentage error between predicted and actual values for die i. Table II shows the error between the predicted and observed junction temperatures for the above heating conditions normalized with the temperature rise above ambient and expressed as a percentage. The error is found to be negligible at fairly non-uniform powers and increases for greater discrepancies in power levels. This can be explained by the coupling of interchip conduction resistances, which have not been rigorously 160 q1=3W, q2=2W, q3=1W 120 80 40 1 2 3 4 Die Location Fig. 10. Experimental (symbol) versus predicted (lines) junction temperature rise above ambient at die location 1 through 4 for case (d) - three dice powered up. included in this model. From the results for case (e) when all four dies are poered up, the normalized error decreases for increasing chip power q1 and for the same chip power, it increases with increasing background power. The simple equation derived from the model, viz. Eqn. 5, can predict the junction temperatures to within a few percent error for natural convection applications that would have a differently powered die layout for a package similar in construction. The superposition technique is hence verified to be applicable to natural convection environment. Subsequently, the superposition approach is tested for forced convection. B. Forced Convection The experiments were repeated under forced convection conditions in the wind tunnel at air speeds of 400 and 1000 lfpm. The value of θja-avg drops by 30% at 1 Watt and 27% at 2 Watt dissipation from the package for 400 lfpm. Upon LALL et al: METHODOLOGY FOR THERMAL EVALUATION OF MULTICHIP MODULES 763 TABLE II 30 PERCENTAGE ERROR BETWEEN PREDICTED AND EXPERIMENTAL JUNCTION TEMPERATURES FOR CASES (a)-(e) P2 P3 P4 E1 E2 E3 E4 1 1 1 1 2 2 2 3 1 2 3 3 2 2 1 2 2 2 2 3 3 3 3 2 2 3 3 3 3 3 3 0 1 0 0 0 1 0 0 1 0 1 0 1 1 1 1 2 2 1 1 1 2 0 1 2 1 2 2 1 3 0 0 0 1 0 0 0 1 0 1 2 0 1 1 0 1 1 1 0 2 1 0 0 2 2 2 1 1 0 2 0 3 0 0 0 1 0 0 0 0 0 0 0 0 0 1 1 1 0 1 0 0 1 0 0 1 0 1 0 1 0 0 0 -3.2 -3.0 2.1 -2.6 -4.0 -1.6 -0.9 -3.6 0.2 -1.2 -1.1 -0.2 -0.4 -2.5 -0.2 -0.4 -0.7 -2.4 0.3 -0.2 -2.3 -1.7 0.1 0.1 -0.2 0.0 0.1 -0.7 1.0 -0.2 2.5 1.7 -1.7 3.6 3.4 -2.7 -1.0 -0.4 -4.0 -0.1 -2.4 -0.9 0.4 -0.5 -0.8 0.9 0.3 -1.1 -0.8 -0.8 -0.6 -1.0 -1.8 -0.9 -0.2 -1.6 0.5 -0.7 -0.0 -0.4 -0.1 1.8 8.1 3.0 1.9 3.4 3.9 4.1 2.0 2.9 0.5 -1.4 5.0 3.9 1.7 1.1 -0.1 1.5 0.9 1.0 -0.3 2.7 2.1 2.8 0.8 -0.0 -0.3 2.8 2.9 3.8 1.5 4.5 2.1 0.1 2.4 3.0 -2.1 -3.8 0.9 -1.2 -4.9 2.7 -2.5 0.3 -0.6 1.3 -1.7 0.4 -0.1 1.4 -0.1 0.4 0.4 -2.0 0.7 -1.2 -0.2 1.2 0.0 2.3 1.1 1.6 4.2 1.4 AVG THETA_ja (degC/W) P1 1 Watt 2 Watt 25 20 15 10 0 200 400 600 800 1000 AIR SPEED (LFPM) Fig. 12. Variation of θja-avg with air speed for test package. Table III COMPARISON OF EXPERIMENTAL AND PREDICTED VALUES OF JUNCTION TEMPERATURE RISE (IN OC) ABOVE AMBIENT FOR FORCED CONVECTION AT 400 AND 1000 LFPM. 400 LFPM 200 Die Power (W) P1 P2 P3 P4 Die Temperature (degC) q1=q2=q3=q4=1W q1=2W,q2=q3=q4=1W 1 0 1 1 1 q1=3W, q2=q3=q4=1W 160 0 0 1 0 0 0 0 0 1 0 0 1 0 0 1 Measured data Tj1 Tj2 Tj3 Tj4 37.8 13.0 48.9 47.1 47.7 13.0 11.3 48.4 23.0 22.0 11.9 12.7 22.6 47.2 22.5 13.4 37.3 22.9 23.6 49.2 Predicted data Tj1 Tj2 Tj3 37.7 12.5 48.0 48.0 48.0 12.5 12.5 48.0 22.8 22.8 12.5 12.5 22.8 48.0 22.8 Tj4 12.5 37.7 22.8 22.8 48.0 1000 LFPM 120 Die Power (W) P1 P2 P3 P4 80 1 2 3 4 Die Location Fig. 11. Experimental (symbol) versus predicted (lines) junction temperature rise above ambient at die location 1 through 4 for case (e) – all four dice powered up. increasing the air speed to 1000 lfpm, the θja-avg drops further to about half of its value for natural convection as shown in figure 12. The reduction in the value of θja-avg is from increased convective heat transfer coefficient for forced convection from the package and the board. The top of the package has a heat slug and this provides a very efficient path of heat dissipation from the package to the ambient air. The chip power factor ζi remained constant at 25.2 for the forced convection conditions of 400 and 1000 lfpm. Equation (5) was used to predict the junction temperatures for the forced convection conditions as well. Table 3 shows the comparison of 1 0 1 1 1 0 0 1 0 0 0 0 0 1 0 0 1 0 0 1 Measured data Tj1 Tj2 Tj3 Tj4 32.2 6.2 38.0 36.7 38.3 6.8 5.2 37.1 12.7 11.8 5.8 6.4 12.2 36.8 12.2 7.2 31.1 12.5 13.3 38.2 Predicted data Tj1 Tj2 Tj3 31.5 6.3 37.6 37.6 37.6 6.3 6.3 37.6 12.4 12.4 6.3 6.3 12.4 37.6 12.4 Tj4 6.3 31.5 12.4 12.4 37.6 predicted and measured results for a few power levels. The Tj’s are the rise in junction temperatures for the dies above ambient in oC. Good agreement is still observed between the two results. It is interesting to note that the behavior of the package is no longer symmetric. Under natural convection, when the adjacent dies are powered up, the measurements as well as the predictions of temperatures are symmetric. Under forced convection conditions, the upstream die, if heated, will produce a preheating of the air that the succeeding die is exposed to. This leads to a higher measured junction temperature - by a few degrees due to the effect of the upstream heating conditions. However, the superposition approach was still found to provide a good estimate of the forced convection temperatures. It is proposed that the superposition approach can be applied to MCM containing dice of non-equal size as well. The technique would be modified so that the die power density or power dissipation per unit die area, (qi /Ai ), is equal for all die during the measurement of θja-avg , where Ai is the surface area of the ith die. This will lead to a uniform junction temperature for 764 IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY-PART A, VOL. 18, NO. 4, DECEMBER 1995 the different sized die. Thereafter, this value of θja-avg can be used in (5) and superposition applied. For non-symmetrical die locations, the same approach can be used and the superposition principle will still be valid. V. FUTURE WORK A detailed numerical model for the multichip module is currently under development. The results of the numerical model will be compared with the experimentally observed results. Effects of non-uniform heating within the PMCM will be further investigated and a parametric study will be conducted to determine the significant governing parameters of the problem at hand. The numerical model will also provide insight into the application of superposition to MCMs with unequal die size and changes in die location. VI. CONCLUSIONS A simple approach is presented here for the analysis of the Amkor PMCM multichip module. The concept of superposition of temperatures was successfully applied to this package under natural and forced convection cooling environments. Using this simple approach, one can arrive at an accurate prediction for the junction temperature even for a multichip module with a non-uniform power distribution. Additional work is planned to determine the degree of accuracy that can be achieved in an arbitrary MCM with chips of unequal size and non-symmetrical placement. ACKNOWLEDGMENT The authors wish to thank Mr. Robert Marrs at Amkor Electronics for useful discussions and support during the course of the investigation. The authors would also like to thank Dr. Richard Cooley also at Amkor Electronics forgetting the parts built and Mr. Dan Rodkey of Delco Electronics for supplying the themal test die for the study. REFERENCES [1] C. A. Harper, Electronic Packaging and Interconnection Handbook. New York: McGraw-Hill, 1991. [2] A. Bar-Cohen. "Thermal management of air- and liquid-cooled multichip modules," in Multichip Modules—Systems Advantages, Major [ [3] R. Sullhan, T. Monaghan, A. Agarwal, B. Kozarek, and G. Kromann, “Thermal modeling and analysis of multichip modules,” in Proc. Seventh Annual IEEE Semiconductor Thermal Measurement and Management Symp., 1991. [4] G. Kromann, "Thermal management for ceramic multichip modules: Ex-penmental program," in 1992 IEEE Multi-Chtp Module Conf., MCMC-92, pp. 75-78. [5] A. Ortega and H. Kabir, “Substrate conduction mechanisms in convectively cooled simulated electronic packages,” in Proc. Seventh Annual IEEE Semiconductor Thermal Measurement and Management Symp., 1991, pp. 1-6. [6] A. Ortega and B. S. Lall, "A clarification of the adiabatic heat transfer coefficient as applied to convective cooling of electronics,” in Proc. Seventh Annual IEEE Semiconductor Thermal Measurement and Management Symp., 1992, pp 1-4. [7] D. E. Arvizu and R. J. Moffat, “The use of superposition in calculating cooling requirements for circuit board mounted electronic components," in Proc. Electronics Components Conf., 32nd, 1982, pp. 133-144. [8] A. Ortega and R.J. Moffat, “Buoyancy-induced convection in a onuniformly heated array of cubical elements on a vertical channel wall,” in Heat Transfer in Electronic Equipment-1986, ASME HTD6, pp. 123-134, ASME, New York, 1986. [9] M. Aghazadeh and P. Jain, “Thermal performance of multi-chip modules,” in Proc. Seventh Annual Int. Electronics Packaging Conf., Boston, MA, 1987, vol. 1, pp. 259-271. Balwant S. Lall was born in Allahabad, India in 1969. He received the B.Tech. degree in mechanical engineering from the Indian Institute of Technology at Kanpur, India, in 1989 and the M.S. in mechanical engineering from the University of Arizona, Tucson, in 1992. He is currently pursuing the Ph.D. at the University of Arizona. He joined Amkor Electronics in July 1994 for a period of 6 months in a full-time position as the Package Characterization Engineer to set up the thermal lest lab at the Amkor, Chandler facility and is continuing in a part-time capacity while finishing his Ph.D. Mr. Lall has authored or co-authored seven papers in the fiel of forced/natural convection cooling of packages in vertical and horizontal configurations, and his doctorate work involves a detailed understanding of the thermal issues and development of board level design rules for laptop computer applications. Bruce M. Guenin (M ’84), for a photograph and biography,see this issue. p. 756. Ronald J. Molnar (S’71-M’74), for a photograph and biography, see this issue, p. 757.