Field Effect Transistors Lesson #3 MOSFETS Sections 5.1-3

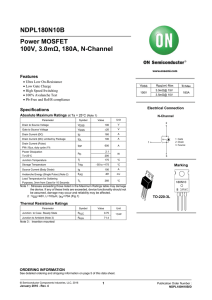

advertisement

Field Effect Transistors Lesson #3 MOSFETS Sections 5.1-3 BME 373 Electronics II – J.Schesser 3 Types of FET • Metal Oxide Semiconductor Field Effect Transistor – MOSFET – Enhancement mode – Depletion mode • Junction FETs • p channel vs n channel BME 373 Electronics II – J.Schesser 4 Metal Oxide Semiconductor Field Effect Transistor MOSFET (NMOS) Enhancement Mode • Drain which is n-doped material Source also n-doped material Base which is p-doped material G D Gate is a metal and is insulated from the Drain, Oxide Source and Base by a thin layer of silicon Metal Gate dioxide ~ .05-.1μm thick Drain • Basically, an electric current flowing from drain to source, iD, is controlled by the amount of voltage (electric field) appearing between the gate and base (note that the base and source are usually tied W + n together and therefore, it is referred to as the gate to source voltage or gate voltage), vGS. p • iD flows through a channel of n-type material which is induced by vGS. The amount of iD is a function of Substrate, body or Base the thickness of the channel and the voltage between drain and source, vDS • However, the thickness of channel is controlled by the level of gate voltage. (The width, .5 to 500 μm, and length, .2 to 10 μm, of the channel is shown in the diagram.) BME 373 Electronics II – 5 J.Schesser – – – – S Source n+ Consists of Four terminals L B Metal Oxide Semiconductor Field Effect Transistor MOSFET (NMOS) Enhancement Mode • Drain which is n-doped material Source also n-doped material Base which is p-doped material G D Gate is a metal and is insulated from the Drain, Oxide Source and Base by a thin layer of silicon Metal Gate dioxide ~ .05-.1μm thick Drain • Basically, an electric current flowing from drain to source, iD, is controlled by the amount of voltage (electric field) appearing between the gate and base (note that the base and source are usually tied W + n together and therefore, it is referred to as the gate to source voltage or gate voltage), vGS. p • iD flows through a channel of n-type material which is induced by vGS. The amount of iD is a function of Substrate, body or Base the thickness of the channel and the voltage between drain and source, vDS • However, the thickness of channel is controlled by the level of gate voltage. (The width, .5 to 500 μm, and length, .2 to 10 μm, of the channel is shown in the diagram.) BME 373 Electronics II – 6 J.Schesser – – – – S Source n+ Consists of Four terminals L B Modes of the NMOS Cutoff • vGS = 0 • pn junctions at the drain and source are reverse biased due to vDS • iD is zero D n G vGS G vGS + iD + − p B n + S − D + S − vDS − BME 373 Electronics II – J.Schesser 7 vDS Modes of the NMOS Triode Region • • • • • vGS ≥ Vto a threshold voltage which causes electrons in the base to be attracted to and holes to be repelled from the region just below the gate This process causes a n-type channel to form below the gate As vDS is increased, iD starts to flow. + v GS For small values of vDS, iD ∝ vDS − In addition, iD ∝ vGS- Vto, the excess gate voltage Therefore, the MOSFET can act as a voltage controlled resistor in the Triode Region (e.g., used in AGC circuits) BME 373 Electronics II – J.Schesser iD D n G p B n + S iD − increasing vGS vDS 8 vDS Modes of the NMOS Triode Region • • • • • vGS ≥ Vto a threshold voltage which causes electrons in the base to be attracted to and holes to be repelled from the region just below the gate This process causes a n-type channel to form below the gate As vDS is increased, iD starts to flow. + v GS For small values of vDS , iD ∝ vDS − In addition, iD ∝ vGS- Vto, the excess gate voltage Therefore, the MOSFET can act as a voltage controlled resistor in the Triode Region (e.g., used in AGC circuits) BME 373 Electronics II – J.Schesser iD D n G p B n + S iD − increasing vGS vDS 9 vDS Modes of the NMOS Triode Region (Continued) • • • • Since the drain is more positive than the source, the voltage difference between the channel and the gate varies along the channel from drain to source. As vDS is further increased, this channel voltage profile causes a tapering of the channel thickness. vGD ≠ vGS This tapering causes the resistance of the channel to increase (as vDS increases) and, + thereby, reduces the rate of increase of iD. vGS − Furthermore, it can be shown that iD D n G p B n + S − vDS iD = K [2(vGS − Vto )vDS − vDS ] 2 μC K = (W )( KP ) = (W )( n ox ) 2 L 2 L • To summarize: vGS ≥ Vto and vDS< vGS- Vto BME 373 Electronics II – J.Schesser iD increasing vGS vDS 10 Modes of the NMOS Saturation • • • As vDS continues to increase, the voltage profile continues to taper. When the gate to channel voltage at the drain, vGD, approaches Vto , the thickness of the channel at the drain is (virtually) zero. (Note that although the channel thickness is virtually zero, current flow is not cutoff since it is needed to support the channel + voltage profile.) vGS − This phenomenon limits the amount of drain current (i.e., iD is saturated) and causes iD to be independent of vDS Furthermore, it can be shown that iD = K (vGS − Vto ) 2 • Summarize: vGS ≥ Vto and vDS ≥ vGS- Vto BME 373 Electronics II – J.Schesser iD D n G p B n + S − Triode iD Saturation vDS 11 vDS Modes of the NMOS iD Triode D n iD G p Saturation vGS Cutoff + − B n + S − vDS BME 373 Electronics II – J.Schesser 12 vDS NMOS Characteristics 20 vGS = 5v iD mA 15 vGS = 4v 10 vGS = 3v 5 vGS = 2v 0 0 2 4 6 8 10 12 14 16 18 Note that Vto = 1 20 vDS Volts Note that for NMOS devices with short channel lengths, a tilt may exist due to the modulation of the channel length by the depletion region surrounding the drain. BME 373 Electronics II – J.Schesser 13 NMOS Characteristics with Channel Length Modulation due to depletion region at the drain which mostly effects shorter channel lengths 2.E-03 i 2.E-03 D amps vGS=5 v 1.E-03 1.E-03 1.E-03 vGS=4 v 8.E-04 6.E-04 4.E-04 vGS=3 v 2.E-04 vGS=2 v 0.E+00 0 2 4 6 v DS volts BME 373 Electronics II – J.Schesser 8 10 12 Note that Vto = 2 14 Load Line of a NMOS Amplifier RD 1k + M1 Mname - sin(2000πt) +- vGS = 5v VDD 20V 5 Vin iD mA 20 15 VGG + - 4V = sin( 2000πt ) + 4 vGS = 4v 5 3 vGS Gate Circuit = vin (t ) + VGG 10 4 0 vGS = 3v vGS = 2v 0 0 2 4 6 8 4 Drain Circuit 10 12 11 14 16 16 18 20 vDS Volts VDD = iD RD + vDS 20 = iD 1000 + vDS Inverted and distorted BME 373 Electronics II – J.Schesser 15 Self-Bias NMOS Circuit • This type of design allows the biasing of an amplifier using a single DC voltage source making amenable to be used in a multistaged RC coupled amplifier. To analysis this circuit, let’s replace the gate circuit with its Thevenin’s equivalent. R1 3Meg RD 4.7k R2 1Meg R2 VG = VDD = 1 20 = 5V R1 + R2 4 VDD 20V - RS 2.7k 0 R1 R2 Rg = = 3 ×1 = .75MΩ R1 + R2 3 + 1 ⇒ 0 RD 4.7k 0 RD 4.7k R1 M1 Mmodel Rg M1 Mmodel VDD 20V + - VDD 20V RS 2.7k + - VDD 20V R2 1Meg + - 0 RS 2.7k 0 0 0 0 0 BME 373 Electronics II – J.Schesser + - 3Meg .75Meg VG 5V + M1 Mmodel ⇒ • 0 16 Self-Bias NMOS Circuit (Continued) • • Now the equation for the gate loop is: VG = v + R i GS S D Assuming that the FET is to be designed in 2 the saturation region, we have: iD = K (vGS − Vto ) • Assuming KP=50μ Vto=2 V, L= 10μm, & W=400μm; then K=1mA/V2 We can solve this equation graphically or analytically: • Rg M1 Mmodel A/V2, VG = vGS + RS K (vGS − Vto ) 2 + iGS Rg SINCE NO CURRENT FLOWS IN THE GATE: VG = vGS + RS K (vGS − Vto ) 2 RD 4.7k VDD 20V + - .75Meg VG 5V RS 2.7k + - 0 0 0 KRS vGS 2 + (1 − 2 RS KVto )vGS + RS KVto 2 − VG = 0 vGS 2 + ( 1 VG − 2Vto )vGS + Vto 2 − =0 KRS RS K 1 5 − 4)vGS + 4 − =0 2.7 2.7 vGS 2 − (3.62963)vGS + 2.148148 = 0 vGS 2 + ( BME 373 Electronics II – J.Schesser 17 Self-Bias NMOS Circuit (Continued) • • • Roots are vGS=2.885051, 0.744579 Choose vGS=2.885051 since VGS > Vto=2 RD 4.7k Rg M1 Mmodel I DQ = K (vGS − Vto ) 2 = (.885051) 2 = .78332ma VDD 20V + - .75Meg VG 5V RS 2.7k + - 0 0 0 VDD = VDSQ + I DQ ( RD + RS ) VDSQ = 20 − .78332(7.4) = 14.203 BME 373 Electronics II – J.Schesser 18 Homework • NMOS Transistors – Problems: 5.3, 5.4, 5.6 • Load-line Analysis – Problems: 5.14-19 • Bias Circuits – Problems: 5.21, 5.23 BME 373 Electronics II – J.Schesser 19