Single-Phase Full-Wave Phase

advertisement

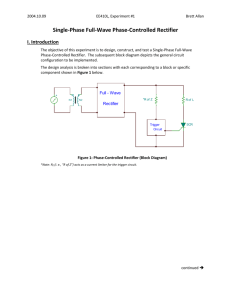

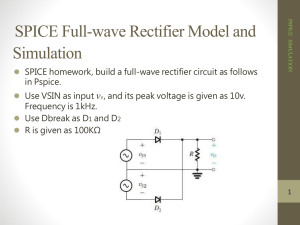

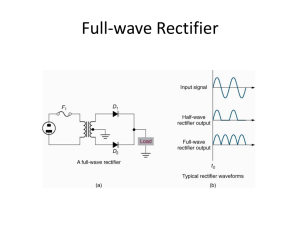

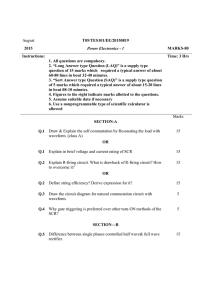

2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier I. Introduction The objective of this experiment is to design, construct, and test a Single-Phase Full-Wave Phase-Controlled Rectifier. The subsequent block diagram depicts the general circuit configuration to be implemented. The design analysis is broken into sections with each corresponding to a block or specific component shown in Figure 1 below. + Full - Wave N1 *R of Z N2 R of L Rectifier Trigger Circuit SCR Figure 1: Phase-Controlled Rectifier (Block Diagram) *Note: RZ (i. e., “R of Z”) acts as a current limiter for the trigger circuit. continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier II. Design Operational Concept A typical implementation of a phase-controlled rectifier is to provide control over the average voltage delivered to a load. The subsequent discussion describes how phase-control accomplishes this proposition. - Assume that a fully rectified sine wave is provided: - The objective is to vary the average or D.C. voltage to a load. We know - If we can vary α between 0° and 180° we can achieve substantial control over the average voltage seen by our load. α ≈ 45° α ≈ 160° After examining the foregoing graphs, it become evident that we can control the time (or phase) at which our SCR is pulsed (and subsequently conducts) during each cycle. We are controlling the D.C. voltage seen by the load. This is our primary objective. continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier II. Design (con’t) Section #1 Design Specifications: 1) Average maximum load current (IL): 2.0 Amps 2) User adjustable range angle range: α = 30° to 160° Section #2 Design Analysis: Part 1: Assuring Specified Load Current (IL) Discussion: The objective herein is to calculate a value of RL (indicated in Figure #1) that will ensure the average load current to be less than or equal to 2.0 Amps. I of L --> V of R + V of S E avg SCR Figure 2: Load Current (Simplified Block Diagram) VS = V M avg ( = 1/π ∫ = [ ] = => Eavg = ( ) = )] = [ ( [ ( )] ) Thus: Eavg = => (√ ) = (√ ) Eavg = 108.037 Volts continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier II. Design (con’t) Part 1 (cont.) Now using the equivalent circuit with Eavg By KVL Eavg = ILRL + VSCR RL = = VSCR ≈ 1.0 V ( RL = ) = 2.0 Amps – = 53.5 Ω Let: RL ≥ 54 Ω Power dissipation of RL (worst case) Pavg = (RL) = (2.0)2(54) = 216.0 Watts Part 2: Trigger Circuit Design Discussion: The objective of this section is to design a trigger circuit such that a trigger pulse will be generated to activate the SCR @ phase angles between 30° and 160°. Additionally, this range is to be user adjustable. Applicable Circuit and Calculations Figure 3: Trigger Circuit continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier II. Design (con’t) Part 2 (cont.) - We know: ( ) ⁄ ( ) Choose ( - ) Hence, we see that after one time constant (τ = RC) the voltage @ node A is 0.632 VZ. The potential @ node B constitutes a reference voltage for the P.U.T. (i. e., when the voltage @ node A is infinitesimally greater than the reference voltage @ node B, the P.U.T. conducts). Subsequently, for convenience, we will establish a reference voltage @ node B equal to 0.632 VZ. Thus: VB = 0.632 VZ VB = 0.632 * (15V) ( By V.D. : ) VB = 9.48 Volts Solving for R2: ( VB = 9.48 V Let ) ( ) ( ) = 1.164 kΩ Choose R1 = 2.0 kΩ R1 = 2.0 kΩ & R2 = 1.2 kΩ Solving for ID (Assuming P.U.T. gate current is negligible) ) = 4.69 mA Power Dissipated by Voltage Divider (worst case R1) ( ) 75.2 Watts continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier II. Design (con’t) Part 2 (cont.) Timing Analysis for R-C Charging Branch Input signal f = 60 Hz - Rectified Signal f = 120 Hz Solving for the number of milliseconds per degree of phase shift ( )( )( ) Now solve for the time required to shift 30° and 160°in phase. T|α = 30° = 0.463 msec/degree (30°) = 1.388 msec T|α = 160° = 0.463 msec/degree (160°) = 7.404 msec 1.388 msec ≤ τ ≤ 7.404 msec - The foregoing range of τ will ensure a phase shift range from 30° to 160° as long as the reference voltage is approximately 0.632VZ Solving for Radj and C: Τ = RadjC Radj|α = 30° = Choose C = 0.2 µF = ( ( ) ( ) = 6,940 Ω τ= Radj|α = 160° = = ( ( ( ) ) = 37,020 Ω τ= (Note: A 50 kΩ “pot” will be implemented) continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier II. Design (con’t) Part 3: Trigger Circuit Current Limiter (RZ) Discussion: In this section the worst case current requirements calculated in the previous sections will be used to determine the minimum current required to drive the trigger circuit. Subsequently, RZ and its power dissipation are determined. Applicable Circuit and Calculations IZ required to drive trigger circuit (worst case) IZ = IZENER + IR + ID = (25 + 2.31 + 4.69) mA = 32 mA (IZENER ≈ 25 mA to ensure Zener operates in avalanche mode.) Figure 4: Trigger Circuit Current Limiter Let IZ = 40 mA = 2,350.0 Ω Choose RZ = 2.2 kΩ Power Dissipation through RZ ( ) 3.93 Watts III. Experimental Circuit (Complete Schematic) Discussion: The subsequent circuit depicts the actual circuit (with measured component values to be employed as a single-phase full-wave phase-controlled rectifier. continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier III. Experimental Circuit (con’t) Circuit (w/ component values): Figure 5: Complete Single-Phase Full-Wave Phase Controlled Rectifier Schematic IV. Bill of Materials Component Types, Values, & Part Numbers Component Rectifier RZ VZ Radj C R1 R2 RG SCR RL P.U.T. Value --2.52 kΩ --0 50 kΩ 0.2∙10-6 F 2.09 kΩ 1.20 kΩ 50 Ω --75 Ω --- Rating Specs 200VPRV @ 2.0 A 5.0 Watts 15V / 5 Watts 1 Watt --0.5 Watts 0.5 Watts 0.5 Watts 200V/4 Amps(RMS) High Power Decade 40 V / I ± 20 mA Part No. NTE 167 --NTE 5130 A ----------NTE 5455 EE 5412 NTE 6402 continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier V. Experimental Results - Discussion: The circuit indicated in Figure #5 was established and tested as a phase-controlled rectifier. Initially, the rectifier and Zener diode were tested to insure proper operation prior to connecting the reminder of the circuit. The Zener diode was observed to clamp input signals @ 15 Volts while RZ acted as a current limier for the Zener diode. The rectifier was observed to generate a fully rectified sine wave at its output terminals. Subsequently, the load and remaining trigger circuit were connected (as shown in Figure #5) and the power scope placed across RL. Radj was adjusted between 5 kΩ and 40 kΩ and the phase angle was observed shifting between 20° and 170°. Typical Phase Shift Waveform across RL: - Finally, α was varied between 30° and 160° while monitoring IL and VL. Corresponding data tables, plots, and conclusions were generated. Part 1 Table I Half Divisions on the Scope Test Data for SCR type Phase-Controlled Rectifier Division 7.0 9.34 11.6 14.0 16.3 18.7 21.0 23.4 25.7 28.0 30.4 23.7 35.0 37.4 39.7 Phase Angle α° (degree) 30 40 50 60 70 80 90 100 110 120 130 140 150 160 170 VL Volts 104.0 99.6 91.7 80.4 72.3 63.5 55.3 49.1 35.2 25.6 17.0 10.8 6.0 3.0 0.9 IL(A)(VL/RL) 1.73 1.66 1.52 1.34 1.21 1.06 0.92 0.74 0.59 0.43 0.28 0.18 0.10 0.05 0.02 continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier V. Experimental Results (con’t) Part 2 Table II Test Data for Load Variation of SCR type Phase-Controlled Rectifier α (°) 30 RL VL IL (Ω) (V) (A) 60 104.0 1.68 <60 104.0 1.70 <60 104.0 1.72 90 60 <60 <60 55.3 0.88 55.2 0.90 55.3 0.91 160 60 <60 <60 3.0 0.05 3.0 0.05 3.0 0.05 Plot of SCR type Phase-Controlled Rectifier (Load Voltage vs. Phase Angle α) 120 100 y = 0.0016x2 - 1.1261x + 141.52 R² = 0.9918 80 60 40 20 0 0 50 100 150 200 -20 continued 2004.10.09 EE410L, Experiment #1 Brett Allan Single-Phase Full-Wave Phase-Controlled Rectifier V. Experimental Results (con’t) Plot for Load Variation of SCR type Phase-Controlled Rectifier Load Voltage VL (Volts) 120 100 80 60 40 20 0 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 Load Current IL (Amps) VI. Conclusion The objective of this experiment was to design, build, and test a Full-Wave Phase-Controlled Rectifier. Initially, we generated a design to provide triggering pulses to the SCR for phase angles between 30° and 160°. Additionally, we were careful to ensure sufficient current to drive the trigger circuit under worst-case conditions. The worst case power dissipation was determined for each element and the appropriate components were selected. Subsequently, the network indicated in Figurer #5 was constructed and tested. The test results were very favorable as the analogue phase-controlled rectifier performed flawlessly to beyond the specifications. The phase angle was controllable between 20° and 170° and the load current never exceeded 2 Amps. With regard to the experimental plots, the VL, VS and α characteristic results were just as expected. Additionally, VL remained approximately constant as IL varied at various phase angles.