Low-Power and Compact Sequential Circuits With Independent

advertisement

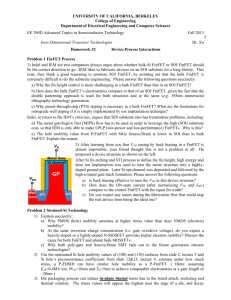

60 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 55, NO. 1, JANUARY 2008 Low-Power and Compact Sequential Circuits With Independent-Gate FinFETs Sherif A. Tawfik and Volkan Kursun, Member, IEEE Abstract—Scaling of the standard single-gate bulk MOSFETs faces great challenges in the nanometer regime due to the severe short-channel effects that cause an exponential increase in the leakage current and enhanced sensitivity to process variations. Multi-gate MOSFET technologies mitigate these limitations by providing a stronger control over a thin silicon body with multiple electrically coupled gates. Double-gate FinFET is the most attractive choice among the multi-gate transistor architectures because of the self-alignment of the two gates and the similarity of the fabrication steps to the existing standard CMOS technology. New latches and flip-flops based on independent-gate FinFETs are proposed in this paper to simultaneously reduce the power consumption and the circuit area. With the proposed independently biased double-gate FinFET sequential circuits, the active power consumption, the clock power, the leakage power, and the circuit area are reduced by up to 47%, 32%, 42%, and 20%, respectively, while maintaining similar speed and data stability as compared to the standard sequential circuits with tied-gate FinFETs in a 32-nm FinFET technology. Index Terms—Brute force, contention current, double-gate MOSFET, FinFET flip-flop, FinFET latch, Monte Carlo, multigate MOSFET. I. INTRODUCTION S CALING is the primary thrust behind the advancement of CMOS technology [1]. The channel length of a MOSFET has been scaled from 10 µm to 45 nm over the past 40 years. The increased subthreshold and gate-dielectric leakage currents and the enhanced device sensitivity to process parameter fluctuations have become the primary barriers against further CMOS technology scaling into the sub-45-nm regime. As the channel length of a conventional single-gate bulk-silicon FET is reduced, the drain potential begins to strongly influence the channel potential, thereby causing significant subthreshold leakage current (inability to turn the device off). Furthermore, as the gate dielectric thickness is reduced to assert stronger control over the channel area, the gate tunneling leakage current increases significantly [1]. Further scaling of the gate insulator thickness causes an unreasonable increase in the power consumption due to the gate leakage. The traditional scaling trends of the single-gate bulk MOSFETs are shown in Fig. 1. The multi-gate MOSFETs offer distinct advantages for simultaneously suppressing the subthreshold and gate dielectric leakage currents in the sub-45-nm CMOS technologies. Manuscript received April 23, 2007. The review of this paper was arranged by Editor J. Welser. The authors are with the Department of Electrical and Computer Engineering, University of Wisconsin—Madison, Madison, WI 53706-1691 USA (e-mail: tawfik@wisc.edu). Digital Object Identifier 10.1109/TED.2007.911039 Fig. 1. Scaling trends of the CMOS technology. The two electrically coupled gates and the thin silicon body suppress the short-channel effects in a double-gate MOSFET, thereby lowering the subthreshold leakage current [2], [10]. The suppressed short-channel effects and the enhanced gate control over the channel (lower subthreshold swing) permit the use of a thicker gate oxide in a double-gate MOSFET as compared to a conventional single-gate transistor. The gateoxide leakage current of a double-gate transistor is thereby significantly reduced. The thin body of a double-gate device is typically undoped or lightly doped. Therefore, the carrier mobility is enhanced and the device variations due to the doping fluctuations are reduced in a double-gate MOSFET as compared to a single-gate bulk transistor [10]. The threshold voltage is typically tuned by adjusting the channel doping concentration in the conventional single-gate bulk MOSFET. Alternatively, in a double-gate MOSFET technology, the threshold voltage is typically tuned by adjusting the work function of the gate material [6]. The FinFET is the most attractive choice among the doublegate device architectures due to the self-alignment of the two gates and the fabrication compatibility of the FinFETs with the existing standard CMOS fabrication process. Both tied-gate and independent-gate FinFETs have been successfully fabricated. A fabrication process is described in [5] for implementing the tied-gate and independent-gate FinFETs on the same die. In [3] and [4], the independent-gate FinFETs are utilized to reduce the number of transistors required for implementing specific logic functions as compared to the standard circuits with tied-gate FinFETs. In addition to the area savings, significant speed enhancement is reported due to the reduced parasitic capacitance and the lower transistor stack heights with the independentgate FinFET circuits as compared to the circuits with tied-gate 0018-9383/$25.00 © 2008 IEEE TAWFIK AND KURSUN: LOW-POWER AND COMPACT SEQUENTIAL CIRCUITS WITH INDEPENDENT-GATE FinFETs FinFETs. The power consumption is also reduced due to the lower parasitic capacitance of the simplified circuit topologies with the independent-gate FinFETs. Static latches and flip-flops are extensively used in synchronous integrated circuits (ICs). The main module of static latches and flip-flops is the bistable circuit formed by a cross-coupled inverter pair. Data are written to a latch either by brute force using a stronger input circuitry as compared to the feedback inverter or by temporarily breaking the feedback loop using a switch (a transmission gate or a tristate inverter) that is controlled by the clock signal. The approach based on data forcing reduces the clock load, the power consumption, and the circuit area by lowering the number of clocked transistors. Power consumed by the clock subsystem is a significant portion (e.g., reported as 40% in [8]) of the total IC power. Brute-force latches and flip-flops with reduced clock load and simpler circuitry are therefore widely used in the state-of-theart ICs [9], [11]. In this paper, new FinFET latches and flipflops that operate based on data forcing are presented. The independent-gate FinFETs are employed in the bistable element feedback path of the proposed circuits to simultaneously reduce the power consumption (both the data transfer power and the clock power) and the area as compared to the standard tied-gate FinFET sequential circuits operating with the same principle of data forcing. This paper is organized as follows. The operation of FinFETs is presented in Section II. A quantitative comparison between the FinFET and the standard single-gate MOSFET technologies is provided. A new static latch based on the independentgate FinFETs is described in Section III. The new latch is compared to a standard latch with tied-gate FinFETs at different process corners under parameter fluctuations. A new bruteforce master–slave flip-flop based on the proposed independentgate FinFET latch is described and characterized in Section IV. Finally, conclusions are provided in Section V. II. FinFET TECHNOLOGY In this section, the device architectures for the tied-gate and independent-gate FinFETs are presented. The n-type and p-type FinFET devices with a 32-nm channel length are designed and characterized using MEDICI, a physics-based device simulator [7]. An n-type FinFET is compared with a conventional single-gate bulk NMOS transistor for the short-channel effects and the drain-induced barrier lowering (DIBL). The effect of different gate-bias conditions on the I–V characteristics of the independent-gate FinFETs is provided. The 3-D architectures of the tied- and independent-gate FinFETs are shown in Fig. 2(a) and (b), respectively. A top view of a FinFET indicating the critical physical dimensions is shown in Fig. 2(c). The technology parameters of the FinFETs considered in this paper are summarized in Table I. The channel length is 32 nm. Two metals with the work functions of 4.5 eV and 4.9 eV are used as the gate materials for the n-FinFET and the p-FinFET, respectively. For these work functions, the threshold voltages are 0.23 V and −0.28 V for the tied-gate n-FinFET and the tied-gate p-FinFET, respectively, at the room temperature. 61 Fig. 2. FinFET architectures. (a) Tied-gate FinFET. (b) Independent-gate FinFET. (c) Cross-sectional top view of a 32-nm FinFET. TABLE I FinFET TECHNOLOGY PARAMETERS The threshold voltage is the gate-to-source voltage at which the drain current per fin height is 10−4 A/µm for |VDS | = VDD (VDD = 0.8 V). The variations of the threshold voltage and the DIBL with the channel length are shown in Fig. 3 for a double-gate FinFET and a single-gate bulk MOSFET. The DIBL is measured as the degradation in |Vth | when the drain voltage is increased from 0.05 to 0.8 V (VDD ). The short-channel effect (Vth rolloff) is significantly suppressed with the double-gate FinFET technology, as shown in Fig. 3(a). The dependence of the threshold voltage on the channel length is much weaker for the doublegate FinFET as compared to the single-gate bulk MOSFET. Furthermore, the DIBL observed for the double-gate FinFET is significantly smaller as compared to the single-gate MOSFET, as shown in Fig. 3(b). An independent-gate FinFET operates in the dual-gate mode (DGM) when both gates are biased to induce channel inversion. Alternatively, an independent-gate n-FinFET (p-FinFET) operates in the single-gate mode when one of the gates is deactivated by a connection to ground (VDD ). Disabling one of the gates in the single-gate mode (SGM) increases the absolute value of the threshold voltage as compared to the DGM. It is therefore possible to modulate the threshold voltage of a FinFET by independently biasing the two gates. The currents produced by 62 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 55, NO. 1, JANUARY 2008 Fig. 3. Comparison of the short-channel effect and the DIBL in the FinFET and the standard single-gate bulk MOSFET technologies. (a) Variation of the threshold voltage with the channel length. (b) DIBL comparison. DIBL is measured as the degradation in |Vth | when the drain voltage is increased from 0.05 to 0.8 V (VDD ). the n- and p-type FinFETs at 110 ◦ C are 2.55× and 2.77× higher in the DGM as compared to the SGM, as shown in Fig. 4(a) and (b), respectively. Modulation of the threshold voltage by independently biasing the two gates of a FinFET is attractive for developing low-power circuit techniques with dual threshold-voltage (dual-|Vth |) transistors. The MEDICIpredicted dc characteristics of the independent-gate n-type and p-type FinFETs are listed in Tables II and III, respectively. In this paper, new latches and flip-flops based on the independent-gate FinFET technology are proposed. The latches considered in this paper operate with brute force in the transparent mode. In order for this type of latches to function correctly, the input driver must be designed to have a significantly higher strength as compared to the feedback path. By utilizing the independent-gate FinFETs operating in the SGM, the contention between the input circuitry and the feedback path of a latch is significantly reduced with the proposed technique. New data can therefore be transferred to a transparent latch without the need for oversizing the input drivers, unlike the standard latches based on the tied-gate FinFETs. With the proposed technique, the smaller sizes of the transistors in the input circuitry lead to a reduction in the switched capacitance and the clock load, thereby reducing the total power consumption, the clock power, and the leakage power as compared to the circuits with tied-gate FinFETs. Furthermore, the area is also reduced with the proposed technique due to the smaller transistors. The FinFET sequential circuits are characterized in this paper considering the effect of the process parameter fluctuations. Monte Carlo simulations, however, are not feasible for the entire circuitry of the latches and the flip-flops due to the long simulation time of a transient analysis with MEDICI, the significant number of the device parameters subject to the Fig. 4. Drain-current characteristics of FinFETs. (a) n-FinFET. (b) p-FinFET. |VDS | = VDD = 0.8 V. T = 110 ◦ C. TABLE II DC CHARACTERISTICS OF AN n-FinFET TABLE III DC CHARACTERISTICS OF A p-FinFET TAWFIK AND KURSUN: LOW-POWER AND COMPACT SEQUENTIAL CIRCUITS WITH INDEPENDENT-GATE FinFETs 63 Fig. 6. Latch based on data forcing (brute force). Fig. 5. Monte Carlo simulation results for the n- and p-type FinFETs with 10 000 samples. SD: Standard deviation. VDD = 0.8 V. |VGS | = |VDS | = VDD . fluctuations considered in this paper, and the large number of the simulation samples. Therefore, an alternative process corner analysis is provided in this paper to characterize the sequential circuits under the parameter fluctuations. The FinFET device parameters that produce the 3σ points on the current distribution curves are used to characterize the strong and weak devices. These devices are used for a variation corner analysis to assess the impact of the process fluctuations on the FinFET sequential circuits. The effect of process variations on the FinFET on current is evaluated using the Monte Carlo analysis with Taurus-MEDICI and a PERL script. Independent 3σ variations of 10% are assumed for the channel length, the fin height, the fin thickness, and the gate-oxide thickness of a FinFET. The distributions of the on current are shown in Fig. 5 for the n-type and p-type FinFETs operating in the DGM (the two gates are tied) and the SGM (one of the gates is disabled). The mean and the standard deviation (SD) of the on current are reduced in the SGM for both the n-type and the p-type FinFETs, as shown in Fig. 5. III. FinFET LATCHES Static FinFET latches that operate with brute force in the transparent mode are presented in this section. The standard implementation of a latch with the tied-gate FinFETs is described in Section III-A. The proposed latch with the independent-gate FinFETs is described in Section III-B. The latches are characterized for power consumption, setup time, data stability, and propagation delay at different process corners under parameter variations in Section III-C. The latch considered in this section consists of a crosscoupled inverter pair, a driver inverter, and a transmission gate controlled by the clock signal, as shown in Fig. 6. The advantages of this latch are the reduced clock load and the lower transistor count as compared to a latch that can disable the feedback path whenever the latch is transparent. The data transfer to the latch shown in Fig. 6 occurs with brute force when the clock is high. To be able to transfer new data into this latch, the driver inverter (I1 ) and the transmission gate (T1 ) must be stronger as compared to the feedback inverter (I2 ). Fig. 7. Standard LATCH-TG in a 32-nm FinFET technology. (a) Circuit schematic. (b) Layout. The size of each transistor is given as (number of fins × Hfin )/L. Hfin : Fin height. L: Channel length. Layout area = 0.63 µm2 . A. Standard Tied-Gate FinFET Latch (LATCH-TG) The standard implementation of a latch in a FinFET technology with the tied-gate transistors (LATCH-TG) is shown in Fig. 7. The feedback inverter (M7 and M8 ) must be weaker than the input stage composed of the driver inverter (M1 and M2 ) and the transmission gate (M3 and M4 ) in order to be able to change the stored bit when the latch is transparent (clock signal is high). This requirement is achieved by sizing M1 , M2 , M3 , and M4 , as shown in Fig. 7. M7 and M8 both have been sized minimum (single fin) to minimize the contention with 64 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 55, NO. 1, JANUARY 2008 Fig. 9. Waveforms of LATCH-IG. stage. With such configuration, I1 (M1 and M2 ) and T1 (M3 and M4 ) can be sized minimum while still being able to overpower the feedback inverter I2 (M7 and M8 ) when the latch is transparent. Since all the gates are sized minimum, the capacitive loads at the clock, the input, and the output nodes are reduced, thereby significantly lowering the total power consumption as compared to the LATCH-TG circuit. Furthermore, the area of the LATCH-IG with smaller transistors is significantly reduced as compared to the LATCH-TG which requires larger transistors for functionality. The LATCH-IG area is 0.506 µm2 . Fig. 8. New LATCH-IG in a 32-nm FinFET technology. (a) Circuit schematic. (b) Layout. The size of each transistor is given as (number of fins × Hfin )/L. Hfin : Fin height. L: Channel length. Layout area = 0.506 µm2 . the input stage whenever the latch is transparent. Note that the width of a FinFET is quantized by the number of fins due to the constant fin height determined by the technology. The area of the LATCH-TG is 0.63 µm2 . As shown in Fig. 7, with the tied-gate FinFETs, the functionality is achieved by increasing the size of the input stage, resulting in an increased clock load, larger circuit area, and higher power consumption. B. Proposed Independent-Gate FinFET Latch (LATCH-IG) A new FinFET latch (LATCH-IG) based on the independentgate transistors is presented in this section. The LATCH-IG is shown in Fig. 8. The latch operates as follows. When the clock signal is low, the transmission gate (composed of M3 and M4 ) is turned off and the latch is opaque. The cross-coupled inverters maintain the state of the latch. When the clock signal transitions high, the transmission gate is turned on and the latch becomes transparent. The new data are transferred to the latch with brute force. The transistors in the feedback path are intentionally weakened by operation in the SGM (the back gates of M8 and M7 are connected to VDD and GND, respectively) in order to reduce the power consumption while maintaining the speed with the new latch. With the proposed technique, the driver inverter (M1 and M2 ) and the transmission gate (M3 and M4 ) produce more current as compared to the feedback inverter (M7 and M8 ) without the need for oversizing the input C. Comparison Quantitative comparison of the two FinFET latches is provided in this section. A capacitive load of 0.2 fF is assumed at the output node. The temperature is 110 ◦ C. The clock frequency is 4 GHz. The waveforms of LATCH-IG are shown in Fig. 9. The total power consumption includes the power consumed in the latch due to the switching input and output nodes as well as the power consumed by the clock driver. The clock power is measured when the clock is the only switching signal with the input and output nodes fixed at 0 V. The static power is measured when neither the clock nor the input signals are switching. The setup time for the latch is the time duration (Tdc ) between the latest input transition and the negative edge of the clock signal (the latches evaluated in this paper are positive) for which the propagation delay (TDQ ) is increased by 1% as compared to the minimum data-to-Q delay (TDQ- min ). The static noise margin (SNM) is the metric used to characterize the noise immunity of the latches. The SNM of the latches is determined graphically from the butterfly curves, as shown in Fig. 10. Weakening the feedback inverter by independent gate bias tends to reduce the hold data stability at Node1 , provided that there is noise coupling directly onto Node1 . Alternatively, provided that there is noise induced directly at the latch output, a weaker feedback inverter also tends to enhance the stability of the data on Node1 by effectively attenuating the noise transfer backward from Q to Node1 . For a worst case noise scenario with equal and opposite amounts of noise coupling to Node1 and Q, the new LATCH-IG and the standard LATCH-TG have similar SNMs, as shown in Fig. 10. TAWFIK AND KURSUN: LOW-POWER AND COMPACT SEQUENTIAL CIRCUITS WITH INDEPENDENT-GATE FinFETs 65 Fig. 11. Total active-mode power consumption of the FinFET latches. Fig. 10. Butterfly curves of the cross-coupled inverters in the LATCH-IG and the LATCH-TG at the nominal process corner. VDD = 0.8 V. TABLE IV PROCESS CORNERS UNDER PARAMETER VARIATIONS Fig. 12. Clock power of the FinFET latches. Four process corners that represent the worst and the best cases of delay are identified for each latch, as listed in Table IV. A fifth process corner (D5) is used to characterize the worst case SNM. The latches are characterized at each process corner (including the nominal process corner), as shown in Figs. 11–16 and as listed in Table V. The total power consumption, the clock power, and the leakage power are reduced by up to 47%, 22%, and 42%, respectively, with the static independentgate-biased FinFET latch while maintaining similar speed and data stability as compared to the LATCH-TG across different process corners. Furthermore, the area of the LATCH-IG is 20% smaller as compared to the LATCH-TG. For the delay and power measurements in this paper, the input signal is assumed to switch every clock cycle, as shown in Fig. 9. The clock power shown in Fig. 12 is therefore much less than the total power consumption. In a more realistic circuit environment, the input activity factor would be significantly less than unity. The power consumed by the clock drivers would therefore be a higher portion of the total power. The clockpower savings with the proposed latch would have a more Fig. 13. Leakage power (averaged for all four possible input–output combinations in the standby mode) of the FinFET latches. Clock is gated low. T = 110 ◦ C. significant impact on the total power consumption in a real chip environment. IV. FinFET FLIP-FLOPS In this section, brute-force master–slave flip-flops in FinFET technologies are presented. A standard master–slave flip-flop with the tied-gate FinFETs is described in Section IV-A. The proposed master–slave flip-flop with the independent-gate FinFETs is described in Section IV-B. The FinFET flip-flops 66 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 55, NO. 1, JANUARY 2008 TABLE V LEAKAGE POWER OF THE STANDARD LATCH-TG AND THE PROPOSED LATCH-IG AT THE NOMINAL PROCESS CORNER Fig. 14. Average propagation delay of the FinFET latches. A. Standard Tied-Gate FinFET Flip-Flop (FF-TG) The standard master–slave FF-TG is shown in Fig. 18. To be able to transfer new data into the master stage when the clock is high, I1 (M1 and M2 ) and T1 (M3 and M4 ) are sized to be stronger as compared to I2 (M7 and M8 ) with this tiedgate FinFET implementation, as shown in Fig. 18. Similarly, I3 (M5 and M6 ) and T2 (M9 and M10 ) are sized to produce more current as compared to I5 (M13 and M14 ) to be able to transfer the last sampled data from the master stage to the slave stage when the clock transitions low. These strict requirements on sizing result in larger area, higher clock load, and increased power consumption with the standard FF-TG. The potential advantages of the brute-force topology, therefore, cannot be fully exploited with the tied-gate FinFET technology. Fig. 15. Setup time of the FinFET latches. B. Proposed Independent-Gate FinFET Flip-Flop (FF-IG) Fig. 16. SNM of the FinFET latches. are characterized for power consumption, clock-to-Q delay, and setup time for different process corners under parameter variations in Section IV-C. The circuits considered in this section are the master–slave flip-flops based on the brute-force latch architecture described in Section III. The gate level schematic of the brute-force flipflop is shown in Fig. 17. To be able to transfer new data to the master stage when the clock signal is high, I1 and T1 must be significantly stronger than I2 . Similarly, to be able to change the state of the slave stage when the clock is low, I3 and T2 must be significantly stronger than I5 . The new FF-IG is presented in this section. The proposed flip-flop is shown in Fig. 19 with the sizes of the transistors indicated. The flip-flop operates as follows. When the clock is high, the master and the slave stages are in the transparent and opaque modes, respectively. The data transfer from the input (D) to Node2 occurs with brute force. Despite the minimum sizing of all the gates, the driver inverter (M1 and M2 ) and the transmission gate (M3 and M4 ) manage to produce more current as compared to the feedback inverter (M7 and M8 ) with the proposed technique. The data in the slave stage are maintained by the cross-coupled inverters (M11 −M12 and M13 −M14 ). When the clock transitions low, the master stage is disconnected from the input by the cutoff transmission gate (M3 and M4 ). The last sampled data are maintained in the master stage by the cross-coupled inverters (M5 −M6 and M7 −M8 ). The slave stage becomes transparent. The data transfer from the Node2 to the flip-flop output (Q) occurs with brute force. Similar to the master stage, the driver inverter (M5 and M6 ) and the transmission gate (M9 and M10 ) of the slave stage produce more current as compared to the feedback inverter (M13 and M14 ) despite the minimum sizing of all the gates. New data are transferred from the master stage into the slave stage with the negative edges of the clock signal. Hence, with the proposed FF-IG, the input circuitry of both the master and slave stages manages to overpower the corresponding feedback paths without the need for oversizing the transistors. TAWFIK AND KURSUN: LOW-POWER AND COMPACT SEQUENTIAL CIRCUITS WITH INDEPENDENT-GATE FinFETs 67 Fig. 17. Master–slave flip-flop based on data forcing (brute force). Fig. 18. Standard FF-TG in a 32-nm FinFET technology. (a) Circuit schematic. (b) Layout. The size of each transistor is given as (number of fins × Hfin )/L. Hfin : Fin height. L: Channel length. Layout area = 1.1 µm2 . All the gates of the proposed flip-flop are sized minimum. The feedback inverters I2 (M7 and M8 ) and I5 (M13 and M14 ) are weakened by disabling the back gates of the p-FinFETs (M8 and M14 ) and the n-FinFETs (M7 and M13 ) by a connection to VDD and GND, respectively. With the proposed independentgate FinFET circuit, the input-versus-feedback contention observed at Node1 and Node3 is thereby significantly suppressed. Furthermore, the capacitances of Node2 and Node4 are also reduced due to the permanently disabled (nonswitching) back gates of M7 , M8 , M13 , and M14 . Hence, the total power consumption, the clock power, and the circuit area of the proposed flip-flops are simultaneously reduced as compared to the standard FF-TG. C. Comparison The proposed and the standard FinFET flip-flops are characterized in this section for the setup time, the clock-to-output delay, the active power consumption (both the data transfer power and the clock power), and the static power consumption. A capacitive load of 0.4 fF is assumed at the output of the flip-flops. The temperature is 110 ◦ C. The clock frequency is 4 GHz. The waveforms of the FF-IG are shown in Fig. 20. The total power consumption includes the power consumed in the flip-flop due to the switching input and output nodes as well as the power consumed by the clock driver. The clock power is measured with the input and output nodes maintained idle (the clock is the only switching signal). The leakage power 68 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 55, NO. 1, JANUARY 2008 Fig. 19. New FF-IG in a 32-nm FinFET technology. (a) Circuit schematic. (b) Layout. The size of each transistor is given as (number of fins × Hfin )/L. Hfin : Fin height. L: Channel length. Layout area = 0.881 µm2 . Fig. 20. Waveforms of FF-IG. is measured with the input and the clock signals maintained idle. The setup time of the flip-flop is the time duration (Tdc ) between the input transition and the active clock edge (the flipflops evaluated in this paper are negative-edge-triggered) for which the data-to-output delay (TDQ ) is minimized. The flip-flops are characterized for the first four process corners listed in Table IV as well as the nominal process corner, as shown in Figs. 21–25 and as listed in Table VI. FF-IG offers up to 46%, 32%, 33%, and 22% reduction in the total activemode power consumption, the clock power, the average leakage power, and the setup time, respectively, as compared to the FF-TG across different process corners under the parameter fluctuations. Furthermore, the circuit area is reduced by 20% with the FF-IG as compared to the standard FF-TG. Fig. 21. Total active-mode power consumption of the FinFET flip-flops. V. CONCLUSION In this paper, new latches and flip-flops based on the independent-gate FinFET technology are proposed. The latches considered in this paper operate with brute force in the transparent mode. In order for this type of latches to be functional, the input drivers must be designed to have a significantly higher strength as compared to the feedback path. By utilizing independent-gate FinFETs operating in the SGM, the contention between the input circuitry and the feedback path of a latch is significantly reduced. New data can therefore be transferred to a transparent latch without the need for oversizing the input drivers unlike the standard latches based on the TAWFIK AND KURSUN: LOW-POWER AND COMPACT SEQUENTIAL CIRCUITS WITH INDEPENDENT-GATE FinFETs Fig. 22. Clock power of the FinFET flip-flops. 69 Fig. 25. Average propagation delay of the FinFET flip-flops. TABLE VI LEAKAGE POWER OF THE STANDARD FF-TG AND THE PROPOSED FF-IG AT THE NOMINAL PROCESS CORNER Fig. 23. Leakage power (averaged for four different input–output combinations in the standby mode) of the FinFET flip-flops. Clock is gated low. in this paper. With the proposed latch and flip-flop, the total active-mode power consumption, the clock power, the leakage power, and the circuit area are reduced by up to 47%, 32%, 42%, and 20%, respectively, while maintaining similar speed and data stability as compared to the circuits with tied-gate FinFETs across different process corners. R EFERENCES Fig. 24. Setup time of the FinFET flip-flops. tied-gate FinFETs. With the proposed technique, the smaller sizes of the transistors in the input circuitry lead to a reduction in the switched capacitance and the clock load, thereby reducing the power consumption as compared to the circuits with tied-gate FinFETs. Furthermore, the area is also reduced with the proposed technique due to the smaller transistors. The new sequential circuits are characterized under the process parameter variations in a 32-nm FinFET technology [1] V. Kursun and E. G. Friedman, Multi-Voltage CMOS Circuit Design. Hoboken, NJ: Wiley, 2006. 242 pp. [2] K. Kim et al., “Leakage power analysis of 25-nm double-gate CMOS devices and circuits,” IEEE Trans. Electron Devices, vol. 52, no. 5, pp. 980– 986, May 2005. [3] M.-H. Chiang et al., “High-density reduced-stack logic circuit techniques using independent-gate controlled double-gate devices,” IEEE Trans. Electron Devices, vol. 53, no. 9, pp. 2370–2377, Sep. 2006. [4] M.-H. Chiang et al., “Novel high-density low-power logic circuit techniques using DG devices,” IEEE Trans. Electron Devices, vol. 52, no. 10, pp. 2339–2342, Oct. 2005. [5] Y. Liu et al., “Cointegration of high-performance tied-gate three-terminal FinFETs and variable threshold-voltage independent-gate four-terminal FinFETs with asymmetric gate-oxide thicknesses,” IEEE Electron Device Lett., vol. 28, no. 6, pp. 517–519, Jun. 2007. [6] J. Kedzierski et al., “Metal-gate FinFET and fully-depleted SOI devices using total gate silicidation,” in IEDM Tech. Dig., Dec. 2002, pp. 247–250. [7] Medici Device Simulator, Synopsys, Inc., Mountain View, CA, Feb. 2003. [8] P. E. Gronowski et al., “High-performance microprocessor design,” IEEE J. Solid-State Circuits, vol. 33, no. 5, pp. 676–686, May 1998. [9] H. Ando et al., “A 1.3-GHz fifth-generation SPARC64 microprocessor,” IEEE J. Solid-State Circuits, vol. 38, no. 11, pp. 1896–1905, Nov. 2003. [10] S. A. Tawfik and V. Kursun, “Low-power high-performance FinFET sequential circuits,” in Proc. IEEE Int. SOC Conf., Sep. 2007, pp. 145–148. [11] S. Naffziger et al., “The implementation of the Itanium2 microprocessor,” IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1448–1460, Nov. 2002. 70 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 55, NO. 1, JANUARY 2008 Sherif A. Tawfik received the B.S. and M.S. degrees in electronics and communications engineering from Cairo University, Cairo, Egypt, in 2003 and 2005, respectively. He is currently working toward the Ph.D. degree in electrical and computer engineering in the Department of Electrical and Computer Engineering, University of Wisconsin—Madison, Madison, under the supervision of Prof. Volkan Kursun. His research interests are in the areas of low-power and variation-tolerant integrated-circuit design and emerging integrated-circuit technologies. Volkan Kursun (S’01–M’04) received the B.S. degree in electrical and electronics engineering from the Middle East Technical University, Ankara, Turkey, in 1999, and the M.S. and Ph.D. degrees in electrical and computer engineering from the University of Rochester, Rochester, NY, in 2001 and 2004, respectively. He performed research on mixed-signal thermal inkjet integrated circuits (ICs) with the Xerox Corporation, Webster, NY, in 2000. During the summers of 2001 and 2002, he was with the Intel Microprocessor Research Laboratories, Hillsboro, OR, where he was responsible for the modeling and design of high-frequency monolithic power supplies. He has been an Assistant Professor with the Department of Electrical and Computer Engineering, University of Wisconsin—Madison, Madison, since 2004. He has more than 60 publications and four issued and three pending patents in the areas of high-performance integrated-circuits and emerging semiconductor technologies. He is the Author of the book Multi-Voltage CMOS Circuit Design (Wiley, 2006). His current research interests include low-voltage, low-power, and high-performance integrated-circuit design, modeling of semiconductor devices, and emerging integrated-circuit technologies. Dr. Kursun is a member of the technical program and organizing committees of a number of IEEE and Association for Computing Machinery conferences. He serves on the editorial boards of the IEEE TRANSACTIONS ON V ERY L ARGE S CALE I NTEGRATION S YSTEMS , the IEEE T RANSACTIONS ON C IRCUITS AND S YSTEMS I, the IEEE T RANSACTIONS ON C IRCUITS AND SYSTEMS II, and the Journal of Circuits, Systems, and Computers.