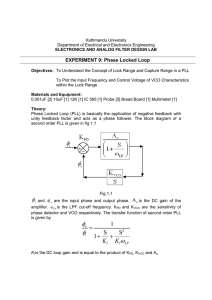

Fully Integrated CMOS Phased

advertisement