UNIVERSITY OF SOUTHERN MAINE Dept. of Electrical Engineering

advertisement

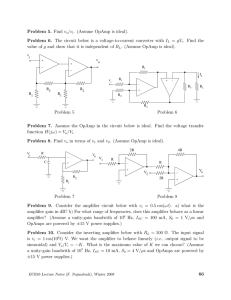

========================================================================================== UNIVERSITY OF SOUTHERN MAINE Dept. of Electrical Engineering TEST #3 Prof. M.G.Guvench ELE343/02 ========================================================================================== Part A: Calculators, Notes, Memory Cards, Books are NOT allowed! PUT YOUR ANSWERS ON THE BLANK SPACES PROVIDED, DO NOT USE ADDITIONAL PAPER (60 points) NO PARTIAL CREDITS WILL BE GIVEN TO ANSWERS WITH INCOMPLETE OR WRONG CIRCUITS OR CIRCUITS WITH MISSING GROUNDS. Assume availability of the following components to DESIGN and DRAW the circuits of the op. amp. applications listed below: Operational Amplifier: VSupply = ± 9VDC, Maximum Output Swing = VSupply - 0.8V, IOUT MAX = 5 mA, Avo = 100,000 Gain Bandwidth Product = 2 MHz Input Bias Currents < 0.01 mA NPN/PNP Transistors: Silicon NPN βNPN = 50 and Silicon PNP βPNP = 150 Capacitor: Zener: Inductor: 1nF and 1µF Diodes: Silicon with 0.7V average forward drop 6.2V IZMIN = 3 mA PDMAX = 250 mW 100 µH ........ PDMAX = ?? You decide! Make sure that all opamp circuits have a balanced resistive path for input bias currents to minimize offsets caused by them. A.1 A Difference Amplifier with a guaranteed bandwidth of 20 Khz, 10 KΩ minimum input impedance and designed for maximum possible gain employing the op amp specified above. What is the maximum possible gain of this amplifier? What is the maximum expected peak-to-peak output voltage swing of this amplifier? What is the new value of the maximum swing if the output drives a load resistance of RL= 0.1KΩ ? Avo = VOUTMAX-PP = VOUTMAX-PP (with RL = 0.1 K) = A.2 A half-wave precision rectifier which passes only the positive half of the inputted waveform, amplifies it by +10 (plus, non-inverting!) and has an input stage with Rin = 10K (exactly!) input resistance and a unity gain buffer at its output. (Explain, in one sentence why you need a buffer amplifier at the output.) A.3 A power operational amplifier which can deliver output swings in both polarities. What are the maximum voltage and the maximum current values your design can deliver to a load? Design a power amplifier which has a non-inverting gain of 10 using your power op. amp. What will happen if you take the feedback from OpAmp's output rather than across the load? Explain it by drawing expected output waveforms for a sinusoidal input of waveform of 100mV peak. A.4 A multi-stage Multi-Input Integrator Amplifier impedance and satisfies circuit which has very high (theoretically infinite) input vout = -10v2(t) + 100 ∫ [ v1(t) +2.v2(t) ]dt starting at t = 0+. A.5 Use a summing amplifier and the half-wave rectifier block(s) designed in A.2 to implement "A Full-Wave OpAmp Precision Rectifier Amplifier Circuit" which puts out all positive output (!) with a net Gain = +100 and Rin = almost infinite. A.6 An OpAmp DC voltage regulator with a fixed voltage of +6.2VDC , and up to 3Amp output, no current limit. (You need a Darlington!) A.7 A Wien Bridge Oscillator complete with its op. amp. amplifier circuit and Zener diode amplitude limiting for peak to peak output of about 8Vp-p. (You specify the Zener diode breakdown voltage.) A.8 A Phase-Shift Oscillator complete with its op. amp. amplifier circuit circuit and Zener diode amplitude limiting for peak to peak output of about 8Vp-p. (You specify the Zener diode breakdown voltage.) A.9 A Second Order Band-Pass Filter Circuit implemented from a combination of Sallen-Key Low Pass and SallenKey High Pass Filters. Sketch the expecter Bode magnitude plots if ξ = 0.1 for each circuit on its side, showing Insertion Loss and Roll-off numbers. ========================================================================================== UNIVERSITY OF SOUTHERN MAINE Dept. of Electrical Engineering TEST #3 Prof. M.G.Guvench ELE343/02 ========================================================================================== Part B: Calculators and Memory Cards are allowed! (50 points) Assume availability of the following components in your design and analysis. Operational Amplifier: VSupply = ± 9VDC, Maximum Output Swing = VSupply - 0.8V, IOUT MAX = 5 mA, Avo = 100,000 Gain Bandwidth Product = 2 MHz Input Bias Currents < 0.01 mA NPN/PNP Transistors: Silicon NPN βNPN = 50 and Silicon PNP βPNP = 50 Capacitor: Zener: Inductor: 1nF and 1µF Diodes: Silicon with 0.7V average forward drop 6.2V IZMIN = 3 mA PDMAX = 250 mW 100 µH ........ PDMAX = ?? You decide! B.1 DESIGN an Op.Amp. DC POSITIVE (!!!) Voltage Regulator which will deliver to a resistive load currents up to 1.2 Amp at a variable voltage of 0VDC < VOUT < +12VDC (plus sign!) and will limit the current at 1.2 Amp. Assume the unregulated supply voltage varies between +18 VDC and +26 VDC. a. Draw the circuit diagram, first. (You will need Darlington transistors.) b. Calculate and specify the values of all R's, PDMAX of the transistors for the worst case. c. Draw the circuit diagram of a capacitive filtered BRIDGE (!) rectifier that will power this regulator from standard 110VRMS AC. For a maximum allowed peak-to-peak ripple voltage of 4V and an average (DC) unregulated supply voltage of 22V calculate the capacitor and transformer parameters. B.2 Phase-Frequency and Magnitude-Frequency plots of a Wien-Bridge-like feedback circuit suitable for building oscillators are shown in the attached figures. Your task is to employ the opamp supplied in combination with this circuit to design an oscillator. a. First determine the frequency of oscillations that will require the least possible amplification. Complete the design. What is the peak-to-peak voltage swing at your oscillator’s output. Employ VSupply = ± 9VDC. b. Add a Zener diode amplitude limiter that will limit the peak-to-peak swing at around 12Vp-p. c. I built a non-inverting amplifier in the lab to use with this oscillator. Unfortunately, due to the non-zero phase delay introduced by my real amplifier the oscillator's frequency has shifted. If the amplifier is introducing -25 degree phase shift use the plots to predict the new oscillation frequency and the minimum amplifier gain needed for this oscillation. d. What would the gain requirement be if you were to use a PHASE-SHIFT circuit to design this oscillator? Consider the finite gain-bandwith product of your OpAmp. To make it oscillate at the same frequency as the one above what value of GBW you would require the OpAmp to have? ..... BEST WISHES FOR A HAPPY SUMMER .....