1 - SNS College of Engineering

advertisement

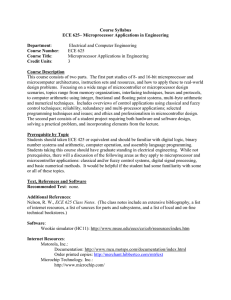

SNS COLLEGE OF ENGINEERING, COIMBATORE DEPARTMENT OF ELECTRONICS AND COMMUNICATION EC 2304 - MICROPROCESSOR & MICROCONTROLLER ACADEMIC YEAR: 2013-2014(Odd Semester) PUZZLES Class:III/Sem:V Prepared by S.Arul Mozhi/AP/ECE R.Saranya/AP/ECE SNSCE/ECE/Microprocessor & Microcontroller Page 1 1. Numbers are stored and transmitted inside a computer in a, b, 1+1 = 2 1+1 = 0 c, d, 15+15 =60 0E+01 =0F 2. The original ASCII codes ___________ bits or characters. (a) (b) I make I make one week one byte (c) (d) Count of interrupts in 8086 microprocessor SNSCE/ECE/Microprocessor & Microcontroller Subtract 1 from 16 Bytes Page 2 3. The 4-bit binary number 0111 represents a, -3+4 b, -3-4 c, 3+4 d, 3-4 4. The decimal number 255 may be represented by (a) 1111 1111B, (b) 1000 0000B, (c) EEEEH, (d) 0111 1111 5. The 8-bit binary number 1111 1111 represents -1 -1 -8 2 2 5 7 5 6. The decimal number 127 may be represented by the following binary numbers. a, Equivalent value of FFH b, 1’ s Complement of 0111 1111B c, EEH d, 2’ s Complement of 1000 0001B 7. A byte corresponds to (a) 22 bits (b) 24 bits (c) 23 bits (d) 25 bits SNSCE/ECE/Microprocessor & Microcontroller Page 3 8. The storage required for an image such as an X-ray is approximately M Bytes K G 9. A Kb corresponds to (a) 1024 bits (b) 1000 bytes (c) 210 bytes (d) 210 bits 10. A superscalar processor has a, Printer Mouse System Keyboard Display C, b, Fn11 Fn2 Fn3 Fn4 R A M SNSCE/ECE/Microprocessor & Microcontroller Page 4 d, 11. A 32-bit processor has B, A, I/O Devices 1 I/O Devices 2 I/O Devices 31 I/O Devices 32 32 Bit Registers D, C, 32 MB RAM 32 Bit Bus 12. Information is stored and transmitted inside a computer in a, b, 1+1 = 2 1+1 = 0 c, d, 15+15 =60 0E+01 =0F SNSCE/ECE/Microprocessor & Microcontroller Page 5 13. A parity bit is A, A, B, C…… B, 1 1 0 4 1 1 C, 1 1 0 1 1 1 1 0 1 1 D, SNSCE/ECE/Microprocessor & Microcontroller Page 6 14. The minimum number of bits required to store the hexadecimal number FF is A, 1 B, 2 1 8 4 C, 2 1 D, 128 64 32 16 8 4 2 1 15. A 20-bit address bus allows access to a memory of capacity A, 20 b, 2 * 20 2 C, 2 d, 20 * 20 SNSCE/ECE/Microprocessor & Microcontroller 2 Page 7 16. An FPU a, b, 13+14 F D E S F D E D E D 13.5 + 14 C, 1.5 * 2.8 D, 1 MB RAM 17. Pipelining improves CPU performance due to A, Memory Access Time B, 18. The system bus is made up of A, c, b, Data Bus Data Bus Control Bus SNSCE/ECE/Microprocessor & Microcontroller Page 8 19. A machine cycle refers to T1 T2 T3 T4 F D E S a, T1 C, b, F d, T3 E 20. Accessing disk storage is slower than accessing RAM by an order of A, b, 10 100 1 C, 1000 1 SNSCE/ECE/Microprocessor & Microcontroller 1 d, 100000 1 Page 9 21. The typical disk storage capacity of a PC is of the order of 32M Bytes 5120K 2G 22. Arrange the blocks in appropriate order ALU Control unit Input Memory unit Output 23. Pick the odd one out, a. Transducers b. Keyboard c. Toggle Switched d. Line printer SNSCE/ECE/Microprocessor & Microcontroller Page 10 24. Find out type of signal PC SP IR ID ? a. b. c. d. 25. What am I? Data Signals Control signals Instruction Bus SP a. b. c. d. X Y Z X C Register Memory Stack Queue SNSCE/ECE/Microprocessor & Microcontroller Page 11 26. FIFO indicates B, A, D, C, 27. Arrange the following in operating stages A, A+B Stage b, Memory C, Instruction d, Decoder Memory Result SNSCE/ECE/Microprocessor & Microcontroller Page 12 28. Which indicates clock period? B, A, C, D, 29. The largest delay in accessing data on disk is due a, Waiting Time b, Time C, Time TX RX SNSCE/ECE/Microprocessor & Microcontroller Page 13 30. Choose the correct format. A, Operational Code Addressing mode Operand Addressing Addressing mode Operational Code Operand Addressing Addressing mode Operational Code B, C, Operand Addressing D, Operational Code Addressing mode 31. What does it indicate? a. b. c. d. Immediate Addressing mode Register Addressing mode Direct Addressing mode Indirect Addressing mode 05 SNSCE/ECE/Microprocessor & Microcontroller DL CL BL AL DH CH BH AH Page 14 32. What does it indicate? DX CX BX(0005) AX a. Immediate Addressing mode b. Register Addressing mode c. Direct Addressing mode d. Indirect Addressing mode 33. SJUMP means sign jump A, True B, False 34. Fill the block given below. a. Compiler b. Assembler c. Converter d. Inverter Assembly Language Program Machine Language Program 35. Fill the following High Level Language Program a. b. c. d. Compiler ? Low level language program Assembly level language program Machine level program Compiled program 36. What does it indicate a. Input- Output Bus b. Control Bus c. Data lines SNSCE/ECE/Microprocessor & Microcontroller Page 15 d. Tristate Bus Output Input Enable/Disable 37. What does T3(2) indicate? Cycle P1 P2 P3 P4 1 T1(1) - - - 2 T1(2) T2(1) - - 3 T1(3) T2(2) T3(1) - 4 T1(4) T2(3) T3(2) T4(1) 38. What does it mean? a. b. c. d. Register Stack Accumulator Segmented Memory FFFF YYYY XXXX 0000 SNSCE/ECE/Microprocessor & Microcontroller Page 16 39. Empty space indicates what? ES SS DS CS 40. Fill the missing segment. ES DS CS 41. Match the following Status Bits S4 S3 0 0 0 1 1 0 1 1 Segments SS DS ES SS SNSCE/ECE/Microprocessor & Microcontroller Page 17 42. Match the following BHE 0 A0 0 0 1 1 0 1 1 S2 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1 Data Access None Both higher & lower bank Lower order bank access Lower order bank access 43. Match the following S0 0 1 0 1 0 1 0 1 Control function Interrupt Ack I/O read I/O write Halt Opcode fetch Memory read Memory write No operation 44. Match the following QS1 0 0 1 1 QS0 Data Access 0 Idle State First byte of opcode 1 has entered queue 0 Queue empty Subsequent byte of 1 opcode has entered queue SNSCE/ECE/Microprocessor & Microcontroller Page 18 45. Match the following IO/M DT/R SSO Control function bar bar bar 0 0 0 Interrupt Ack 0 0 1 Memory read 0 1 0 Memory write 0 1 1 Halt 1 0 0 Opcode fetch 1 0 1 I/O read 1 1 0 I/O write 1 1 1 No operation 46. The following address resides at 00001, 00003, 00005 a. b. c. d. Higher order bank Lower order bank Both None of these 47. Pick the odd one out a. ALE is made high b. M/IO bar is made high c. Data is put on data lines d. DT/R bar is low 48. Fill in the blanks given below G1.(G2B.___________) = 1 SNSCE/ECE/Microprocessor & Microcontroller Page 19 49. What type of interrupts indicated by (a), (b), & (c) (c) 255 254 (b) (a) … … 01 00 50. Interrupt vector type multiply by 4 = ______________ 51. Match the following Type/vector 0 1 2 3 4 Specific Interrupt INT soft int Non-maskable Divide by zero INT0 Single step SNSCE/ECE/Microprocessor & Microcontroller Page 20 52. Arrange the following in priority order. NMI Divide by zero Single step INTR INT0 53. Match the following Pins Reset Test Functions DMA request Extend the no of cycles Pushes the flag register, Ready CS,IP to stack Brings the CPU out of Hold idle state . 54. Name the type of addressing mode SNSCE/ECE/Microprocessor & Microcontroller Page 21 55. Name the type of addressing mode 56. Pick the odd one out a. b. c. d. ORG OFFSET LABEL DUP 57. LODSB comprises the following (AL) (DS:SI) True or False 58. MOVSB comprises the following (ES:DI)<-- (AL) True or False SNSCE/ECE/Microprocessor & Microcontroller Page 22 59. Tell the operation happens in executing below instruction TEST dest, src 60. Fill the empty block. ? ? CL ? ? BH AL ? 61. In 8085 name the 16 bit registers. B, A, PC C, Instruction SNSCE/ECE/Microprocessor & Microcontroller Register Page 23 62. BHE of 8086 processor signal is used to interface the A, b, 00007 00005 00003 00001 00008 00006 00004 00002 C, I/O Devices 63. In8085 are of the following statements is not true A)Co processor is interfaced in max mode. B)Co processor is interfaced in mIN mode C)Co processor is interfaced in max/min mode. D)Supports pipelinig. Ans-(B) 64. In which T-state does the CPU sends the address to memory or I/O and the ALE signal for demultiplexing SNSCE/ECE/Microprocessor & Microcontroller Page 24 65. In a DMA write operation the data is transferred a, I/O B, I/O SNSCE/ECE/Microprocessor & Microcontroller Page 25 C, D, I/O I/O 66. Which type of JMP instruction assembles if the distance is 0020h bytes a, Data segment SNSCE/ECE/Microprocessor & Microcontroller Page 26 b, Code segment Data segment 67. Which of the following is true with respect to EEPROM? (A) contents can be erased byte wise only. (B) contents of full memory can be erased together. (C) contents can be erased using ultra violet rays (D) contents cannot be erased 68. Number of the times the instruction sequence below will loop before coming out of loop is MOV AL, 00h A1: INC AL JNZ A1 (A) 00 (B) 01 (C) 255 (D) 256 69. What will be the contents of register AL after the following has been executed MOV BL, 8C MOV AL, 7E ADD AL, BL (A) 0A and carry flag is set (B) 0A and carry flag is reset (C) 6A and carry flag is set (D) 6A and carry flag is reset SNSCE/ECE/Microprocessor & Microcontroller Page 27 70. Direction flag is used with (A) String instructions. (B) Stack instructions. (C) Arithmetic instructions. (D) Branch instructions. A, b, MOVSB, POP & PUSH STOSB C, d, ADD, SUB, MUL, DIV JMP, CALL, LOOP 71. The devices that provide the means for a computer to communicate with the user or other computers are referred to as: SNSCE/ECE/Microprocessor & Microcontroller Page 28 72. The software used to drive microprocessor-based systems is called 73. The circuits in the 8085A that provide the arithmetic and logic functions are called the A, Printer Mouse System Keyboard Display B, C, CPU ALU 74. How many buses are connected as part of the 8085A microprocessor? A, Number of binary digits B, Number of bits in a byte SNSCE/ECE/Microprocessor & Microcontroller Page 29 C, Number of memory segments in 8086 75. The ________ ensures that only one IC is active at a time to avoid a bus conflict caused by two ICs writing different data to the same bus. 76. How many bits are used in the data bus? 77. Single-bit indicators that may be set or cleared to show the results of logical or arithmetic operations are the: C, a, b, DL CL BL AL DH CH BH AH SNSCE/ECE/Microprocessor & Microcontroller Monitor Page 30 78. The technique of assigning a memory address to each I/O device in the computer system is called: A. memory-mapped I/O B. ported I/O C. dedicated I/O D. wired I/O 79. When was the first 8-bit microprocessor introduced? A. 1969 B. 1974 C. 1979 D. 1985 80. What type of circuit is used at the interface point of an output port? a, b, S R EN S Q R Q bar c, SNSCE/ECE/Microprocessor & Microcontroller Page 31 81. I/O mapped systems identify their input/output devices by giving them a(n) ________. a, b, PPI c, IN & OUT 82. The register in the 8085A that is used to keep track of the memory address of the next op-code to be run in the program is the: A, B, C, AL AH SNSCE/ECE/Microprocessor & Microcontroller Page 32 83. The control bus and memories share a bidirectional bus in a typical microprocessor system. True or False 84. The 8085A is a (n): A, 0 1 2 7 0 1 2 7 0 1 2 15 0 1 2 15 B, C, D, 85. Because microprocessor CPUs do not understand mnemonics as they are, they have to be converted to ________. A, b, 0E+01 =0F 15+15 =60 c, d, 1+1 = 0 1+1 = 2 SNSCE/ECE/Microprocessor & Microcontroller Page 33 86. What is the difference between a mnemonic code and machine code? A. There is no difference. B. Machine codes are in binary, mnemonic codes are in shorthand English. C. Machine codes are in shorthand English, mnemonic codes are in binary. 87. Identify the following buses? A, b, RD,WR C, 88. What kind of device is used to convert mnemonic code to machine code? A, Assembly Language Program Machine Language Program B, High Level Language Program Machine Language Program 89. LDA addr and STA addr are Fortran language instructions stored in an external memory IC for a microprocessor. A, True B,False SNSCE/ECE/Microprocessor & Microcontroller Page 34 90. The 8051 has ________ 16-bit counter/timers. 91. When the 8051 is reset and the line is HIGH, the program counter points to the first program instruction in the: 92. An alternate function of port pin P3.4 in the 8051 is: SNSCE/ECE/Microprocessor & Microcontroller Page 35 93. Which of the following commands will move the number 27H into the accumulator? A. MOV A, P27 B. MOV A, #27H C. MOV A, 27H D. MOV A, @27 94. What is the difference between the 8031 and the 8051? A. The 8031 has no interrupts. B. The 8031 is ROM-less. C. The 8051 is ROM-less. D. The 8051 has 64 bytes more memory. 95. The contents of the accumulator after this operation MOV A,#2BH ORL A,00H will be: A. 1B H B. 2B H C. 3B H D. 4B H 96. Which is/are the basic refresh mode(s) for dynamic RAM? A. Burst refresh B. Distributed refresh C. Open refresh D. Burst refresh and distributed refresh SNSCE/ECE/Microprocessor & Microcontroller Page 36 97. For the given circuit, what memory location is being addressed? A. 10111 B. 249 C. 5 D. 157 98. Which of the following RAM timing parameters determine its operating speed? A. tACC B. tAA and tACS C. tCO and tOD D. tRC and tWC SNSCE/ECE/Microprocessor & Microcontroller Page 37 99. For the given circuit, which of the following is correct? A. The number 5 is being written to the memory at address location 203. B. The chip has not been enabled, since the EN terminal is 0; therefore, nothing will be written to the chip and the output is tri-stated. C. Decimal 10 is being written into memory location 211. D. The read/write line is LOW; therefore, decimal 5 is being stored at memory location 211. 100. What is the significance of the inverted triangles on the outputs of the device in the given figure? A. They represent inverters and mean that the outputs are active-LOW. B. They represent buffers and mean that the outputs can drive 40 TTL loads, instead of the normal 10. SNSCE/ECE/Microprocessor & Microcontroller Page 38 C. It means that the outputs will be active only if a change has occurred at that memory location since the last read/write cycle. D. The outputs are tristated. SNSCE/ECE/Microprocessor & Microcontroller Page 39