2 R R R + = - ECE Users Pages

advertisement

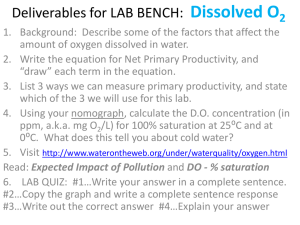

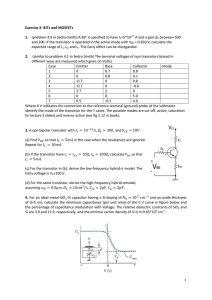

ECE3030 Physical Foundations of Computer Engineering, Fall 2015 Homework 8 Solutions Prelude for Q1 and Q2: Effective resistance is average of saturation and linear region resistance: Rt = Rlin + Rsat 2 This exercise will be divided into the following three parts: part a), calculation of resistance in the liner region Rlin; part b), calculation of resistance in saturation region Rsat; and part c), calculation of the total resistance Rtot. Note A: For the discussion below, remember that , = VGS – VTN for n-type transistors and , = VSG + VPN = VSG - |VPN | for p-type transistors is the point of transition from the linear region to the saturation region. Please, note the diference along this HW between , (in slides noted as well as ) and which is the average between , and the maximum value that we can provide to VDS, in this case, VDD. Note B: Also, for this problem we can assume VGS = VDD for n-type transistors and VSG = VDD (or equivalently VGS = -VDD) for p-type transistors. Note C: All the calculated currents are refered to the drain. Then, the subscript D is not taken into account in the notation to describe drain currents for these problems. 1) (25 pts.) You are given a 65nm n-type transistor with a threshold voltage of VTN = 0.2 V, a transconductance of k’ = 100 microamps/V2 and a W/L of 1.5. Assuming that the transistor is fully on (i.e., VG = VDD), find the effective resistance for the transistor assuming a power supply voltage of VDD = 1.2 V. For ID, use the equations given in the Electronic Computing Machines lecture. (a) To calculate linear region resistance we need to find Vlin and Ilin. To find Vlin , = , − − − = = = 2 2 2 2 = 1.2 − 0.2 1 = = 0.5V 2 2 = 0.5V Note 1.1: For this case, a connection to ground, i.e., VS = 0V, is assumed. We have chosen the voltage midpoint (Vlin) between VS and , in the linear region. We next find the drain current in the linear regime (formula). Recall that for the linear region = 1 ′ − − 2 2 Since VGS = VDD (see Note B) and = = = = , = = , we have − 1 − ′ − − 2 2 2 2 1 1 3 ′ − 2 − − 2 = ′ − 2 2 8 8 3 = 1.5750 ∗ 10ି 1.2 − 0.22 = 4.22 ∗ 10ିଷ = 421.88μA 8 = 421.88μA Calculating the linear region resistance, − 1 ,ௌ் /2 4 2 = = = = 3 3 ′ − 2 ′ 8 − = 4 1 4 = = 1.19kΩ 3 1.5 ∗ 750 ∗ 10−6 1 3.375 ∗ 10−3 = 1.19kΩ Or simply = 0.5V = = 1.19kΩ 421.88μA Note 1.2: Observe that VGS = VDD for this calculation. Also note that under this assumption we found Vlin = VD,SAT /2 = (VDD-VTN)/2. See that VS = 0 is also an assumption taken for this relation between Vlin and VD SAT. Note 1.3: Since for this case VD,SAT concides with the transition point from the linear to the saturation region (assuming VGS = VDD and VS = 0), any value for VDS less than VD,SAT (except 0 V) will be in the linear region. In particular, Vlin = VD,SAT/2 will be a mid-point in the linear region. (b) Wheras Rlin is calculated as the slope in the midpoint between the condition of saturation and cut-off, Rsat is calculated at the midpoint between the saturation and the maximum value of VDS, i.e., for this case VDD. To calculate saturation region resistance we need to find Vsat and Isat. For calculations in this context, Vsat is defined as a region. Therefore, ௦௧ = , + − + − + 2 − = = = 2 2 2 2 ௦௧ = 2 ∗ 1.2 − 0.2 2.2 = = 1.1V 2 2 ௦௧ = 1.1V Note 1.4: Please see Note 0. Find the drain current in saturation regime: ௦௧ = 1 1 ′ − ்ே ଶ = ′ − ்ே ଶ 2 ீ௦ 2 ௦௧ = (1.5) 750 ∗ 10 −6 1 −6 1ଶ = 1.5 375 ∗ 10 = 562.5μA 2 ௦௧ = 562.5μA Calculating the saturation region resistance, ௦௧ ௦௧ = 1 2 − ்ே ௦௧ (2 − ்ே ) = = 2 = ௦௧ ′ 1 − ଶ ′ − ଶ ்ே ்ே 2 2 ∗ 1.2 − 0.2 1.5 ∗ 750 ∗ 10 −6 1.2 − 0.2ଶ = 2.2 1.5 ∗ 750 ∗ 10 −6 = 2.2 11.25 ∗ 10 −3 = 1.96kΩ ௦௧ = 1.96kΩ Or simply ௦௧ = ௦௧ 1.1V = = 1.96kΩ ௦௧ 562.5μA (c) To calculate the effective resistance, we take the average of the linear and saturation resistance as discussed before as follows: ௧ = + ௦௧ 1.19 + 1.96 = kΩ = 1.58kΩ 2 2 2) (25 pts.) You are given a 65nm p-type transistor with a threshold voltage of VTP = -0.3 V, a transconductance of k’ = 100 microamps/V2 and a W/L of 6. Assuming that the transistor is fully on (i.e., VG = 0), find the effective resistance for the transistor assuming a power supply voltage of VDD = 1.2 V. For Id, use the equations given in the Electronic Computing Machines lecture suitably and properly modified to account for the fact that this case is a p-type MOSFET. (a) To calculate linear region resistance we need to find Vlin and Ilin. To find Vlin , = , + + − | | = = = 2 2 2 2 = 1.2 − 0.3 0.9 = = 0.45V 2 2 = 0.45V Note 2.1: For this case, VS = is assumed. We have chosen the voltage midpoint (Vlin) between , and VSD = 0V in the linear region. We next find the drain current in the linear regime (formula). Recall that for the linear region = 1 ′ − | | − 2 2 Since VSG = VDD (see Note 0) and = = we have = = , = = = | | − | | 1 − | | ′ − | | − 2 2 2 2 1 1 3 2 2 2 ′ − | | − − | | = ′ − | | 2 8 8 3 = 6100 ∗ 10ି 1.2 − 0.32 = 225 ∗ 10ି 0.92 = 182.25μA 8 = 182.25μA , Calculating the linear region resistance, − | | 1 ,ௌ் /2 4 2 = = = = 2 3 3 ′ − | | ′ 8 − | | = 4 1 4 = 106 = 2.47kΩ −6 3 6 ∗ 100 ∗ 10 0.9 1620 = 2.47kΩ Or simply = 0.45V = = 2.47kΩ 182.25μA Note 2.2: Observe that VSG = VDD for this calculation. Also note that under this assumption we found Vlin = VD,SAT /2 = (VDD - |VTP|)/2. Note 2.3: Since for this case VD,SAT concides with the transition point from the linear to the saturation region (assuming VSG = VDD), any value for VSD less than VD,SAT (except 0 V) will be in the linear region. In particular, Vlin = VD,SAT /2 will be a mid-point in the linear region. (b) Wheras Rlin is calculated as the slope in the midpoint between the condition of saturation and cut-off, Rsat is calculated at the midpoint between the saturation and the maximum value of VDS, i.e., for this case VDD. To calculate saturation region resistance we need to find Vsat and Isat. For calculations in this context, Vsat is defined as a region. Therefore, ௦௧ = + − | | + − | | + 2 − | | = = = 2 2 2 2 ௦௧ = 2 ∗ 1.2 − 0.3 2.1 = = 1.05V 2 2 ௦௧ = 1.05V Note 2.4: Please see Note B. Find the drain current in saturation regime: ௦௧ = 1 1 ′ − |் |ଶ = ′ − |் |ଶ 2 ௌீ 2 ௦௧ = (6) 100 ∗ 10 −6 1 −6 0.9ଶ = 3 81 ∗ 10 = 243μA 2 ௦௧ = 243μA Calculating the saturation region resistance, ௦௧ ௦௧ = 1 2 − | | ௦௧ (2 − | |) = = 2 = ௦௧ ′ 1 − | |ଶ ′ − | |ଶ 2 (2 ∗ 1.2 − 0.3) 6 ∗ 100 ∗ 10 −6 1.2 − 0.3ଶ = (2.1) 600 ∗ 10 −6 0.9ଶ = 2.1 3.645 ∗ 10 −3 = 4.32kΩ ௦௧ = 4.32kΩ Or simply ௦௧ = ௦௧ 1.05V = = 4.32kΩ ௦௧ 243μA (c) To calculate the effective resistance, we take the average of the linear and saturation resistance as discussed before as follows: ௧ = + ௦௧ 2.47 + 4.32 = kΩ = 3.4kΩ 2 2 3) (25 pts.) Derive a formula for the delay of an inverter with an equivalent resistance of Rn (both the nFET and the pFET have an equivalent resistance of Rn, i.e., the pFET transistor in the inverter is made wider to compensate for higher pFET resistance so that the result is a pull-up resistance of Rn) driving a load of CL where the delay is measured from 10% to 85% of the output voltage. If the rise and fall times are different, give both results. Your answer should be in terms of RnCL. In this question, there are two situations, namely, rise time delay and fall time delay, which are shown as below. The question asks for the time from 10% to 85% of VDD, hence, rise time. (a) rise time delay (b) fall time delay (a) For rise time delay, 1 Initial Condition: % 1 % 0.10 % ln0.90 % 0.85 % ln0.15 Final Condition: % 1 Therefore, the rise time delay is % % ln0.15 ln0.90 ln 1.79 0.90 0.15 (b) For the fall time delay, = Initial Condition: % = % = 0.85 % = 0.10 #$% = − " ln(0.10) % = − " ln(0.85) Final Condition: #$% = Therefore, the fall time delay is %& = #$% − % = − " ln0.10 + " ln0.85 = " ln 0.85 0.10 '() = 2.14 " NOTE: the rise and fall times are not equal! This inequality is due to the curves shown on the previous page and where the 10% and 85% voltage points intersect the curves; basically, the curve intersection points are not symmetric. YOU MAY NOT CONSULT HOMEWORK SOLUTIONS OF THESE EXACT PROBLEMS FROM OTHER COURSES, INCLUDING OTHER/PREVIOUS SECTIONS OF ECE 3030. ALL HOMEWORK SUBMISSIONS MUST INCLUDE YOUR NAME, COURSE NUMBER, SECTION, AND THE HOMEWORK SET NUMBER. ALL SHEETS MUST BE STAPLED TOGETHER. ALL WRITING MUST BE EASY TO READ (FOR EXAMPLE, YOU MAY HAVE TO WRITE ONLY ON ONE SIDE OF EACH SHEET OF PAPER THAT YOU SUBMIT AND MAY NOT BE ABLE TO USE RECYCLED PAPER). FAILURE TO FOLLOW INSTRUCTIONS MAY RESULT IN ZERO POINTS. ALL WORK MUST BE YOUR OWN. NO PLAGIARISM IS ALLOWED, AND YOU MUST PROPERLY REFERENCE ALL SOURCES OF YOUR INFORMATION – ALTHOUGH YOU SHOULD NOT LOOK FOR AND MAY NOT CONSULT “SOLUTIONS” AVAILABLE FROM OTHER SOURCES (TO REPEAT, YOU MAY NOT CONSULT HOMEWORK SOLUTIONS OF THESE EXACT PROBLEMS FROM OTHER COURSES!).