Lecture24-Digital Circuits

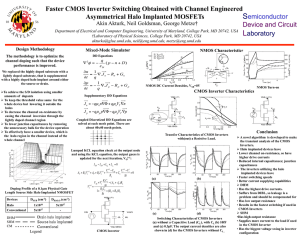

advertisement

EE105 – Fall 2014 Microelectronic Devices and Circuits Prof. Ming C. Wu wu@eecs.berkeley.edu 511 Sutardja Dai Hall (SDH) Lecture24-Digital Circuits-CMOS Inverters 1 The Ideal Inverter The ideal inverter has the following voltage transfer characteristic (VTC) and is described by the following symbol V+ and V- are the supply rails, and VH and VL describe the high and low logic levels at the output Lecture24-Digital Circuits-CMOS Inverters 2 1 Logic Level Definitions • An inverter operating with power supplies at V+ and 0 V can be implemented using a switch with a resistive load • The switch could be a mechanical device such as a wall switch or relay, a vacuum tube, or an MOS or bipolar transistor Lecture24-Digital Circuits-CMOS Inverters 3 NMOS Inverter with a Resistive Load • Resistor R is used to “pull” the output high. MS “Off” • MS is the switching transistor used to force the output low. • The size of R and the W/L ratio of MS are the design factors that need to be chosen. MS “On” Lecture24-Digital Circuits-CMOS Inverters 4 2 NMOS Inverter with a Resistive Load Load Line Visualization Q-pts for VL and VH on the NMOS device output (iD -vDS) characteristics. Load line equation: vDS = VDD − iD R VL VH Lecture24-Digital Circuits-CMOS Inverters 5 Logic Level Definitions Voltage Levels (cont.) Note that for the voltage transfer characteristic (VTC) of the nonideal inverter, there is now an undefined logic state. Lecture24-Digital Circuits-CMOS Inverters Noise Margin: NMH = VOH – VIH NML = VIL - VOL 6 3 Logic Level Definitions Voltage Levels • VL – The nominal voltage corresponding to a low-logic state at the output of a logic gate for vi = VH • VH – The nominal voltage corresponding to a high-logic state at the output of a logic gate for vi = VL • VIL – The maximum input voltage that will be recognized as a low input logic level • VIH – The maximum input voltage that will be recognized as a high input logic level • VOH – The output voltage corresponding to an input voltage of VIL • VOL – The output voltage corresponding to an input voltage of VIH Lecture24-Digital Circuits-CMOS Inverters 7 Logic Gate Design Goals • An ideal logic gate is highly nonlinear and attempts to quantize the input signal to two discrete states. In an actual gate, the designer should attempt to minimize the undefined input region while maximizing noise margins. • The input should produce a well-defined output, and changes at the output should have no effect on the input. • Voltage levels at the output of one gate should be compatible with the input levels of a following gate. • The gate should have sufficient fan-out and fan-in capabilities. • The gate should consume minimal power (and area for ICs) and still operate under the design specifications. Lecture24-Digital Circuits-CMOS Inverters 8 4 Dynamic Response of Logic Gates Propagation Delay • Propagation delay describes the amount of time between the input reaching the 50% point and the output reaching the 50% point. V50% = V H + VL 2 • The high-to-low propagation delay, τPHL, and the low-to-high propagation delay, τPLH, are € usually not equal, but can be combined as an average value: τP = Lecture24-Digital Circuits-CMOS Inverters τ PHL + τ PLH 2 9 € Dynamic Response of Logic Gates Power-Delay Product • The power-delay product (PDP) is a metric that describes the amount of energy (Joules) required to perform a basic logic operation and is given by the following equation where P is the average power dissipated by the logic gate: PDP = Pτ P Lecture24-Digital Circuits-CMOS Inverters 10 5 Review of Boolean Algebra A Z A B Z A B Z A B Z A B Z 0 1 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 1 1 0 1 0 0 1 0 0 1 1 NOT Truth Table 1 0 1 1 0 0 1 0 0 1 0 1 1 1 1 1 1 1 1 1 0 1 1 0 OR Truth Table AND Truth Table NOR Truth Table NAND Truth Table Z = A+ B Z = AB Z = A +B Z = AB Z=A € Lecture24-Digital Circuits-CMOS Inverters € 11 Logic Gate Symbols and Boolean Expressions Lecture24-Digital Circuits-CMOS Inverters 12 6 CMOS Technology • Complementary MOS, or CMOS, needs both PMOS and NMOS devices for the logic gates to be realized • The concept of CMOS was introduced in 1963 by Wanlass and Sah, but it did not become common until the 1980’s as NMOS microprocessors were dissipating as much as 50 W and an alternative design technique was needed • CMOS dominates digital IC design today Lecture24-Digital Circuits-CMOS Inverters 13 CMOS Inverter Circuit • When vI is pulled high (to VDD), the PMOS transistor is turned off, while the NMOS device is turned on pulling the output down to VSS • When vI is pulled low (to VSS), the NMOS transistor is turned off, while the PMOS device is turned on pulling the output up to VDD Lecture24-Digital Circuits-CMOS Inverters 14 7 CMOS Inverter Fabrication • The CMOS inverter consists of a PMOS device stacked on top on an NMOS device, but they need to be fabricated on the same wafer • To accomplish this, the technique of “n-well” implantation was developed as shown in this cross-section of a CMOS inverter Lecture24-Digital Circuits-CMOS Inverters 15 CMOS Inverter Static Characteristics: vI = VL • For vI = VL ≤ VTN, MN is off, and MP is on. Therefore VH = VDD, ID = 0, and there is no static power dissipation. Lecture24-Digital Circuits-CMOS Inverters 16 8 CMOS Inverter Static Characteristics: vI = VH • For vI = VH = VDD, VL = 0 V, and ID = 0 A which means that there is no static power dissipation Lecture24-Digital Circuits-CMOS Inverters 17 CMOS Inverter Voltage Transfer Characteristics The VTC shown is for a CMOS inverter that is symmetrical (Kp = Kn). Lecture24-Digital Circuits-CMOS Inverters 18 9 CMOS Inverter Noise Margins (cont.) KR = KN KP VIH = 2K R (VDD − VTN + VTP ) (VDD − K RVTN + VTP ) − K R −1 (K R −1) 1+ 3K R € NM H = VOH − VIH (K R + 1)VIH − VDD − K RVTN − VTP VOL = VIL = NM L = VIL − VOL 2K R 2 K R (VDD − VTN + VTP ) (VDD − K RVTN + VTP ) − K R −1 (K R −1) K R + 3 VOH = (K R + 1)VIL + VDD − K RVTN − VTP Lecture24-Digital Circuits-CMOS Inverters 2 19 € CMOS Inverter Propagation Delay Estimate • The two modes of capacitive charging/discharging that contribute to propagation delay Lecture24-Digital Circuits-CMOS Inverters 20 10 CMOS Inverter Rise and Fall Times τ PHL tf t1 t2 Lecture24-Digital Circuits-CMOS Inverters RC charging (or discharging) is exponential: # t & Δv(t) = ΔV exp % − ( $ RC ' # t & At 10%, 0.1 = exp % − 1 ( $ RC ' # t & At 90%, 0.9 = exp % − 2 ( $ RC ' # 0.9 & Fall time: t f = t2 − t1 = RC ln % ( = 2.2RC $ 0.1 ' # τ & At 50%, 0.5 = exp % − PHL ( ⇒ τ PHL = 0.69RC $ RC ' Therefore, t f ≅ 3τ PHL Similarly, tr ≅ 3τ PLH 21 CMOS Inverter Propagation Delay Estimate (cont.) 02 * $ V − V ' 2VTN 42 TN τ PHL = RonN C 1ln,4& H −1 + 5 / ) 23 + % V H + VL ( . V H − VTN 26 1 RonN = K n (V H − VTN ) τp = τ PHL + τ PLH = τ PHL = 1.2RonN C 2 • If it is assumed the inverter in “symmetrical” with (W/L)P = 2.5(W/L)N, then τPLH = τPHL € Lecture24-Digital Circuits-CMOS Inverters 22 11 CMOS Inverter Performance Scaling • State-of-the-art short gate length technologies are hard to analyze • Scaling can be used to properly set W/L for a given load capacitance relative to reference gate simulation with a reference load. τP = (W / L ) × "$ CL ' %' × τ Pr ef (W / L ) ' $# CLref '& or ' " W % " W % " τ Pr ef % " CL ' '×$ $ ' = $ '×$ # L & # L & # τ P & $# CLref % '' & • Scaling allows us to calculate a new geometry (W/L)' in terms of a target load and delay. Lecture24-Digital Circuits-CMOS Inverters 23 CMOS Logic Dynamic Power Dissipation • There are two components that add to dynamic power dissipation: – Capacitive load charging at a frequency f given by: PD = CVDD2 f – The current that occurs during switching which can be seen in the figure Lecture24-Digital Circuits-CMOS Inverters 24 12 CMOS Logic Power-Delay Product • The power-delay product is given as: PDP = Pavτ P 2 2 Pav = CVDD f = CVDD 1 T • The figure shows a symmetrical inverter switching waveform 2t r 2(2τ P ) = = 5τ P 0.8 0.8 2 2 CVDD CVDD PDP ≥ τP = 5τ P 5 T ≥ t r + t a + t f + tb = Lecture24-Digital Circuits-CMOS Inverters 2 PMOS in series à double (W/L) to obtain similar RON,P 25 CMOS Logic NOR Gate A B Y 0 0 1 0 1 0 (W/L)PMOS = 2.5x (W/L)NMOS to make up for lower hole mobility 1 0 0 1 1 0 Y = A+B Basic CMOS logic gate structure Lecture24-Digital Circuits-CMOS Inverters CMOS NOR gate implementation Reference Inverter 26 13 A B Y 0 0 1 CMOS Logic NAND Gates (W/L)PMOS is usually 2.5x (W/L)NMOS to make up for lower hole mobility 0 1 1 1 0 1 1 1 0 Y = AB 2 NMOS in series à double (W/L) to obtain similar RON,N CMOS NAND gate implementation Lecture24-Digital Circuits-CMOS Inverters Reference Inverter 27 Complex CMOS Logic Gate Design Example (cont.) • From the PMOS graph, the PMOS network can now be drawn for the final CMOS logic gate while once again considering the longest PMOS path for sizing Two equivalent forms of the final circuit Lecture24-Digital Circuits-CMOS Inverters 28 14