DEI1058 - DEIAZ.com

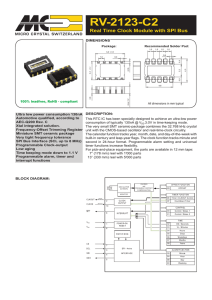

advertisement

Device Engineering Incorporated DEI1058 Six Channel Discrete-to-Digital Interface Sensing 28 Volt/Ground 385 East Alamo Drive Chandler, AZ 85225 Phone: (480) 303-0822 Fax: (480) 303-0824 E-mail: admin@deiaz.com Features: • • • • • • • Senses six 28V / Ground inputs Small footprint (16L SOIC NB) Inputs are lightning protected per DO-160D Level 3 TTL/CMOS-Compatible Tri-state outputs Low Cost -55ºC to +85ºC operating temperature range. 100% Final testing Functional Description: The DEI1058 is a six channel discrete-to-digital interface BiCMOS device. It senses six 28V/Ground discrete signals of the type commonly found in avionic systems. The inverted outputs are TTL/ CMOS compatible and are enabled by the OE and CE pins. The inputs of this small 16 lead narrow body SOIC device are lightning protected to meet the requirements of DO160D waveforms 3, 4, and 5 Level 3. See figures 5-7. OE CE VDD 2K 12K IN 1 + OUT 1 - 2K 12K + IN 2 2K 12K + IN 3 - + IN 4 - + IN 5 OUT 5 - 2K 12K + IN 6 16 GND IN 2 2 15 OUT 1 IN 3 3 14 OUT 2 IN 4 4 13 OUT 3 IN 5 5 12 OUT 4 IN 6 6 11 OUT 5 OE 7 10 OUT 6 CE 8 9 OUT 4 2K 12K 1 OUT 3 2K 12K IN 1 OUT 2 - OUT 6 - VDD 12K 2K 3.1V Reference V DD GND Figure 1: Concept Drawing © 2007 Device Engineering Figure 2: Pinout Diagram 1 of 5 NOT RECOMMENDED FOR NEW DESIGN – Use DEI1026A DS-MP-01058 Rev. E Table 1: Absolute Maximum Ratings PARAMETER MIN -0.3 MAX 7.0 UNITS V -5 +35 * V VSS - 0.3 VDD + 0.3 V -600 -300 +600 +300 V Storage Temperature -55 125 o C Operating Free Air Temperature -55 85 o C C C Supply Voltage VDD Discrete Input Voltage (Pins 1-6) Digital Input Voltage (CE and OE) Lightning Protection (Pins 1-6) DO160D, Waveform 3; Level 3 DO160D, Waveforms 4, and 5; Level 3 Lead Soldering Temperature (10 Seconds Max) - 280 o Body Soldering Temperature (10 Seconds Max) - 210 o The DEI1058 contains circuitry to protect inputs from damage due to electrostatic discharge. It has been characterized per JEDEC A114-A Human Body Model to Class 1. Observe precautions for handling and storing Electrostatic Sensitive Devices. * The DEI1058 will withstand the transient surge DC voltage step function loci limits for category B equipment per MILSTD-704A. Table 2: DEI1058 Device Operating Characteristics PARAMETER CONDITIONS SYMBOL Supply Voltage VDD Free Air Operating Temp. TA VDD = 4.5 – 5.5 V Logic Output Sink Current IOL VDD = 4.5 – 5.5 V Logic Output Source Current IOH VDD = 4.5 – 5.5 V MIN TYP MAX 4.5 5.0 5.5 -55 UNITS V 85 o 5.0 mA -5.0 C mA Table 3: DEI1058 Logic Truth Table CE (Chip Enable) OE (Output Enable) Discrete Input Output 0 0 28V 0 0 0 Ground 1 1 X X High Z X 1 X High Z © 2007 Device Engineering 2 of 5 NOT RECOMMENDED FOR NEW DESIGN – Use DEI1026A DS-MP-01058 Rev. E Table 4: DEI1058 Electrical Characteristics (TA = -55ºC TO +85ºC, VDD = 4.5 TO 5.5 V, Unless otherwise noted) SYMBOL PARAMETER CONDITIONS MIN TYP MAX Power Supply and Thermal Data Supply Current VIN = VDD (all inputs) VDD = 5.5 V Junction to Ambient Junction to Case Max. Junction Temperature IDD Thermal Resistance Max. Junction Temperature θJA θJC ΤJmax 5 10 110 60 UNITS mA °C/W 125 °C 3.0 V Discrete Input Characteristics 28 Volt input voltage High Output VSG 28 Volt input voltage Low Output VSO Ground State Input Resistor RIG Input source current IIO Reverse Leakage Current IIR Voltage source from input terminal to ground for Logic High Output. Voltage source from input terminal to ground for Logic Low Output. Resistor from input to Ground to guarantee Logic High Output. Current sourced into 100 Ohm resistor to ground. 3.5 V 100 -100 VIN = 35 V, VDD = 0 V Ω µA -330 100 µA Logic Input Characteristics CE, OE input logic 1 level VIH CE, OE input logic 0 level VIL 2.0 V 0.8 V DC Output Characteristics Output logic 1 level (TTL) VOH IOH = -5 mA. Output logic 0 level (TTL) VOL IOL = 5 mA. Output logic 1 level (CMOS) VOH IOH = -100 µA Output logic 0 level (CMOS) VOL IOL = 100 µA Off-state Output Current IOZ OE = VDD VDD = 5.5 V VOUT = 0 or VDD 2.4 V 0.4 VDD – 50mV V V VSS + 50mV V +/-10 µA Switching Characteristics I/O propagation delay tHL, tLH Refer to Figure 4. 150 ns Delay from CE or OE input (with output low) to output HI-Z tLZ Refer to Figure 3. 25 ns Delay from CE or OE input (with output HI-Z) to output low tZL Refer to Figure 3. 25 ns Delay from CE or OE input (with output high) to output HI -Z tHZ Refer to Figure 3. 25 ns Delay from CE or OE input (with output HI-Z) to output high tZH Refer to Figure 3. 25 ns © 2007 Device Engineering 3 of 5 NOT RECOMMENDED FOR NEW DESIGN – Use DEI1026A DS-MP-01058 Rev. E 3.0 3.0 OE or CE 1.5 1.5 0 0 tZL tLZ HIGH Z HIGH Z OUTPUT tHZ tZH HI 1.3 0.3 1.3 0.3 LO HIGH Z HIGH Z VIN = VSS RL = 1KΩ to V SS CL = 30pF VIN = VDD RL = 1KΩ to V DD CL = 30pF Figure 3: Enable to Output Propagation Delay INPUT 16V tHL tLH 2.4 OUTPUT 0.4 LO RL = 1K Ω to V DD CL = 30pF Figure 4: Input to Output Propagation Delay © 2007 Device Engineering 4 of 5 NOT RECOMMENDED FOR NEW DESIGN – Use DEI1026A DS-MP-01058 Rev. E V/I V Peak 25% to 75% of Largest Peak Largest Peak T1 = 6.4 microseconds ±20% T2 = 70 microseconds ±20% 50% t 0 50% 0 T1 t T2 Figure 5: DO160D Voltage Waveform #3 Figure 6: DO160D Voltage Waveform #4 VOC = 600V, ISC = 24A, Frequency = 1.0MHZ ±20% VOC = 300V, ISC = 60A V/I 5A: T1 = 40 microseconds ±20% Peak Notes: 1. VOC = Peak Open Circuit Voltage available at the calibration point. 2. ISC = Peak Short Circuit Current available at the calibration point. 3. Amplitude tolerances: +10%, -0% 4. The ratio of VOC to ISC is the generator source impedance to be used for generator calibration purposes. T2 = 120 microseconds ±20% 5B: T1 = 50 microseconds ±20% T2 = 500 microseconds ±20% 50% 0 T1 t T2 Figure 7: DO160D Voltage Waveform #5 VOC = 300V, ISC = 300A Pin 1 Dimensions are in IN (MM) 0.228 - 0.244 (5.791 - 6.198) 0.150 - 0.158 (3.810 - 4.013) 0.181 - 0.205 (4.597 - 5.207) 0.016 - 0.021 (0.406 - 0.533) 0.014 - 0.018 (0.356 - 0.457) 0.007 - 0.009 (1.178 - 0.229) 0.015 (0.381) 45 ° 0.386 - 0.393 (9.804 - 9.962) 3° - 6° 0.050 (1.270) BSC 0.004 - 0.008 (0.102 - 0.203) 0.053 - 0.069 (1.346 - 1.753) Figure 8: DEI1058 Mechanical Outline JEDEC MS-012-16 © 2007 Device Engineering 5 of 5 NOT RECOMMENDED FOR NEW DESIGN – Use DEI1026A DS-MP-01058 Rev. E