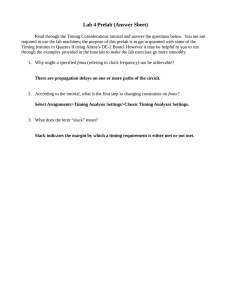

This work reports on SiGe HBT technology with fmax and fT of 350

advertisement

SiGe HBT Technology with fmax/fT = 350/300 GHz and Gate Delay Below 3.3 ps M. Khater, J. -S. Rieh, T. Adam, A. Chinthakindi, J. Johnson*, R. Krishnasamy*, M. Meghelli**, F. Pagette, D. Sanderson, C. Schnabel, K. T. Schonenberg, P. Smith, K. Stein, A. Stricker*, S. -J. Jeng, D. Ahlgren, and G. Freeman IBM Microelectronics, Rt. 52, M/S EM1, Hopewell Junction, NY 12533, *Essex Junction, VT 05452 ** IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 Email: mkhater@us.ibm.com / Phone: (845) 894-8711 / Fax: (845) 892-3039 Abstract This work reports on SiGe HBT technology with fmax and fT of 350 GHz and 300 GHz, respectively, and a gate delay below 3.3 ps. This is the highest reported speed for any Sibased transistor in terms of combined performance of fmax and fT both of which exhibit 300 GHz and above. Associated BVCEO and BVCBO are measured to be 1.7 V and 5.6 V, respectively. The dependence of device performance on bias condition and device dimension has been investigated. Considerations regarding the extraction of such high fmax and fT values are also discussed. Introduction The improvement in transistor performance, especially the operation speed, is an essential requirement for increased bandwidth and data rate for network communication systems. As Si-based technology enables large-scale integration, an increase in the operation speed of Si-based device is a key to the low-cost implementation of such systems. The performance of SiGe HBT has been significantly improved by vertical and lateral scaling as well as structural improvements [1-5]. A significant structural improvement is the implementation of a raised extrinsic base self-aligned to the emitter, as shown in Fig. 1, which allows reduction of base resistance (RB) and collector-to-base capacitance (CCB) independently. Recent work has focused on enhancing the operation speed of SiGe HBT, which have been favored over CMOS for RF/analog/ mixed-signal applications owing to their advantages in transconductance, 1/f noise, device matching, and power performance. In our previous work we reported a SiGe HBT with fT of 350 GHz and associated fmax of 170 GHz, which was achieved by vertical profile scaling, for a device with emitter size of AE=0.12×2.5 µm2 [2]. Our latest work demonstrated fT and fmax both of which exhibiting 300 GHz achieved through further vertical profile scaling for a device with the same emitter size [3]. In this work we demonstrate improvement of fmax to 350 GHz, with associated fT of 300 GHz, on the same device platform achieved through reduction of the parasitic components of RB. To the authors’ knowledge, this is the highest reported fmax value of 350 GHz with associated fT of at least 300 GHz for any Si-based transistor technology. The detailed device performance, including the effect of bias and emitter width, and the effect of extrapolation frequency on fmax and fT extracted values will be described in this work. A gate delay below 3.3 ps for a CML ring oscillator with devices of emitter size AE=0.10×1.5 µm2 fabricated using a different mask set design with the same process conditions will also be demonstrated. Device Structure and Process The device basic process steps for our previous work [1-3] were maintained for this work. The schematic cross-section of the device is shown in Fig. 1. Deep trench combined with shallow trench isolation (STI) provides device isolation, while a buried subcollector layer and an n- epitaxial layer form the collector region along with the selectivelyimplanted collector (SIC) pedestal. A boron-doped SiGe:C base layer was grown by non-selective UHV/CVD and a boron-doped raised extrinsic base was formed self-aligned to in-situ phosphorus-doped emitter. Copper-based back-end of the line (BEOL) process completes the devices for interconnects and test pads. The total RB was reduced to improve fmax by reducing the polysilicon parasitic resistance component of the raised extrinsic base, denoted as RB_poly in Fig. 2, which is a close-up of the circled area in Fig. 1. This was achieved by reducing the spacing between the raised extrinsic base silicide and the emitter, shown as D in Fig. 2. In-situ Phosphorus-Doped Emitter Dielectric Isolation Silicide Raised Extrinsic Base Boron-Doped SiGe Base Shallow Trench Deep Trench Selectively Implanted Collector (SIC) Buried Subcollector Fig. 1. Schematic cross-section of SiGe HBT with raised extrinsic base. 0-7803-8684-1/04/$20.00 ©2004 IEEE 12 Spacer D AE = 0.12X2.5 µm2 IB from 0, step 3 µA 10 Emitter Silicide IC (mA) 8 RB_poly 6 4 Raised extrinsic base STI 2 SiGe base 0 0.0 Fig. 2. Schematic view of the circled area in Fig. 1 showing the spacing, D, between the raised extrinsic base silicide and the emitter. Typical DC characteristics are shown in Fig. 3 and Fig. 4 for devices with emitter size of AE=0.12×2.5 µm2. From the Gummel plots shown in Fig. 3, which exhibit low leakage current, the peak DC current gain is approximately 650 at VBE~0.8 V. From the common emitter forced-IB output characteristics, shown in Fig. 4, the open-base E-C breakdown voltage BVCEO is approximately 1.7 V, which results in fT·BVCEO product of 510 GHz·V, far exceeding the Johnson limit of 200 GHz·V [5]. Open-emitter B-C breakdown voltage BVCBO, which is more relevant in actual circuit designs [6], is approximately 5.6 V. B. RF Characteristics Figure 5 shows the overlay of RF characteristics curves for 3 devices with emitter size of AE=0.12×2.5 µm2 selected across the wafer. They exhibit peak fmax and fT of about 350 GHz and 300 GHz, respectively, at collector current IC~5.7 mA. 1.0E-1 2.5 AE = 0.12X2.5 µm2 350 600 1.0E-5 1.0E-6 400 1.0E-7 1.0E-8 200 1.0E-9 VCB = 0.5 V 300 fmax, fT (GHz) IC, IB (A) 2.0 400 800 1.0E-4 250 fmax 200 150 fT 100 50 1.0E-10 1.0E-11 0.4 1.5 VCE (V) The parameters were obtained from the extrapolation of unilateral power gain U and the current gain h21 at 40 GHz with -20 dB/dec roll-off. Variations in the extracted peak values of fmax and fT with the extrapolation frequency and device bias will be discussed later. Improvement in fmax compared to our prior work [3] is a result of reduced total RB, which was achieved through reduction of the parasitic component RB_poly as shown in Fig. 2. The resistance component of the un-silicided polysilicon portion of the raised extrinsic base is lowered by reducing the spacing, D, between the extrinsic base silicide and the emitter as illustrated in Fig. 2. We note that such reduction in the parasitic base resistance did not have significant impact on fT, which was previously reported [3], or the collector-base capacitance (CCB). Further improvement in fmax can be achieved through reduction of parasitic components of CCB. This indicates continuing performance improvements achievable in SiGe HBTs by reducing extrinsic parasitics. Selected device parameters are summarized in Table I. AE = 0.12X2.5 µm2 VCB = 0 V Curent Gain 1.0E-3 1.0 Fig. 4. The common emitter forced-IB output characteristics with IB step of 3 µA. AE=0.12×2.5 µm2. T=298 K. Device Characteristics A. DC Characteristics 1.0E-2 0.5 0.5 0.6 0.7 VBE (V) 0.8 0.9 0 1.0 Fig. 3. The Gummel characteristics and current gain measured at VCB=0V. AE=0.12× 2.5 µm2. T=298 K. 0 0 1 IC (mA) 10 100 Fig. 5. fmax and fT extrapolated from U and h21 at 40 GHz with -20 dB/dec slope. The curves were taken from 3 sites across the wafer. 0-7803-8684-1/04/$20.00 ©2004 IEEE Table I Selected device parameters of SiGe HBTs. AE=0.12×2.5 µm2. Parameter Peak fmax Peak fT IC @ peak fmax and fT Peak β BVCBO BVCEO BVEBO Value 350 GHz 300 GHz 5.7 mA 650 5.6 V 1.7 V 2.5 V The accuracy of the extracted values of fmax and fT were verified by careful examination of the raw data. Figure 6 shows U and h21, as well as MSG/MAG (max. stable gain / max. available gain), measured up to f =110 GHz. The gain rolls off with a slope of about -20 dB/dec near 40 GHz for all three gains as predicted by the single-pole approximation. This indicates that fmax and fT values extrapolated from frequencies around 40 GHz can be considered reliable. Figure 7 shows the extracted values of fmax and fT , for the 3 40 AE = 0.12X2.5 µm2 35 -20 dB/dec U Gain (dB) 30 MSG/MAG h21 25 20 15 0 fT=300 GHz 1 10 100 Frequency (GHz) 1000 Fig. 6. U, h21, and MSG/MAG measured up to 110 GHz shown along with -20 dB/dec lines. 450 425 fmax, fT (GHz) 400 375 350 AE = 0.12X2.5 µm2 VCB = 0.5 V fmax 325 300 fT 275 250 225 200 10 15 20 25 30 35 40 45 Extrapolation Frequency (GHz) Table II Gain values of U, MSG/MAG, and h21 at selected frequencies. Frequency (GHz) 20 30 40 50 60 70 80 90 100 U 24.2 21.1 18.7 15.6 13.7 12.6 12.6 11.0 10.7 Gain (dB) MSG/MAG 19.4 17.7 16.4 15.6 13.3 11.5 11.0 9.4 8.9 h21 23.3 20.1 17.4 15.5 14.2 13.5 12.9 12.3 12.0 C. Effect of Bias and Device Dimension Variations fmax=350 GHz 10 5 sites in Fig. 5, for extrapolation frequencies between 20-40 GHz. Clearly, the values of fmax and fT can be affected by the extrapolation frequency due to fluctuation in the raw data with fmax between 330-370 GHz and fT between 300-315 GHz. Based on the variations in the extracted values in Fig. 7, fmax and fT of these devices with AE=0.12×2.5 µm2 can be quoted conservatively as 350 GHz and 300 GHz, respectively. To avoid ambiguity over the extracted values of fmax and fT at a specific extrapolation frequency, the gain values at selected frequencies are listed in Table II as a measure for the device operation speed. The gain values at frequencies of interest indicate the suitability of this SiGe HBT technology for high frequency RF/analog and high data rate network applications. 50 Fig. 7. fmax and fT obtained from U and h21 with -20 dB/dec slope as a function of extrapolation frequency for the 3 site in Fig. 5. Sensitivity of fmax and fT to the collector-base reverse bias (VCB) is demonstrated in Fig. 8 for VCB=0 and 0.5 V. An optimal peak value for fmax is observed at VCB= 0.5 V, while a slight degradation of fT is observed at VCB=0 V. This behavior can be explained by the competing contributions from the reduced CCB and increased RB, due to increased C-B space charge region width at higher VCB. At VCB=0.5 V these two terms are balanced out resulting in the highest peak value for fmax. On the other hand, the large RB dominates at VCB=0 V causing fmax peak value to decrease [2]. The dependence of the device speed on the emitter width (WE) is shown in Fig. 9 for WE=0.12, 0.16, and 0.2 µm. An obvious difference is observed for fmax as expected, where the peak fmax value is achieved with reduced base resistance for narrower emitter width. This is a major advantage of lateral scaling in Si-based bipolar transistors. The peak fT value for WE=0.12 µm is about 300 GHz and is lower than the peak values for WE=0.16 and 0.2 µm, both for which fT is about 325 GHz. D. Ring Oscillator Gate Delay Figure 10 shows the gate delay for a CML ring oscillator with 56 stages and a load resistor of 79 Ω for devices with 0-7803-8684-1/04/$20.00 ©2004 IEEE 400 AE = 0.1X1.5 µm2 VCB = 0.5 V 350 3.5 300 fmax 250 Gate Delay (ps) fmax, fT (GHz) 3.6 VCB = 0.0 V AE = 0.12X2.5 µm2 fT 200 150 100 0 1 10 IC (mA) 100 0 1 10 IC (mA) 100 Fig. 8. Effect of VCB on fmax and fT. The highest peak value for fmax is observed at VCB=0.5 V. 400 fmax, fT (GHz) WE = 0.12 µm VCB = 0.5 V LE = 2.5 µm 350 3.3 WE = 0.20 µm fmax fT 200 3.1 2.5 3.26 ps 3.0 150 100 4.0 IC (mA) 4.5 5.0 5.5 Fig. 10. Gate delay versus collector (tail) current for CML ring oscillator. AE=0.1×1.5 µm2. T=298 K. 50 0 3.5 GHz for any Si-based transistor technology. DC characterization shows BVCEO=1.7 V, BVCBO=5.6 V, and peak current gain of 650. A gate delay below 3.3 ps was also achieved for a CML ring oscillator using this technology. The result presented herein demonstrates the capability for continued performance improvements in SiGe HBT technology through extrinsic parasitics reduction. WE = 0.16 µm 300 250 3.4 3.2 50 0 RLoad = 79 Ω VEE = -2.5 V Acknowledgments 0 1 10 IC (mA) 100 0 1 10 IC (mA) 100 Fig. 9. Effect of device lateral scaling on fmax and fT. A significant improvement is obtained for fmax with the emitter width reduction from 0.2 µm down to 0.12 µm. emitter size of AE=0.10×1.5 µm2 from 3 different sites. The ring oscillator was fabricated using a different mask set design with the same process conditions. However, measurement of the RF performance for devices with emitter width of 0.1 µm were not possible due to limited functionality of the RF test structures for the new mask set design. As can be seen from Fig. 10, a gate delay between 3.26-3.28 ps per stage was achieved at a tail current IC~4.2 mA with supply voltage VEE=-2.5 V. The improvement in the gate delay is believed to be due to reduced total RB and higher fmax.[7] This gate delay is lower than our previously reported result of 3.9 ps [7] and 9% improvement over recently reported result of 3.6 ps for SiGe HBT technology [8]. This result can also be compared to the recent result from III-V technology of 3.21 ps ECL gate delay using InP/InGaAs DHBT technology with fmax/fT of about 360/232 GHz.[9] Conclusion SiGe HBT technology with fmax of 350 GHz was developed through reduction of the parasitic component of RB. This fmax value is the highest reported with associated fT of at least 300 The authors would like to acknowledge partial support of this work by DARPA under SPAWAR contract number N66001-02-C-8014. The authors also would like to thank Joseph Kocis, David Rockwell, Michael Longstreet, Karyn Hurley, and Robert Groves for their support in device process and test. References [1] B. Jagannathan et al., “Self-aligned SiGe NPN transistors with 285 GHz fMAX and 207 GHz fT in a manufacturable technology”, IEEE Elect. Dev. Lett., Vol. 23, p. 258 (2002). [2] J.-S. Rieh et al., “SiGe HBTs with cut-off frequency of 350 GHz", IEDM Tech. Dig., p. 771 (2002). [3] J. -S. Rieh et al., “SiGe HBTs for millimeter-wave applications with simultaneously optimized fT and fMAX of 300 GHz", IEEE RFIC Symp. Dig. , p. 395 (2004). [4] K. Washio, “SiGe HBT and BiCMOS technologies”, IEDM Tech. Dig., p. 113 (2003). [5] E. O. Johnson, “Physical limitations on frequency and power parameters of transistors,” RCA Rev., Vol. 26, p. 163 (1965). [6] G. Freeman et al., “Reliability and performance scaling of very high speed SiGe HBTs” Mircroelectronics Reliability, Vol. 44, p. 397 (2004). [7] B. Jagannathan et al., “3.9 ps SiGe HBT ECL ring oscillator and transistor design for minimum gate delay”, IEEE Elect. Dev. Lett., Vol. 24, p. 324 (2003). [8] H. Rücker et al., “SiGe:C BiCMOS technology with 3.6 ps gate delay,” IEDM Tech. Dig., p. 121 (2003). [9] K. Ishii et al, “3.21 ps ECL gate using InP/In/GaAs DHBT technology”, Electronics Lett., Vol. 39, p. 1434 (2003). 0-7803-8684-1/04/$20.00 ©2004 IEEE