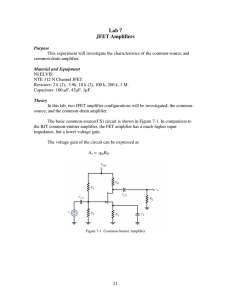

JFET Common-Drain Amplifier

advertisement

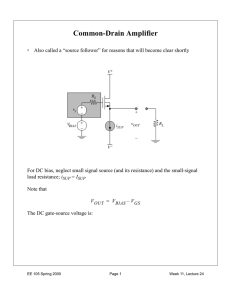

OTHER JFET AMPLIFIER CONFIGURATIONS

ü

OTHER JFET AMPLIFIER CONFIGURATIONS

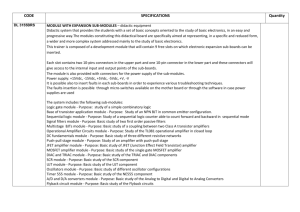

CONFIGURATIONS

Common - Source

Zin

High

Zout

Medium

Av o

Medium

Common - Gate HHigh frequency applicationsL

High

Low

~1

Very Low

High

Medium

Common - Drain HSource - FollowerL

ü

COMMON-DRAIN ( SOURCE-FOLLOWER ) JFET AMPLIFIER

Figure 1. Common-Drain (Source-Follower) SSAC JFET Amplifier

Note that RD is not needed and should be eliminated from the JFET circuit when operating in the common-drain configur

Univ. of Southern Maine

1

ELE343 Electronics 1999/20

JFET Common-Drain Amplifier-v03.nb

Prof. M.G. Guven

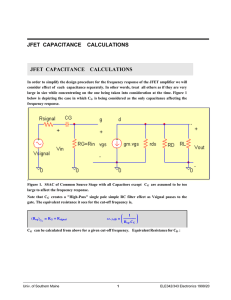

Figure 2. SSAC Equivalent Circuit for the Source-Follower

Note that RD is not needed and should be eliminated from the JFET circuit when operating in the common-drain

ü

INPUT IMPEDANCE OF COMMON-DRAIN AMPLIFIER

Rin = RG

HBy inspection of the SSAC equivalentL

Comment: In principle RG can be chosen as large as one wants. However, finite leakage current of the biased g

chosen RG . Practical values limit RG at 10 MW level for room temperature operation. For high temperature op

JFET junction leakage currents getting very close to base-emitter forward bias current of a BJT.

Univ. of Southern Maine

2

ELE343 Electronics 1999/20

JFET Common-Drain Amplifier-v03.nb

ü

Prof. M.G. Guven

VOLTAGE GAIN OF COMMON-DRAIN AMPLIFIER

Figure 3.

gm.DvGS = gm Hvin - vout L

vout = gm Hvin - vout L Hrds ˛ RS ˛ RL L

vout @1 + gm Hrds ˛ RS ˛ RL LD = gm vin Hrds ˛ RS ˛ RL LD

vout

gm Hrds ˛ RS ˛ RL L

Av = ÄÄÄÄÄÄÄÄÄÄÄÄÄ = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

vin

1 + gm Hrds ˛ RS ˛ RL L

1

ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ b 1 Unity Gain

Av = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

1

ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

ÄÄÄÄÄÄ

1 + ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

g H r ˛R ˛R L

m

Since,

ds

S

L

1

rds , RS , RL are typically >> ÄÄÄÄ

ÄÄÄÄ

g

m

Av is close to unity.

1

Note that RL does not change the unity gain significantly unless RL becomes as low as ÄÄÄÄ

ÄÄÄÄ .

g

m

1

This predicts Rout of the circuit to be in the order of ÄÄÄÄ

ÄÄÄÄ and, therefore, low.

g

m

Proof follows:

Univ. of Southern Maine

3

ELE343 Electronics 1999/20

JFET Common-Drain Amplifier-v03.nb

ü

Prof. M.G. Guven

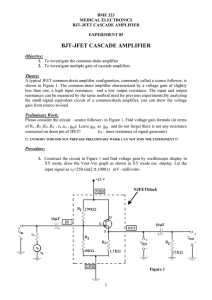

OUTPUT IMPEDANCE OF COMMON-DRAIN AMPLIFIER

Figure 4. Vtest -Itest method applies to determine Rout of Common-Drain JFET stage.

Using Vtest - Itest ,

vg = 0 and vs = Vtest

if RL excluded.

Vtest

1

Rout = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄ = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

1

Itest

I ÄÄÄÄÄÄÄÄ

ÄÄÄÄÄÄÄÄÄ M + gm

r ˛R

1

ij

y

j ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ zz << gm

k rds ˛ Rs {

ds

Typically

s

therefore

1

Rout > ÄÄÄÄÄÄÄÄÄÄ

gm

From the design example,

gm = 1 mS

at

IDQ > 0.41 mA , therefore,

Rout ª 1 KW

Therefore, if we use the same bias except for common-drain rather than common-source Rout = 1KW . Note that,

BJT counterpart , the common-collector. For the common-collector stage,

kT ê q

Rout > ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

ICQ

which yields about 63 ohms, more than an order of magnitude smaller than the common-drain for the same bias c

In conclusion, if low output impedance is of prime concern a BJT common-collector (emitter-follower) should be

Univ. of Southern Maine

4

ELE343 Electronics 1999/20