Common-Drain Amplifier

advertisement

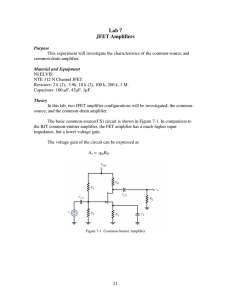

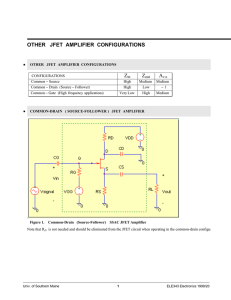

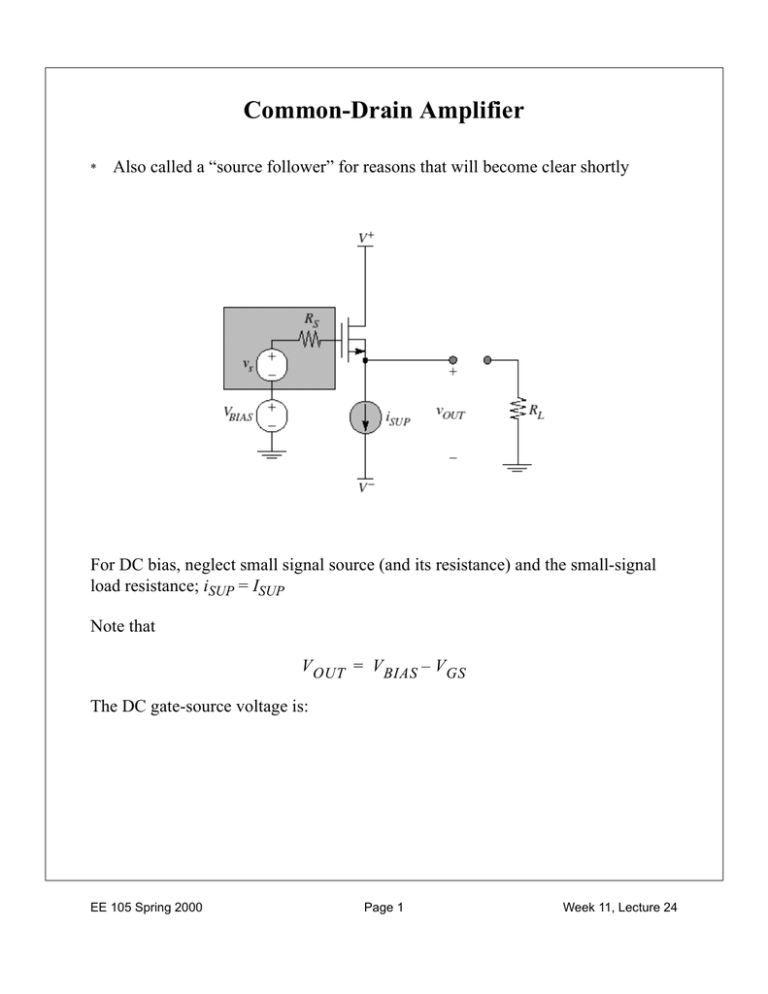

Common-Drain Amplifier * Also called a “source follower” for reasons that will become clear shortly For DC bias, neglect small signal source (and its resistance) and the small-signal load resistance; iSUP = ISUP Note that V OUT = V BIAS – V GS The DC gate-source voltage is: EE 105 Spring 2000 Page 1 Week 11, Lecture 24 DC Transfer Curve p-well CMOS process means that the source and bulk can be shorted ... not true for an n-well process. The threshold voltage VTn is not a constant, since the source-bulk voltage VSB increases as VOUT increases: V Tn = V TOn + γ n EE 105 Spring 2000 - ( V OUT – V ) – 2φ p – 2φ p Page 2 Week 11, Lecture 24 DC Transfer Curve for Common-Drain Amps VOUT VBIAS Simple idea: slope of transfer curve is the voltage gain ... about 1 The common-drain is a voltage buffer dv OUT A v = ----------------- ≈ 1 dv BIAS EE 105 Spring 2000 Page 3 Week 11, Lecture 24 Common-Drain Open-Circuit Voltage Gain For finding Av exactly, remove the source and its resistance and the load resistance ... apply a test voltage and find the output voltage KCL at source node: v out ---------------- – g ( v – v ) – ( – g mb v out ) = 0 r oc r o m t out 1 v out ----------------- + g m + g mb = g m v t r oc r o gm gm v out -----------------------------------------------------------------------A v = ---------- = ≈ g + g vt 1 m mb g m + g mb + ----------------- r oc r o EE 105 Spring 2000 Page 4 Week 11, Lecture 24 Output Resistance of Common-Drain Amplifier * Leave the source resistance attached while exercising the output with a test voltage KCL at the source node ... remove ro || roc and put it back in i t + g m ( 0 – v t ) + ( – g mb v t ) = 0 v t 1 1 R out = ( r o r oc ) ---- = ( r o r oc ) ----------------------- = --------------------------------------------------------------g + g [ 1 ⁄ ( r o r oc ) ] + g m + g mb it m mb Typically, ro || roc >> gm + gmb 1 R out ≅ ----------------------g m + g mb EE 105 Spring 2000 Page 5 Week 11, Lecture 24 Common-Drain Small-Signal Model Input resistance is infinite: open-circuit from gate-source If source and bulk can be shorted (possible for a MOSFET in a well), then the gate is essentially 1 (since backgate generator has zero vsb controlling it.) Output resistance is ideally zero for a voltage-output amplifier: typical values gm = 500 µS gmb = 50 µS 1 R out = ----------------------- ≈ 2 kΩ g m + g mb The output resistance can be reduced by increasing the transconductance ... (W/L) can be made huge in order to drive Rout toward zero. EE 105 Spring 2000 Page 6 Week 11, Lecture 24 Summary of MOSFET Two-Port Models EE 105 Spring 2000 Page 7 Week 11, Lecture 24 Assessment of MOS Amplifiers Common-source is the only stage that provides gain Common-gate can buffer a poor current source into a nearly ideal one Common-drain can buffer a poor voltage source into a nearly ideal one We need more than one stage to approach an ideal amplifier (of any of the 4 types) EE 105 Spring 2000 Page 8 Week 11, Lecture 24