Chapter 5

advertisement

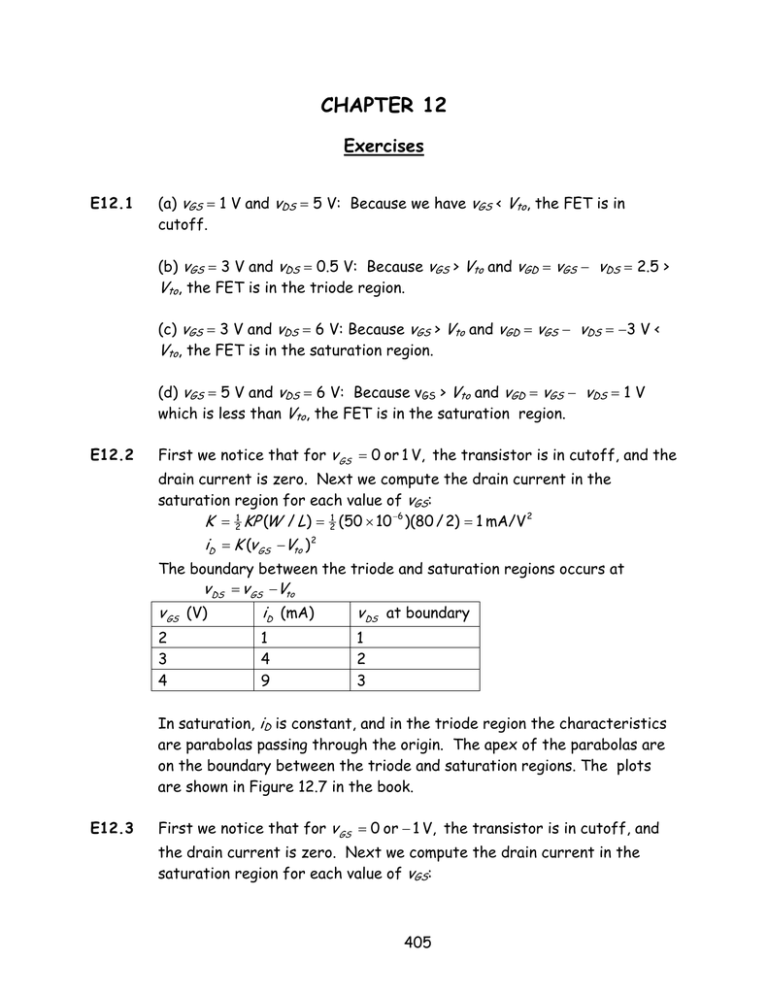

CHAPTER 12 Exercises E12.1 (a) vGS = 1 V and vDS = 5 V: Because we have vGS < Vto, the FET is in cutoff. (b) vGS = 3 V and vDS = 0.5 V: Because vGS > Vto and vGD = vGS − vDS = 2.5 > Vto, the FET is in the triode region. (c) vGS = 3 V and vDS = 6 V: Because vGS > Vto and vGD = vGS − vDS = −3 V < Vto, the FET is in the saturation region. (d) vGS = 5 V and vDS = 6 V: Because vGS > Vto and vGD = vGS − vDS = 1 V which is less than Vto, the FET is in the saturation region. E12.2 First we notice that for v GS = 0 or 1 V, the transistor is in cutoff, and the drain current is zero. Next we compute the drain current in the saturation region for each value of vGS: K = 21 KP (W / L) = 21 (50 × 10 −6 )(80 / 2) = 1 mA/V 2 iD = K (v GS −Vto ) 2 The boundary between the triode and saturation regions occurs at v DS = v GS −Vto v GS (V) iD (mA) v DS at boundary 2 3 4 1 4 9 1 2 3 In saturation, iD is constant, and in the triode region the characteristics are parabolas passing through the origin. The apex of the parabolas are on the boundary between the triode and saturation regions. The plots are shown in Figure 12.7 in the book. E12.3 First we notice that for v GS = 0 or − 1 V, the transistor is in cutoff, and the drain current is zero. Next we compute the drain current in the saturation region for each value of vGS: 405 K = 21 KP (W / L) = 21 (25 × 10 −6 )(200 / 2) = 1.25 mA/V 2 iD = K (v GS −Vto ) 2 The boundary between the triode and saturation regions occurs at v DS = v GS −Vto . v GS (V) iD (mA) v DS at boundary −2 −3 −4 1.25 5 11.25 −1 −2 −3 In saturation, iD is constant, and in the triode region the characteristics are parabolas passing through the origin. The apex of the parabolas are on the boundary between the triode and saturation regions. The plots are shown in Figure 12.9 in the book. E12.4 We have v GS (t ) = v in (t ) +VGG = sin(2000πt ) + 3 Thus we have VGS max = 4 V, VGSQ = 3 V, and VGS min = 2 V. The characteristics and the load line are: 406 For vin = +1 we have vGS = 4 and the instantaneous operating point is A. Similarly for vin = −1 we have vGS = 2 V and the instantaneous operating point is at B. We find VDSQ ≅ 11 V, VDS min ≅ 6 V, VDS max ≅ 14 V. E12.5 First, we compute VG = VDD R2 = 7V R1 + R2 1 and K = 2 KP (W / L) = 21 (50 × 10 −6 )(200 / 10) = 0.5 mA/V 2 As in Example 12.2, we need to solve: V 1 2 2 VGSQ + − 2Vto VGSQ + (Vto ) − G = 0 RS K RS K Substituting values, we have 2 VGSQ −VGSQ − 6 = 0 The roots are VGSQ = −2 V and 3 V. The correct root is VGSQ = 3 V which yields IDQ = K(VGSQ − Vto)2 = 2 mA. Finally, we have VDSQ = VDD − RSIDQ = 16 V. E12.6 First, we replace the gate bias circuit with its equivalent circuit: Then we can write the following equations: K = 21 KP (W / L) = 21 (25 × 10 −6 )(400 / 10) = 0.5 mA/V 2 VGG = 11.5 =VGSQ − Rs I DQ + 20 (1) 407 I DQ = K (VGSQ −Vto ) 2 (2) Using Equation (2) to substitute into Equation (1), substituting values, and 2 − 16 = 0 . The roots of this equation are rearranging, we have VGSQ VGSQ = ±4 V. However VGSQ = −4 V is the correct root for a PMOS transistor. Thus we have I DQ = 4.5 mA and E12.7 VDSQ = Rs I DQ + RD I DQ − 20 = −11 V. From Figure 12.21 at an operating point defined by VGSQ = 2.5 V and VDSQ = 6 V, we estimate gm = 1 rd = ∆iD (4.4 − 1.1) mA = 3.3 mS = ∆v GS 1V ∆iD (2.9 − 2.3) mA = 0.05 × 10 − 3 ≅ (14 - 2) V ∆v GS Taking the reciprocal, we find rd = 20 kΩ. 408 E12.8 E12.9 gm = RL′ = ∂iD ∂v GS = Q − po int ∂ ∂v GS 1 1 rd + 1 RD + 1 RL ( K (v GS −Vto )2 = 2K V GSQ −Vto ) Q − po int = RD = 4.7 kΩ Avoc = − gm RL′ = −(1.77 mS) × (4.7 kΩ ) = −8.32 E12.10 For simplicity we treat rd as an open circuit and let RL′ = RD RL. v in = v gs + Rs gmv gs v o = −RL′ gmv gs Av = E12.11 RL′ = RD RL = 3.197 kΩ Av = E12.12 − RL′ gm vo = v in 1 + RL′ gm − RL′ gm vo − (3.197 kΩ )(1.77 mS) = = = −0.979 1 + (2.7 kΩ )(1.77 mS) v in 1 + RL′ gm The equivalent circuit is shown in Figure 12.28 in the book from which we can write 409 v in = 0 v gs = −v x ix = Solving, we have Ro = E12.13 vx vx v v + − gmv gs = x + x + gmv x RS rd RS rd vx 1 = 1 1 ix gm + + RS rd Refer to the small-signal equivalent circuit shown in Figure 12.30 in the book. Let RL′ = RD RL . v in = −v gs v o = −RL′ gmv gs Av = v o v in = RL′ gm iin = v in Rs − gmv gs = v in Rs + gmv in Rin = v in 1 = iin gm + 1 Rs If we set v (t) = 0, then we have vgs = 0. Removing the load and looking back into the amplifier, we see the resistance RD. Thus we have Ro = RD . E12.14 See Figure 12.34 in the book. E12.15 See Figure 12.35 in the book. Problems P12.1 See Figures 12.1 and 12.2 in the book. P12.2 Cutoff: Triode: iD = 0 for vGS ≤ Vto iD = K[2(vGS − Vto)vDS − vDS2] for vDS ≤ vGS − Vto (or vGD ≥ Vto) and vGS ≥ Vto Saturation: iD = K(vGS − Vto)2 for vGS ≥ Vto and vDS ≥ vGS − Vto (or vGD ≤ Vto) 410 P12.3* K = 21 KP (W / L) = 0.25 mA/V 2 (a) Saturation because we have vGS ≥ Vto and vDS ≥ vGS − Vto. iD = K(vGS − Vto)2 = 2.25 mA (b) Triode because we have vDS < vGS − Vto and vGS ≥ Vto. iD = K[2(vGS − Vto)vDS − vDS2] = 2 mA (c) Cutoff because we have vGS ≤ Vto. iD = 0. P12.4* iD vGS = 4 3V 2V vDS P12.5 The device is in saturation for vDS ≥ vGS − Vto = 3 V. The device is in the triode region for vDS ≤ 3 V. In the saturation region, we have iD = K(vGS − Vto)2 = 0.1(vGS − 1)2 for vGS ≥ 1 In the pinchoff region, we have iD = 0 for vGS ≤ 1 The plot of iD versus vGS in the saturation region is: 411 P12.6 (a) Saturation because we have vGS ≥ Vto and vDS ≥ vGS − Vto. (b) Triode because we have vGS ≥ Vto and vDS ≤ vGS − Vto. (c) Saturation because we have vGS ≥ Vto and vDS ≥ vGS − Vto. (d) Cutoff because we have vGS ≤ Vto. P12.7 With the gate connected to the drain, we havevDS = vGS so vDS ≥ vGS − Vto. Then, if vGS is greater than the threshold voltage, the device is operating in the saturation region. If vGS is less than the threshold voltage, the device is operating in the cutoff region. P12.8 For the NMOS enhancement transistors, we have Vto = +1 V. For the PMOS enhancement transistors, we have Vto = −1 V. (a) This NMOS transistor is operating in saturation because we have vGS ≥ Vto and vDS ≥ vGS − Vto. Thus, Ia = K(vGS − Vto)2 = 0.9 mA. (b) This PMOS transistor is operating in saturation because we have vGS ≤ Vto and vDS = −4 ≤ vGS − Vto = −3 −(−1) = −2. Thus, Ib = K(vGS − Vto)2 = 0.4 mA. (c) This PMOS transistor is operating in the triode region because we have vGS ≤ Vto and vDS = −1 ≥ vGS − Vto = −5 −(−1) = −4. Thus, Ic = K[2(vGS − Vto)vDS − vDS2] = 0.7 mA. (d) This NMOS transistor is operating in the triode region because we have vGS ≥ Vto and vDS = 1 ≤ vGS − Vto = 3 − 1 = 2. Thus, Id = K[2(vGS − Vto)vDS − vDS2] = 0.3 mA. P12.9 With vGS = vDS = 5 V, the transistor operates in the saturation region for which we have iD = K(vGS − Vto)2. Solving for K and substituting values we obtain K = 125 µA/V2. However we have K = (W/L)(KP/2). Solving for W/L and substituting values we obtain W/L = 5. Thus for L = 2 µm, we need W = 10 µm. P12.10 To obtain the least drain current choose minimumW and maximum L (i.e., W1 = 0.25 µm and L1 = 2 µm). To obtain the greatest drain current choose maximumW and minimum L (i.e., W2 = 2 µm and L2 = 0.25 µm). The ratio between the greatest and least drain current is (W2/L2)/(W1/L1) = 64. P12.11* In the saturation region, we have iD = K(vGS − Vto)2. Substituting values, we obtain two equations: 412 0.2 mA = K(2 − Vto)2 1.8 mA = K(3 − Vto)2 Dividing each side of the second equation by the respective side of the first, we obtain (3 −Vto )2 9= (2 −Vto )2 Solving we determine that Vto = 1.5 V. (We disregard the other root, which is Vto = 2.25 V, because the transistor would then be in cutoff with vDS = 2 V and would not give a current of 0.2 mA as required.) Then, using either of the two equations, we find K = 0.8 mA/V2. P12.12 For a device operating in the triode region, we have iD = K[2(vGS − Vto)vDS − vDS2] Assuming that vDS << vGS − Vto this becomes iD ≅ K2(vGS − Vto)vDS Then, the resistance between drain and source is given by 1 rd = v DS / iD = K 2(v GS −Vto ) With the device in cutoff (i.e., vGS ≤ Vto), the drain current is zero and rd is infinite. Evaluating, we have: vGS (V) rd (kΩ) 0.5 1.0 1.5 2.0 P12.13 ∞ 10 5 3.33 (a) This is an NMOS transistor. We have vGS = Vin and vDS = 5 V. With Vin = 0, the transistor operates in cutoff and Ia = iD = 0. With Vin = 5, the transistor operates in satruation and Ia = iD = K(vGS − Vto)2 = 3.2 mA. (b) This is a PMOS transistor. We have vGS = Vin − 5 and vDS = −5 V. 413 With Vin = 0, the transistor operates in satruation and Ib = iD = K(vGS − Vto)2 = 3.2 mA. With Vin = 5, the transistor operates in cutoff and Ib = iD = 0. P12.14 Because vGD = 3 − 5 = −2 V is less than Vto, the transistor is operating in saturation. Thus, we have iD = K(vGS − Vto)2. Substituting values gives 0.5 = 0.5(vGS − 1)2 which yields two roots: vGS = 2 and vGS = 0 V. However, the second root is extraneous, so we have vGS = 2 = 3 − 0.0005R which yields R = 2000 Ω. P12.15* We have iD = K (v GS −Vto ) 2 . Substituting values and solving, we obtain v GS = −2.5 and v GS = 1.5 V. However, if v GS = 1.5 , the PMOS transistor is operating in cutoff. Thus, the correct answer is v GS = −2.5 V. P12.16 Distortion occurs in FET amplifiers because of curvature and nonuniform spacing of the characteristic curves. P12.17* The load-line equation is VDD = RDiD + vDS, and the plots are: Notice that the load line rotates around the point (VDD, 0) as the resistance changes. P12.18 The load-line equation is VDD = RDiD + vDS, and the plots are: 414 Notice that the load lines are parallel as long as RD is constant. P12.19* For VGG = 0, the FET remains in cutoff so VDSmax = VDSQ =VDSmin = 20 V. Thus, the output signal is zero, and the gain is zero. For amplification to take place, the FET must be biased in the saturation or triode regions. P12.20 (a) The 1.7 MΩ and 300 kΩ resistors act as a voltage divider that establishes a dc voltage VGSQ = 3 V. Then if the capacitor is treated as a short for the ac signal, we have vGS(t) = 3 + sin(2000πt) (b), (c), and (d) iD vGS = 4 V 3V 2V vDS From the load line we find VDSQ = 16 V, VDSmax = 19 V, and VDSmin = 11 V. P12.21* For vin = +1 V we have vGS = 4 V. For the FET to remain in saturation, we 415 must have VDSmin ≥ 3 V at which point the drain current is 4.5 mA. Thus, the maximum value of RD is RDmax = (20 − 3)/4.5 mA = 3.778 kΩ. P12.22 The Thévenin equivalent for the drain circuit contains a 12-V source in series with a 1.2-kΩ resistance. Then, we can construct the load line and determine the required voltages as shown: P12.23 The KVL equation around the loop consisting of the VDD source, the nonlinear element, and the drain/source is VDD = 20 = 0.1iD2 + v DS The load line in this case is a parabola with its apex at iD = 0, vDS = 20 V as shown: 416 P12.24 Using KVL, we have v GS (t ) = sin(2000πt ) + 7 − 10 = −3 + sin(2000πt ) Thus, the maximum value of vGS is −2 V, the Q-point value is −3 V, and the minimum value is −4 V. Applying KVL again, we obtain the load-line equation: − 10 = v DS − iD in which the current is in mA. The load line is: From the load line, we determine that the maximum value of vDS is approximately −1.6 V, the Q-point is −5.5 V, and the minimum value is −8.8 V. The corresponding output voltages are 8.4 V, 4.5 V, and 1.2 V. P12.25 We are given vDS(t) = VDC + V1msin(2000πt) + V2mcos(4000πt) Evaluating at t = 0.25 ms and observing that the plot gives vDS = 4 V at that instant we have 4 = VDC + V1m − V2m Similarly at t = 0 we have 11 = VDC + V2m and at t = 0.75 ms we have 16 = VDC − V1m − V2m Solving the previous three equations we have VDC = 10.5 V, V2m = 0.5 V and V1m = −6 V. Thus the percentage second−harmonic distortion is V2m/V1m × 100% = 8.33%. Thus this amplifier has a very large amount of distortion compared to that of a high quality amplifier. 417 P12.26 In an amplifier circuit, we need to bias the MOSFET so the ac signal to be amplified can cause changes in the currents and voltages resulting in an amplified signal. If the signal peak amplitude was smaller than 1 V, the transistor had Vto = 1 V, and we biased the transistor at VGSQ = 0, the transistor would remain in cutoff, iD(t) would be zero for all t, and the signal would not be amplified. P12.27* For this circuit, we can write VGSQ = 15 − IDQRS Assuming operation in saturation, we have IDQ = K(VGSQ − Vto)2 using the first equation to substitute into the second equation, we have IDQ = K(15 − IDQRS − Vto)2 = 0.25(14 − 3IDQ)2 where we have assumed that IDQ is in mA. Rearranging and substituting values, we have 2 I DQ − 9.777IDQ + 21.777 = 0 The correct root is the smaller one which is IDQ = 3.432 mA. Then we have VDSQ = 30 − RDIDQ − RSIDQ = 16.27 V. P12.28* We can write VDD = VDSQ + RS I DQ . Substituting values and solving, we obtain RS = 3 kΩ. Next we have K = 21 KP (W / L) = 2 mA/V 2 . Assuming that the NMOS operates in saturation, we have I DQ = K (VGSQ −Vto ) 2 Substituting values and solving, we find VGSQ = 0 V and VGSQ = 2 V. The correct root is VGSQ = 2 V. (As a check we see that the device does operate in saturation because we have VDSQ greater than VGSQ −Vto . ) Then we have VG = VGSQ + RS I DQ = 8 V. However we also have VG = VDD R2 R1 + R2 Substituting values and solving, we obtain R2 = 2 MΩ. 418 P12.29* We can write VDD = 20 = 2I DQ + 8 + 2 in which IDQ is in mA. Solving, we obtain IDQ = 5 mA. Then, we find Rs = 2 / I DQ = 400 Ω. Next, we have K = 21 KP (W / L) = 0.75 mA/V 2 . Assuming that the NMOS operates in saturation, we have I DQ = K (VGSQ −Vto ) 2 Substituting values and solving we find VGSQ = −1.582 V and VGSQ = 3.582 V. The correct root is VGSQ = 3.582 V. (As a check, we see that the device does operate in saturation because we have VDSQ = 8 V, which is greater than VGSQ −Vto . ) Then, we have VG = VGSQ + 2 = 5.582 V. However, we also have VG = VDD R2 R1 + R2 Substituting values and solving, we obtain R1 = 2.583MΩ. P12.30 First, we use Equation 12.11 to compute VG = VDD R2 R1 + R2 = 5V As in Example 12.2, we need to solve: V 1 2 2 + − 2Vto VGSQ + (Vto ) − G = 0 VGSQ RS K RS K Substituting values, we have 2 VGSQ − 1.1489VGSQ − 3.2553 = 0 The roots are VGSQ = 2.4679 V and −1.319 V. The correct root is VGSQ = 2.4679 V which yields IDQ = K(VGSQ − Vto)2 = 0.5387 mA. Finally, we have VDSQ = VDD − RDIDQ − RSIDQ = 9.936 V. P12.31 Assuming that the MOSFET is in saturation, we have VGSQ = 10 − IDQ IDQ = K(VGSQ − Vto)2 419 where we have assumed that IDQ and K are in mA and mA/V2 respectively. (a) Using the second equation to substitute in the first, substituting values and rearranging, we have VGSQ2 − 7VGSQ + 6 = 0 which yields VGSQ = 6 V. (The other root, VGSQ = 1 V, is extraneous.) IDQ = 4 mA VDSQ = 20 − 2IDQ = 12 V (b) Similarly for the second set of values, we have VGSQ2 − 3.5VGSQ − 1 = 0 VGSQ = 3.765 V IDQ = 6.234 mA VDSQ = 20 − 2IDQ = 7.53 V P12.32 We can write VDD = RD I DQ +VDSQ + RS I DQ . Substituting values and solving we obtain RS = 3 kΩ. Next we have K = 21 KP (W / L) = 0.2 mA/V 2 . Assuming that the NMOS operates in saturation, we have I DQ = K (VGSQ −Vto ) 2 Substituting values and solving we find VGSQ = −1.236 V and VGSQ = 3.236 V. The correct root is VGSQ = 3.236 V. (As a check we see that the device does operate in saturation because we have VDSQ greater than VGSQ −Vto . ) Then we have VG = VGSQ + Rs iD = 6.236 V. However we also have R2 VG = VDD R1 + R2 Substituting values and solving, we obtain R2 = 1.082 MΩ. P12.33 We have VG = VGSQ = 10R2/(R1 + R2) = 2.5 V. Then we have IDQ = K(VGSQ − Vto)2 = 0.5625 mA. VDSQ = VDD − RDIDQ = 4.375 V. 420 P12.34* We have VGSQ = VDSQ = VDD − RDIDQ. Then substituting IDQ = K(VGSQ − Vto)2, we have VGSQ = VDD − RDK(VGSQ − Vto)2 Substituting values and rearranging, we have VGSQ2 + 2VGSQ − 39 = 0 Solving we determine that VGSQ = 5.325 V and then we have IDQ = K(VGSQ − Vto)2 = 4.675 mA. P12.35 Beause vGD1 is zero, the first transistor operates in saturation. We have K 1 = 21 KP (W1 / L1 ) = 50 µA/V 2 . Then, we have iD 1 = K 1 (VGSQ −Vto )2 Substituting values and solving, we find VGSQ = −1.5 V and VGSQ = 2.5 V. The correct root is VGSQ = 2.5 V. Then, the resistance is R = 5 −VGSQ iD 1 = 2.5 = 12.5 kΩ 0.2 The second transistor has K 2 = 21 KP (W2 / L2 ) = 100 µA/V 2 and iD 2 = K 2 (VGSQ −Vto )2 = 0.4 mA. Provided that Vx is larger than 2 V, the second transistor operates in saturation, iD2 is constant, and the transistor is equivalent to an ideal 0.4mA current source. P12.36 P12.37 See Figure 12.20 in the book. gm = ∂iD ∂v GS 1 rd = Q − point ∂iD ∂v DS Q − point P12.38 For constant drain current in the saturation region, we have rd = ∞. P12.39 For VDSQ = 0, the vertical spacing of the drain characteristics is zero. Therefore gm = 0 at this operating point. Then the small-signal equivalent circuit consists only of rd. FETs are used as electronically controllable resistances at this operating point. 421 P12.40* In the triode region, we have iD = K[2(vGS − Vto)vDS − vDS2] gm = ∂iD ∂v GS = 2Kv DS Q − point Q − point = 2KVDSQ P12.41* In the triode region, we have iD = K[2(vGS − Vto)vDS − vDS2] 1 rd = ∂iD ∂v DS rd = P12.42 Q − point 2K (VGSQ = 2K (v GS −Vto − v DS ) Q − point 1 −Vto −VDSQ ) From Figure P12.42 at an operating point defined by VGSQ = 2.5 V and VDSQ = 6 V, we have gm = ∆iD (6.4 − 1.5) mA = 4.9 mS = 1V ∆v GS 1 rd = ∆iD (4.0 − 3.1) mA = 0.225 × 10 −3 ≅ (8 - 4 ) V ∆v DS Taking the reciprocal, we find rd = 4.44 kΩ. P12.43 gm = ∂iD ∂v GS 1 rd = 2 = 9v GS Q −point ∂iD ∂v DS Q −point Q −point = 9 mS = 0.1 Q −point = 0.1 mS rd = 10 kΩ P12.44 gm = ∂iD ∂v GS Q −point = 3 exp(v GS ) Q −point = 3 exp(1) = 8.155 mS 422 1 rd = ∂iD ∂v DS = 0.02v DS Q −point Q −point = 0.2 mS rd = 5 kΩ P12.45 We will sketch the characteristics for vGS ranging a few tenths of a volt on either side of the Q point. gm determines the spacing between the charactersistic curves. For gm = 2 mS, the curves move upward by 0.2 mA for each 0.1 V increase in vGS. Also, we will sketch the characteristics for vDS ranging a few volts on either side of the Q point. rd determines the slope of the charactersistic curves. For rd = 5 kΩ, the curves slope upward by 0.2 mA for each 1 V increase in vDS. The sketch of the curves is: P12.46 This transistor is operating with constant vDS. Thus, we can determine gm by dividing the peak ac drain current by the peak ac gate-to-source voltage. ∆iD 0.1 mA gm = = = 0.5 mS ∆v GS v =V 0.2 V DS DSQ The Q-point is VDSQ = 4 V, VGSQ = 1 V, and I DQ = 2 mA. P12.47 This transistor is operating with constantvGS. Thus, we can determine rd by dividing the peak ac drain-to-source voltage by the peak ac drain 423 current. rd = ∆v DS ∆iD = vGS =VGSQ 2 V = 200 kΩ 0.01 mA The Q-point is VDSQ = 5 V, VGSQ = 2 V, and I DQ = 3 mA. P12.48 Coupling capacitors act as open circuits for dc and as approximate short circuits for the ac signals to be amplified. Coupling capacitors are used in discrete circuits to isolate the various stages for dc so the bias points of the various stages can be determined independently while connecting the ac signal. The output coupling capacitor prevents dc current from flowing through the load and causes the ac signal to appear across the load. Furthermore, the input coupling capacitor connects the ac signal and prevents the dc component of the source from affecting the bias point of the input stage. Coupling capacitors are replaced by short circuits in midband small-signal equivalent circuits. They cause the gain of an amplifier to decline as the signal frequency becomes small. P12.49 See Figure 12.22 in the book. P12.50* (a) VG = VDD R2 R1 + R2 = 20 0. 3 = 3V 1.7 + 0.3 VGSQ = VG = 3 V K = 21 KP (W / L) = 2.5 mA/V 2 IDQ = K (VGSQ −Vto )2 = 10 mA VDSQ = VDD − RD I DSQ = 10 V gm = 2 KI DQ = 0.01 S (b) RL′ = 1 = 500 Ω 1 / RD + 1 / RL Av = − gm RL′ = −5 1 = 255 kΩ 1 / R1 + 1 / R2 Ro = RD = 1 kΩ Rin = 424 P12.51 (a) VG = VDD R2 R1 + R2 = 20 0. 3 = 3V 1.7 + 0.3 VGSQ = VG = 3 V K = 21 KP (W / L) = 0.75 mA/V 2 I DQ = K (VGSQ −Vto )2 = 0.75 mA VDSQ =VDD − RD I DSQ = 19.25 V gm = 2 KIDQ = 0.0015 S (b) 1 = 500 Ω 1 / RD + 1 / RL Av = − gm RL′ = −0.75 1 Rin = = 255 kΩ 1 / R1 + 1 / R2 Ro = RD = 1 kΩ RL′ = Notice that the gain of the circuit can change a great deal as the parameters of the FET change. P12.52 (a) (b) v o = RL′ (iin − gmv in ) iin = (v in − v o ) Rf v o RL′ − gm RL′Rf = v in RL′ + Rf R v Rin = in = f iin 1 − Av Av = The circuit used to determine output impedance is: 425 We define RD′ = RD (R + Rf ) . Then we can write vgs = vx Ro = R R + Rf and ix = vx + gmvgs RD′ vx 1 = g R 1 ix + m ′ Rf + R RD (c) The dc circuit is: IDQ = K(VDSQ − Vto)2 VGSQ = VDSQ IDQ = (VDD − VDSQ)/RD Using the above equations, we obtain 2 3VDSQ − 29VDSQ + 55 = 0 VDSQ = 7.08 V and IDQ = 4.31 mA gm = ∂iD ∂v GS ( ) = 2K VGSQ −Vto = 4.16 × 10 −3 S Q −point 426 (d) RL′ = RD RL = 2.31 kΩ Av = − 9.37 Rin = 9.64 kΩ Ro = 414 Ω (e) vo(t) = v(t) × R in × A = −0.164sin(2000πt) v R + R in (f) This is an inverting amplifier that has a very low input impedance compared to many other FET amplifiers. P12.53* Referring to the circuit shown in Figure P12.53, we have VGSQ = VDSQ IDQ = K(VGSQ − Vto)2 IDQ = (VDD − VDSQ)/RD From the previous three equations we obtain: 2 1.1VDSQ − 5.6VDSQ − 10.1 = 0 VDSQ = 6.50 V and IDQ = 6.135 mA gm = Ro = ∂iD ∂v GS ( ) = 2K VGSQ −Vto = 3.5 mS Q − point vx vx 1 = = = 253 Ω ix v x RD + gmv x 1 RD + gm P12.54 See Figure 12.26 in the book. P12.55 If we need a voltage-gain magnitude greater than unity, we choose a common-source amplifier. To attain lowest output impedance usually a source follower is better. 427 P12.56* We have W KP K= = 400 µA/V2 L 2 Assuming operation in saturation, we have IDQ = K(VGSQ − Vto)2 Solving for VGSQ and evaluating we have VGSQ = Vto + I DQ /K = 3.236 V VG = VDD R2 = 10 V R1 + R2 VG = VGSQ + RSIDQ Solving for RS and substituting values we have RS = (VG − VGSQ)/IDQ = 3.382 kΩ We have gm = 2 KI DQ = 1.789 mS RL′ = 1 = 1.257 kΩ 1 / RL + 1 / RS + 1 / rd Av = Rin = v in = RG = R1 R2 = 666.7 kΩ iin Ro = P12.57 gm RL′ vo = = 0.6922 v in 1 + gm RL′ gm + 1 1 Rs + 1 = 386.9 Ω rd (a) We start by assuming that the MOSFET is operating in the saturation region, so we have I DQ = K (VGSQ −Vto ) 2 Also, we have K = 21 KP (W / L) = 1.5 mA/V 2 For a dc Q-point analysis, the capacitors behave as open circuits. Writing a voltage equation from the gate through Rs and back to ground through the VSS source, we obtain VGSQ + Rs I DQ =VSS Substituting for IDQ we have VGSQ + Rs K (VGSQ −Vto )2 = VSS 428 Then substituting numerical values, we have VGSQ + 4.5(VGSQ − 1)2 = 15 Solving, we obtain VGSQ = 2.656 V (The other root is extraneous.) Then we have I DQ = K (VGSQ −Vto ) 2 = 4.114 mA VDSQ = 30 − I DSQ (RS + RD ) = 5.316 V Since VDSQ is higher than VGSQ − Vto the assumption that the device operates in the saturation region is valid. gm = 2 KI DQ = 4.968 mS (b) Using the results from Exercise 12.13, we have RL′ = RD RL = 2.308 kΩ Av = v o v in = RL′ gm = 11.465 v 1 Rin = in = = 188.6 Ω iin gm + 1 Rs P12.58 See Figure 12.31 in the text. P12.59 429 P12.60 (a) (b) All inputs high: (c) All inputs low: 430