JFET Biasing Lab: Self-Biasing Method

advertisement

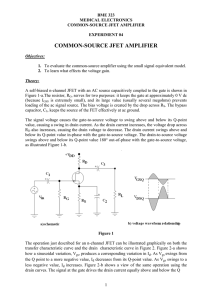

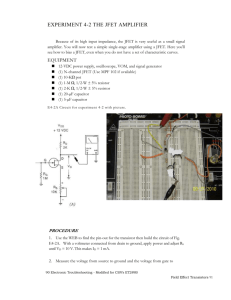

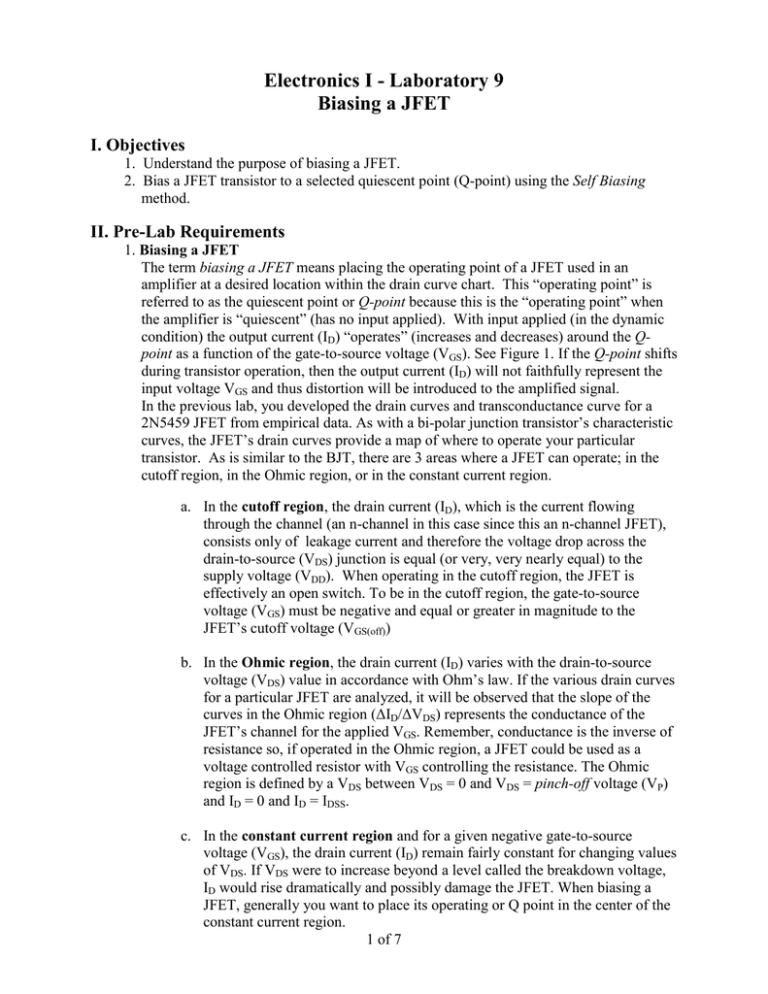

Electronics I - Laboratory 9 Biasing a JFET I. Objectives 1. Understand the purpose of biasing a JFET. 2. Bias a JFET transistor to a selected quiescent point (Q-point) using the Self Biasing method. II. Pre-Lab Requirements 1. Biasing a JFET The term biasing a JFET means placing the operating point of a JFET used in an amplifier at a desired location within the drain curve chart. This “operating point” is referred to as the quiescent point or Q-point because this is the “operating point” when the amplifier is “quiescent” (has no input applied). With input applied (in the dynamic condition) the output current (ID) “operates” (increases and decreases) around the Qpoint as a function of the gate-to-source voltage (VGS). See Figure 1. If the Q-point shifts during transistor operation, then the output current (ID) will not faithfully represent the input voltage VGS and thus distortion will be introduced to the amplified signal. In the previous lab, you developed the drain curves and transconductance curve for a 2N5459 JFET from empirical data. As with a bi-polar junction transistor’s characteristic curves, the JFET’s drain curves provide a map of where to operate your particular transistor. As is similar to the BJT, there are 3 areas where a JFET can operate; in the cutoff region, in the Ohmic region, or in the constant current region. a. In the cutoff region, the drain current (ID), which is the current flowing through the channel (an n-channel in this case since this an n-channel JFET), consists only of leakage current and therefore the voltage drop across the drain-to-source (VDS) junction is equal (or very, very nearly equal) to the supply voltage (VDD). When operating in the cutoff region, the JFET is effectively an open switch. To be in the cutoff region, the gate-to-source voltage (VGS) must be negative and equal or greater in magnitude to the JFET’s cutoff voltage (VGS(off)) b. In the Ohmic region, the drain current (ID) varies with the drain-to-source voltage (VDS) value in accordance with Ohm’s law. If the various drain curves for a particular JFET are analyzed, it will be observed that the slope of the curves in the Ohmic region (ΔID/ΔVDS) represents the conductance of the JFET’s channel for the applied VGS. Remember, conductance is the inverse of resistance so, if operated in the Ohmic region, a JFET could be used as a voltage controlled resistor with VGS controlling the resistance. The Ohmic region is defined by a VDS between VDS = 0 and VDS = pinch-off voltage (VP) and ID = 0 and ID = IDSS. c. In the constant current region and for a given negative gate-to-source voltage (VGS), the drain current (ID) remain fairly constant for changing values of VDS. If VDS were to increase beyond a level called the breakdown voltage, ID would rise dramatically and possibly damage the JFET. When biasing a JFET, generally you want to place its operating or Q point in the center of the constant current region. 1 of 7 Figure 1. Location of a Quiescent Point (Q-point) 2. Methodology for Biasing a JFET Using a Self Biasing Scheme. In the previous lab, where the drain characteristic curves were developed for the 2N5459 transistor, a voltage source was used to control VGS and another voltage source was use to control ID. The use of two separate voltage sources complicates design and increases the component count for your circuit. A biasing method employing a single voltage source is more desirable. Figure 2 shows a simple biasing scheme for the JFET referred to as self biasing. Figure 2. Self Biasing Scheme for a JFET Determine VDD In the self biasing scheme, the supply voltage (VDD) is the first parameter to be determined. This is done by picking an appropriate voltage based on an analysis of transistor’s limitations, circuit limitations, power supply limitations, and voltage gain required. 2 of 7 Determine Q-Point With the value of VDD determined, the location of the desired Q-point must now be selected based on input and output considerations. When you are using a JFET as an amplifier, the drain current, which is the output, is controlled by the magnitude of the gate-to-source voltage which is the input. Your input will generally be an alternating signal that will have some peak-to-peak value and your goal is to reproduce that input signal, at the output, with gain and a reasonable degree of fidelity. To do this, the full range of your input and output signals must remain within the constant current region of the JFET’s operation. Therefore, when biasing for an amplifier circuit design, you need to know or approximate what your input voltage will be. When you have determined the input voltage range, i.e. the value the voltage changes between the upper and lower limit, select half of this voltage swing. This midpoint will be used to select your VGS bias value. Your VGS bias value must be located such that upper excursions when VGS becomes less negative (when the input signal becomes more positive) and the lower excursions when VGS becomes more negative (when the input signal becomes more negative) stay in the constant current operating region of the JFET. Since VGS is represented by an entire curve on your plots, your next step is to select a single point on that VGS curve. This is done by picking a drain-to-source voltage value. A general rule is to select a VDS value half way between the planned VDD and the pinch-off voltage (VP) for VGS = 0. This places the Q-point near the center of the constant current region. Where the value of VDS (displayed on the Y-axis) and the value of VGS coincide is the desired Q-point. With the Q-point selected, the final step is to define the value of ID at the Q-point. To do this, extend a horizontal line from the intersection of VDS and VGS (the Q-point) through the Y-axis. The point of intersection of this line with the Y-axis is the value of ID for the selected Q-point. You should now have the Q-point values for the following parameters: a. ID b. VDS c. VGS Determining Values for RG, RD and RS Source Resistor (RS) To operate a n-channel JFET as an amplifier, the gate junction must be reversed biased i.e. electrically negative in relation to the source. To negatively bias the gate-to- source junction, a negative voltage source could be placed between the gate and ground; however, this method is not generally used since it would require addition of another voltage source to the circuit. A more efficient method to achieve a negative bias between the gate-to-source junction is to electrically “raise” the source above ground. Figure 3 illustrates this method. The JFET’s gate is maintained at ground level through a resistor (RG) connected directly to ground. Despite the resistor between it and ground, the gate stays at (or extremely close to) ground potential because the reversed biased 3 of 7 drain-to-gate junction current is extremely low and can be considered non-existent, therefore, no voltage develops across RG. As source current flows through RS from source to ground, the source side of the resistor is raised above ground in accordance with Ohm’s law. This action results in a negative bias between the gate which is at 0V or ground potential and the source which is at (IS*RS) V. This self biasing provides the negative bias for the gate-to-source junction that is required for the JFET to operate as an amplifier. Figure 3. Self Bias Voltages and Currents To compute the value of the source resistor (RS), the values of VGS and ID at the desired Q-point are applied to the equation below: Drain Resistor (RD) The drain resistor is used to set the value of the drain current. Since we know the value of ID and VDS at the desired bias point, as well as the value of VDD, we can easily compute the value of RD so that the desired bias point is achieved. The equation below is germane: 4 of 7 Gate Resistor (RG) The gate resistor serves two purposes. First, it connects the gate to ground thus keeping the gate voltage at 0V or ground potential and second, it provides a high resistance path to ground for an input signal. One of the advantages of a JFET is its high input impedance which results in negligible loading on the input signal source to a JFET based circuit. Without utilizing a large resistance value for RG, the advantage of the JFET’s high input resistance would be lost, since to the input signal the JFET circuit would be seen as the high impedance JFET in parallel with much smaller resistance of RG. The resultant of this parallel resistive combination would be an input resistance that is less than the resistance of RG. As a design rule of thumb use a 10MΩ resistor for RG. 3. DC Load Line. When the JFET is biased for use as an amplifier and no input is provided the amplifier will operate at its Q-point, which is the quiescent operating point lab. When an input is provided; however, the operating point will move based on changes in VGS caused by changes in the input signal. When this occurs, a unique thing happens. The operating point slides up and down a line, called the DC. Load Line. This load line is shown in Figure 4. The slope of this line is the reciprocal of the sum of the resistances in the drain and source circuits with one end point defined as the drain-to-source voltage with VDD applied when the JFET is cutoff and the other as the drain current with VDD applied with the JFET is fully conducting. The Q-point, of course is located on that line. Figure 4. JFET DC Load Line 4. III. Laboratory Requirements 1. Required Parts and Equipment A. B. C. D. E. F. G. 1 - DC power supplies 1 - Bench DMM 1 - Fluke hand-held DMMs 1 - Proto-Board (PB-103) 1 – 2N5459 JFET Resistors as required by student’s design Wires and leads for circuit connections. 5 of 7 2. Required Information A. Transistor Data Sheets The following is a link to the specification sheet for the 2N5459: http://fairchildsemi.com/ds/2N/2N5459.pdf B. 2N5459 Pinout Figure 5 shows the pin orientation for the 2N5459 Figure 5. 2N5459 Pin Orientation C. 2N5459 collector characteristic curves developed from Lab 4. 3. Laboratory Procedure A. Self Biasing a 2N5459 In this experiment a 2N5459 JFET will be biased using a self biasing scheme in order to place its Q-point at a predicted location within the constant region of the drain s chart developed in Lab 8. The JFETS bias parameters will be measured to verify compliance with the design parameters. a. Design your biasing circuit and develop its schematic in PSpice. b. Construct your designed circuit on a Protoboard. c. Test your circuit and record the parameters in Table 1. Parameter Measured Value Designed Value Simulation Value VDD VDS VGS VRD VRS ID Table 1. Parameter Table for Base Biased 2N5459 4. Data Reduction and Lab Report This Lab submittal will be an informal report. Your report should be in Word with graphics pasted in. 6 of 7 A. For the 2N5459 self biasing circuit submit the following: a. PSpice schematic of the circuit with all circuit components labeled. b. A PSpice Bias Point analysis of each biasing circuit showing all pertinent biasing parameters. c. A populated parameters Table 1 for each biasing circuit. d. An Excel plot of your 2N5459 drain curves showing the location of your designed Q-point, your measured Q-point, and the DC load line. 7 of 7