passive lossless snubbers for high frequency pwm converters

advertisement

PASSIVE LOSSLESS SNUBBERS FOR HIGH

FREQUENCY PWM CONVERTERS

Sam Ben-Yaakov and Gregory Ivensky

Power Electronics Laboratory

Department of Electrical and Computer Engineering

Ben-Gurion University of the Negev

P. O. Box 653, Beer-Sheva 84105, ISRAEL

Tel: +972-7-646-1561; Fax: +972-7-647-2949

Email: sby@ee.bgu.ee.ac.il

March 1999

1

OUTLINE

Chapter 1. Introduction

1. Seminar objectives

2. Hard versus soft switching

3. Diode reverse recovery

4. IGBT behavior under hard switching

5. Why soft switching?

6. Soft switching terminology

7. Soft switching by passive lossless snubbers

8. Simulation tools

Chapter 2.

Passive lossless snubbers perspective

1. Passive lossless snubber approaches

2. Snubbers evolution

3. The switched inductor (SIM) model

4. Basic switching cell of common PWM converters

5. Fundamental principles

6. Practical aspects

Chapter 3.

Basics of resonant networks

1. Reset of resonant elements

2. Resonant networks - the vehicle of snubbing and energy

circulation

3. Basic resonant network parameters

4. Ideal LC-network with ideal diode fed by a voltage source Vs

5. Some trivial cases and practical aspects

6. Resonant inductor design

2

Chapter 4.

Switch turn-off lossless snubbers

1. The ‘one way’ capacitor. Versions 1 and 2 (SNB1 & SNB2)

2. Switch turn-off lossless snubber (SNB3)

3. Applying snubber SNB3 in a flyback converter

4. Applying snubber SNB3 in a forward converter

5. A switch turn-off lossless snubber for a boost converter

(SNB4)

Chapter 5.

Switch turn-on and diode turn-off

snubbers

1. Flyback reset snubber. Versions 1 and 2 (SNB5 & SNB6).

Practical aspects

2. Low stress turn-on snubber (SNB7). Experimental results.

Implementation in APFC

3. RMS current of the snubber inductor in a boost converter

implemented in APFC

Chapter 6.

Turn-on and turn-off single switch

snubbers

1. Generic LCC 'turn off' & 'turn on' snubber topology

2. Boost converter with LCC snubber: D type 'on' and S type

'off' (SNB8)

3. Some additional recent turn-on & turn-off passive lossless

LCC snubbers (SNB9 - SNB12)

4. LCC snubbers with improved reset (SNB13)

5. Boost converter with LLC-type snubber (SNB14)

3

6. Buck converter with LC-type snubber (SNB15)

7. Turn-on, turn-off and turn-on - turn-off snubbers. Can

parasitic elements be used?

Chapter 7.

Rectifier diodes lossless snubbers

1. Phase shifted PWM (PSPWM) converters

2. Residual issues in PSPWM

2.1. Circulating current. Lossless output snubbers SNB16 &

SNB17

2.2. Rectifier’s diodes reverse recovery. Possible remedysaturable reactor. Snubber SNB18

3. Experimental PSPWM converter

4. Improved magnetic snubber for rectifier diodes in DC/DC

converters (SNB19)

Chapter 8.

Combining snubber and power supply

functions

1. Turn-off snubber with energy recovery back to the input or

into a local power supply (SNB20)

2. A local power supply with turn off snubber features

3. Application of proposed power supply in a boost APFC

Conclusions

References

4

Chapter 1

INTRODUCTION

5

SEMINAR OBJECTIVES

• To demonstrate the use and benefits of passive lossless

snubbers in modern high frequency power electronics

design.

• Relevant topologies

• Soft switching

• Parasitic effects

• Limitation - pros & cons

HARD VERSUS SOFT SWITCHING

V=200v

Vds

Vgs*20

100 Rd

12

0

Rg G

+ 2.7

-

Id*30

D

PWRMOS

IRFP460

MOSFET switching stage

Switching waveforms

(simulation)

• Switching losses are proportional to switching frequency

Modern simulators include switching behavior

6

Id

Vds

V=200v

I0=5A

D

15

0

+

-

Rg G

2.7

Vgs*10

Lm

1m

10n MUR860

Ls

D

PWRMOS

IRFP460

V=400v

Hard switched boost stage

Basic waveforms

(simulation)

☛ Diode reverse current and parasitic oscillations

☛ Natural 'softening' at 'turn off'

• 'Turn On' more troublesome in MOSFETS

• 'Turn On' & 'Turn off' problematic for IGBT -> ZCS

Diode Reverse Recovery [25, 39]

i

IF

VF

L

i

VD

VD

t rr

t rm

D

0.25 I rm

t

Vr

I rm

Vrm

• Low voltage drop on diode in reverse recovery period

•

di = V

dt L

• High reverse currents

• High reverse voltage

• Parasitic oscillations

7

The reverse recovery problem in Boost

topology

Dout

Lm

Vout

+

Iin

Ir

Vin

-

S

C o Ro

Vgs

• Short circuit against Vout

• Occurs in all topologies

The reverse recovery problem in Boost

topology

Vgs

I (Dout)

t

I in = 10A

t

I rm = - 69A

I (Switch)

79A

I in = 10A

t

P (Switch)

27kW

trr = 50nsec.

• High reverse currents

• High losses

• EMI emission

8

t

Dependence on L

V=-400v

I0

MUR860

L

D

50

Rs

Cs

0.5nF

Diode switching circuit - reverse recovery

Dependence on L - Simulation

Idiode

Idiode

Diode reverse recovery switching waveforms

Very high reverse currents

A function of series inductance

Detrimental effect in isolated and non isolated

converters

Becomes very important in high switching frequency

9

converters

Trapped Energy as L becomes Larger

Assume: t rm constant

Irm = V

L trm

Peak reverse current :

Trapped energy

(V trm )2

E = (Irm ) L =

2L

1

2

2

• Trapped energy decreases as L becomes larger

• Adding inductance ---> Advantageous

Center Tap Rectifier

Llkg

1

+

Llkg

2

10

CO

RO

Leakage inductance at secondary

Diode voltage

Voltage at input to

filter inductor

Experimental waveforms (no diode snubber)

• Greatly influenced by transformer leakage

• Forces the use of high voltage diodes

IGBT BEHAVIOR UNDER HARD SWITCHING

[5, 16, 20, 21, 38]

Vcc

Ic

Ic

Rc

Vce

Rb

Vce

Vg

t

Current tail

11

☛ Current tail due to stored minority carriers

☛ Switching losses increase linearly with switching

frequency

☛

Switching frequency limit is at about 25 kHz

Why Soft Switching ?

magnetics

size

ideal

f

Ideal Size/Switching frequency relationships

magnetics

size

conventional

planar

~100kHz ~500kHz

f

Practical size realization

12

MOSFET

Losses

PWM

Hard

IGBT PWM Resonant

Soft Soft

Frequency

Losses

Conflicting constraints

✏

Soft switching helps to reduce EMI emission ???

SOFT SWITCHING TERMINOLOGY

13

VGS

Hard Switching

Vs

Vs

Vs

Is

True

ZVS

Is

Pseudo

ZCS

Pseudo

True

Is

'True' soft switching calls for external active circuitry

'Pseudo' soft switching by lossless snubbers

14

Soft Switching by Passive Lossless Snubbers

Vs

Pseudo

ZCS

Pseudo

ZVS

Is

Turn On

Turn Off

• For MOSFETs -> OK

• For IGBTs -> ZCS at 'turn off' might be more desirable

(current tail)

• This can not be accomplished with a Passive Snubber

unless operating in constant 'off' time (quasi-resonant)

15

SIMULATION TOOLS

✔ Modern device models account for switching behavior

☛

Old Models DO NOT account for switching behavior

☛

Difficult to account for PCB parasitics

☛

Simulation of switching losses is still unreliable

✰

✔

Cycle-by-Cycle simulation

Can faithfully describe the basic switching

phenomena

Very useful tool to examine snubber operation

✔

✔

Average Simulation [3]

Can account for snubber effect on dynamics

Can be used to design the feedback loop

✔

✰

MODEL MUR860 D (IS=783U RS=30M N=4.82 BV=600

IBV=10U

+ CJO=330P VJ=.75 M=.333 TT=79.2N)

* Motorola 600 Volt 8 Amp 55M us Si Diode 02-24-1994

.MODEL DN5406 D (IS=2.68P RS=7.31M N=1.17 BV=900

IBV=10U

+ CJO=124P VJ=.6 M=.333 TT=14.4U)

* Motorola 600 Volt 3 Amp 15 us Si Diode 11-23-1990

• Parameters can be changed to test various aspects, e.g.TT

for reverse recovery

16

.SUBCKT IRF150 10 20 30

* TERMINALS: D G S

M1 1 2 3 3 DMOS L=1U W=1U

RG 20 2 5.35

RD 10 1 4.3M

RDS 1 3 635K

CGD 4 1 2.75N

RCG 4 1 10MEG

MCG 4 5 2 2 SW L=1U W=1U

ECG 5 2 2 1 1

DGD 2 6 DCGD

MDG 6 7 1 1 SW L=1U W=1U

EDG 7 1 1 2 1

DDS 3 1 DSUB

LS 30 3 7.5N

.MODEL DMOS NMOS (LEVEL=3 VMAX=1.6MEG THETA=265.6M

VTO=3.3

+ KP=9 RS=8.12M IS=2.01P CGSO=2.65M)

.MODEL SW NMOS (LEVEL=3 VTO=0 KP=.45)

.MODEL DCGD D (CJO=2.75N M=.5 VJ=.41)

.MODEL DSUB D (IS=2.01P RS=5.20M VJ=.8 M=.4 CJO=2.60N

TT=720N)

.ENDS

* IR 100 Volt 28 Amp 45M Ohm N-Channel Power MOSFET 11-201990

Chapter 2

PASSIVE LOSSLESS SNUBBERS PERSPECTIVE

17

Lr

C

D

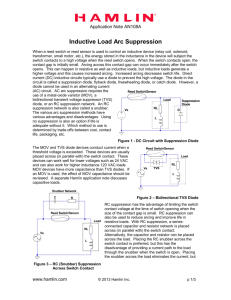

RC SNUBBERS - Diode RC snubber

(2 Vo )2 C

} fs ;

2

LOSSES P d(min) = {

Pd(min) = minimum losses

V o = output voltage

C = snubber capacitor

fs = switching frequency

R

( I pkr ) 2 Llkg

}fs

P d(lkg) = {

2

I pkr = peak reverse current

Llkg = leakage inductance

Resistor dissipation may reach 10's of Watts

PASSIVE LOSSLESS SNUBBER APPROACHES

1. Snubbing in multiple switch configuration (e.g. half

bridge)

2. Auxiliary (dual) switch snubbers [4, 15, 33, 37]

3. Snubbers in single switch configuration (references

given below)

No. # 1: Most effective

• Few extra components => economical

No. # 2: Effective but costly

• Calls for extra switches and drives

• Diminishing return

No. # 3: Good compromise

• Only passive elements needed

• Proven to improve efficiency

• Potentially lowers EMI emission

☛ This seminar will concentrate on single switch and diode

snubbers for PWM converters

18

Snubbers Evolution

• SCR (1): RC snubbers - high losses

• SCR (2): Lossless Snubbers - help to turn off devices

• PWM (1): RC Snubbers - high losses

• PWM (2): Quasi Resonant - high stresses and conduction

losses

• PWM (3): Auxiliary Switch - complex

• PWM (4): Lossless Snubbers -optimal (as of now)

Passive Lossless Snubbers are comparable in

performance to the Dual Switch approaches but are less

expensive !

The Switched Inductor (SIM) Model

BASIC SWITCHING CELL OF COMMON PWM

CONVERTERS

LLff

da

b

iaI b

Vin

R Load

iI c

c

d

Vout

IL

iILL

+

--

Lf

a

Vout

a

Ic

R Load

Vin +

-

Ib

Cf

Cf

b

c

b

Buck

Boost

b

c

Vout

d

Ib

Ic

R Load

Lf

+

Vin -

IL

a

Buck-Boost

19

Cf

BASIC SWITCHING CELL OF COMMON PWM CONVERTERS

A

C

Do

Lo

S

B

Topology

V in

Buck

Boost

Buck-Boost

V CB

V AB

V AB

Vo

Topology

V AB

V CA

V CB

-V CA

Buck

Boost

Buck-Boost

V in -V o

V in

V in

Fundamental Principles

dI

1. Controlling dt at 'Turn On' -> Pseudo ZCS

A

Do

C

A

Do

C

Lo

Lo

Ls

Ls

S

S

B

B

S - type

Turn-On snubber

D - type

Turn-On snubber

20

V CB

V in

Vo

V in +Vo

Fundamental Principles

dV

2. Controlling dt at 'Turn Off' ->

A

C

Do

A

A

C

Do

Lo

Pseudo ZVS

Cc

Cc

C

Lo

Lo

S

Do

Cc

S

S

B

B

S - type

Turn-Off snubber

D - type

Turn-Off snubber

B

L - type

Turn-Off snubber

The major objective: to circulate the trapped energy

• In a lossless manner

• Without increasing the switch and diode stresses

• As quickly as possible (Don & Doff limitations)

• Without generating new parasitic effects (of extra

components)

• Inexpensive to implement

Use the followings as check points for comparison

I pk(switch)

V max (switch)

V max (diode)

21

General Observation

A

Do

C

Lo

S

B

Snubber solution is independent of (PWM)

topology if confined to the 'A-B-C' domain

Practical Aspects (1)

Snubber inductor rms current:

A

Do

C

Lo

Ls

S

B

• Snubber inductor carries switch plus reverse recovery

currents

22

A

Do

C

Lo

Ls

S

B

• Snubber inductor carries diode plus reverse recovery

currents

Practical Aspects (2)

Stirring capacitor's ripple current

A

C

Do

A

A

C

Do

Lo

Lo

Lo

Cc

Cc

S

Cc

S

S

B

B

B

C

Do

(a)

(b)

(a) Ripple stirred to 'ground' - in Boost topology

(b) Ripple stirred to output - in Boost topology

23

(c)

(c) Ripple stirred to input - in Boost topology

24

Chapter 3

BASICS OF RESONANT NETWORKS

25

Reset of Resonant Elements

At steady-state:

• Volt-Sec of resonant inductor over switching cycle must be

zero

∫

Ts

V Lr dt = 0

• Ampere- Sec of resonant capacitor over switching cycle

must be zero

∫

Ts

IC r dt = 0

• Sufficient time must be available for reset

•

This will cause restriction on duty cycle min & max

Resonant Networks

-the vehicle of Snubbing and Energy Circulation

• Energy circulation in passive lossless snubbers is made

possible by lossless energy exchange of reactive elements

(i.e. C, L)

• When the exchange is between L & C one deals with

resonant phenomena

26

Basic Resonant Network Parameters

D

L

R

C

V

• Typical equivalent circuit of a lossless snubber

➜

➜

➜

➜

➜

Series resonance

R is normally small (to make the snubber "lossless")

May or may not include diode

Peak current equal or higher than main currents

Resonant frequency need to be shorter than

switching frequency

Basic Resonant Network Parameters

i

D

L

C

Vs

VC

2π

1

1

; ωr =

; Tr =

LC

2π L C

ωr

L

➜ Characteristic impedance : Zr =

C

➜ Resonant frequency:

fr =

27

Ideal LC-network with ideal diode fed by a voltage source Vs

i(0)= Io vC(0)=V Co

i

S

L

C

Vs

VC

D

V s -V Co

i= Z

sin(ωr t)+Iocos(ωr t)

r

vC=(Vs -V Co)[1-cos(ωr t)]+IoZr sin(ωr t)+VCo

V Cp=(Vs -V Co)[1-cosψ]+I oZr sinψ+V Co

I oZr

ψ=tan-1(-V -V )+π

ψ<π

s Co

If V Co = 0 and Io = 0 ψ=π and V Cp = 2 Vs

If V Co < 0 and Io = 0 ψ=π and V Cp > 2 Vs

Vc

∆Vc

Vco

Vcp

t

Vs

i

Ip

Io

t

Tr ψ

2 π

28

SOME TRIVIAL CASES

• Linear inductor discharge

i

L

Vs +

dI L V s

dt = L ;

✌

D

iL = IL (0) −

Vs

L

t

Large capacitor acts as Vs

• Linear capacitor discharge

Is

dV C Is

dt = L

✌

;

VC

Is

vC = VC (0) + t

C

Large inductor acts as Is

29

•

Capacitor voltage reversal

i(0)=0

vC(0)=V Co

L

L

C

VCo

C

Beginning

End

Practical Aspects (3)

Practical Snubber Components

• Reverse recovery of snubber diodes

I

I

L

L

Vs +

Vs

D

Before reset

Cp

Diode snapped

Parasitic oscillations

✔

+

Remedy -> Saturable Reactor

30

VCo

Practical Aspects (4)

Practical Snubber Components

• ESR of resonant Capacitor

High losses, high temperature

✔

Remedy -> Low ESR capacitors:

Polypropylene

Mica (the best !!)

• Interwinding capacitance of resonant inductor

Li

Cp

Li

Cp

Li

Cp

Parasitic oscillations , high losses, EMI emission

✔

Remedy ->

Careful design, toroidal configuration,

good coupling between windings

31

• Printed circuit layout

Parasitic oscillations , high losses, EMI emission

✔

Remedy -> Careful design

Resonant Inductor Design

Typical characteristics

• Low inductance ; Typical range 3µH - 10µH

• High current ; Typical range 1A -30A

Some basic relationships:

L I

pk

Bmax = n A ;

e

∫ V Ldt

∆B = n A

e

n2 µ µ A

o r e

L=

;

l

e

L - inductance (H)

I pk - peak inductor current (A)

V L - voltage across inductor (V)

t - time (Sec)

n - number of turns

Bmax - limit of magnetic flux density (T)

A e - effective core area (m2)

le - effective magnetic length (m)

µo - permeability (1.25 10-6 H/m)

µr - relative permeability

32

From above

I

pk 1 Bmax le

L = L n µ o µr

I pk

For high L ratios:

• Long l e

• Small number of turns n

• Low relative permeability µr

• Winding window will no be full

Typical Construction

Ferromagnetic Gap

Gap

Ferrite

Ferrite

Toroid based design

Lower EMI emission

33

Suggested Design Procedure

1. Choose ∆Bmax based of acceptable losses (mW/gr) from

ferrite data (losses as a function of ∆B and frequency). Use

fr as an indicator but take into account the short period of

snubbing by dividing the data sheet losses by (f r /f s )

2. Estimate {V Sec} across resonant inductor

∫V

L

dt or by an

approximation e.g. VL * trr

3. Calculate nAe from the relationship:

n Ae

V dt

∫

=

L

∆Bmax

4. Select wire cross section according to rms current

5. Based on calculated nAe and wire size, choose a core for a

single layer winding

6. Gap the core for required L value

Chapter 4

SWITCH TURN-OFF LOSSLESS SNUBBERS

34

35

SWITCH 'TURN OFF' LOSSLESS SNUBBER (SNB1)

The 'One Way' Capacitor : Version 1 [35]

Snubber

D2

C2

D3

L

C1

D1

A

+

Lo

IA

+

Do

VAB

C

VCB

S

B

Vgs

-

-

B

Snubber

Snubber

C2

C2

D2

D3

D3

D1

A

+

Lo

L

C1

C1

+

IA

VAB

C

VCB

A

+

-

Vgs

B

+

IA

VAB

C

VCB

S

S

B

Lo

B

Snubbing

-

Vgs

-

Reset

• Snubber capacitor C1+C 2

• Resonant reset ( C1+C 2, L)

36

B

General Observations (1)

1. Snubbing

Snubber

D2

C2

A

C

Do

D3

D1

Lo

C1

Cc

A

+

Lo

+

IA

VAB

B

C

S

VCB

Vgs

-

S

-

B

B

• Prior to 'turn-off', C1 & C2 must be charged to VCB

2. Reset

Snubber

C2

D3

L

A

+

Lo

i

C1

+

IA

VAB

S

C

L

C

Vs

VCB

S

B

-

Vgs

-

D

B

V C= 2 VCB

if C1 = C2 ->

VC1 = V C2 = V CB

37

VC

General Observations (2)

Snubber

D2

C2

A

D3

D1

A

+

Lo

L

IA

+

VAB

B

Lo

C1

Do

Cc

C

VCB

Vgs

-

C

Do

S

S

-

B

B

• Topology independent

2.0V

0V

Vgs

v(pulse)

2.0A

0A

500V

iL r

Ipk

i(lr)

Vc1

-10V

2.0A

v(out,vd1)

500V

is

IA

0A

i(smain)

Vs

0V

488us

490us

v(drain)

t0

492us

t1

494us

Time

Waveforms of SNB1 (simulation)

38

496us

t2 t 3

498us

500us

Interval t o-t1

t

iL=iD3=I pksin(2π T )

Assuming: C 1=C2=C

Tr

LC

t1-to= 2 =π

2 ;

r

I pk=

V CB

2L

C

;

iS=I A +i L

t

vC1=vC2=0.5V CB[1-cos(2π T )]

r

Interval t 1-t2

iS=I A ;

iDo=iD1=iD2=iD3=0

IA

vC1=vC2=V CB-2C(t-t2) ;

Interval t 2-t3

vC1(t3)=vC2(t3)=0

2CVCB

from which: t3-t2= I

A

Interval t 3-(to+T s )

dvS

IA

and hence ( dt )

=2C

t2-t3

iDo=I A ; iS=iD1=iD2=iD3=0

Typical Design

dvS

Given: VCB, I A , ( dt )

, Dmin , Dmax

t2-t3

IA

2CVCB

1. C ≥ dv

;

2. t2-3= I

S

A

2( dt )

t2-t3

Dmin 2

2(

1-Dmax

fs )

3. fs ≤ t

4. L=

2-3

π 2C

V CB

I pk

π VCB

=>

=

IA

dvS

2L

ton min ( dt )

t2-t3

C

The diodes D 1 & D2 must be very fast and have a very low

5. Ipk=

storage charge.

39

Example:

dvS

Assuming: f s ≈ 100KHz; ton min ≈ 1µS ; ( dt )

≈ 400V/µS

t2-t3

I pk

I A = 0.78

✔ Check points

I pk(switch)

I A π VCB

dvS

ton min ( dt )

t2-t3

= IA +

V max (switch) = Same as original

V max (diode) = Same as original

SWITCH 'TURN OFF' LOSSLESS SNUBBER

The 'One Way' Capacitor : Version 2 (SNB2) [35]

Snubber

D2

C2

D3

D1

A

+

Lo

L

Do

C1

VAB

B

-

Lo

+

Do

IA

A

S

-

Cc2

C

VCB

Vgs

S

B

• Identical to Version 1 (normally drawn differently)

40

C

Cc1

B

SWITCH 'TURN OFF' LOSSLESS SNUBBER (SNB3) [35]

Reset to Input

IA

A

Do

Lo

+

+

C

D1

- +

L C1

VAB

VCB

Snubber

B

D2

-

S

Vgs

-

A

Do

Lo

IA

A

Lo

+

+

C

Cc

D1

- +

C1

VCB

S

S

B

-

Vgs

-

B

Snubbing

41

B

B

C

IA

A

Lo

+

+

C

i

D1

- +

VAB

B

L

C1

D2

-

VCB

Vgs

L

C

S

-

B

Reset 1

✌

VCA > V AB ---> Dmin = 0.5

i

IA

A

Lo

+

+

C

L

D1

VAB

VCB

L

Snubber

B

D2

-

S

Vgs

-

Vs +

B

Reset 2

1.0A

0A

is

i(smain)

500V

Vs

0V

800mA

0A

800mA

0A

400V

v(drain)

iD1

i(d1)

iDo

i(dout)

Vc1

-400V

488us

490us

v(drain)-v(vc1)

t0

t1

492us

t2

494us

Time

Waveforms of SNB3 (simulation)

42

496us

t3

498us

t4

500us

D

VCo

Case VCB-V AB > V AB , i.e. VCB > 2V AB

Interval t o-t1

t

iL=iD2=I pksin(2π T )

r

where

Tr =2π LC1

V CB-V AB

I pk=

L

C1

iS=I A +i L

t

vC1=(VCB-V AB )cos(2π T )

r

t1 is found from the condition:

(vC1)t1=-VAB

Tr

V AB

t1= cos -1(V -V )

CB AB

2π

Interval t 1-t2

t1 V AB

iL=iD1=iD2=I pksin(2π T )- L (t-t1)

r

t2-t1 is found

from the condition: (iL)t2=0

t2-

t1

I pkLsin(2π T )

r

t1=

V AB

Interval t 2-t3

iA =I Ao -iL

iS=I A ; iDo=iD1=iD2=0

Interval t 3-t4

iS=iDo=iD2=0

I Ao

vC1=-VAB + C (t-t3)

1

t4-t3 is found from the

condition:

43

(vC1)t4=V CB-V AB

C1V CB

t4-t3= I

Ao

Interval t 4-(to+T s )

iDo=I Ao

iS=iD1=iD2=0 ;

44

Typical Design

dvS

Given: VCB, I Lo, ( dt )

,

t3-t4

Dmin ≥ 0.5, Dmax

1. C1 ≤ \f(ILo,(\f(dvS,dt))

)

;

1-Dmax

3. fs ≤ t

;

3-4

;

t3-t4

2. t3-4 =\f(C1V CB,I Lo)

Dmin 2

( f )

s

4. L≈ 2

(assumption: iL has a sine waveform not only

π C1

during

interval to-t1 but also during

t1-t2)

V CBDmax

5. Ipk=

L

C1

✔ Check points

I pk(switch)=ILo+

πDmax V CBI Lo

(no free lunch)

dvS

ton min ( dt )

t3-t4

V pk(switch) = Same as original

V pk(diode) = Same as original

Limitation: VAB ≤

V CB

2

Vo

In Boost Power Factor, hard switching when Vin ≥ 2

45

Applying snubber SNB3 in a flyback converter

[6, 26, 28]

SNUBBER

-

Tr

R'o

V'

Co' + o

Lm

D1

-

Ro

Co

V

+ o n2

n1

Do

D1

+

-

C

V in

+

L lkg

-

- +

C

L

S

D2

V in

L

S

D2

Basic topology

Lm

Llkg

Do

Equivalent circuit

- output transformer magnetizing inductance

- output transformer leakage inductance

C - snubber capacitance

L - snubber inductance

Ro'

- reflected load resistance

Co'

- reflected capacitance of the output filter

S - switching transistor

Do

- output diode

D1, D2- snubber diodes

V in

- input voltage

V o'

- reflected output voltage

46

Equivalent circuit at different time intervals

-

R'o

-

Lm

Co' +

R'o

Lm

Co' +

L lkg

V in

-

D1

i lkg

+

L lkg

+

-

V in

- +

S

1.

C

S

ON

2. Snubbing 1

-

R'o

V'

Co' + o

Lm

D1

Do

+

L lkg

- +

-

V o'

V in

+

i

D1

+

-

L lkg

C

S

C

3. Snubbing 2

47

-

R'o

Lm

Co' +

Do

4. OFF

-

R'o

V'

Co' + o

Lm

Do

+

L lkg

+ -

C

S

V in

-

L

D2

5.

Resonant reset - ZCS at 'turn on' by Llkg !!

-

R'o

V'

Co' + o

Lm

Lm

Do

+

L lkg

+ -

C

S

-

D1

+

L lkg

V in

-

+

C

L

S

D2

-

L

D2

6 Inductor discharge

48

V in

General Observation

1. Switch maximum voltage (Vs pk)

-

R'o

V'

Co' + o

Lm

D1

Do

+

L lkg

- +

-

V o'

V in

+

i

D1

+

-

L lkg

C

S

C

Capacitor's initial voltage

--> VC(0) = Vin

Capacitor maximum voltage --> VCpk > 2 Vo' +V in

{ additional voltage contributed by energy removed from Llkg }

Switch maximum voltage --> Vs pk > 2 (Vin +V o')

Advantages

•

The snubber is simple and inexpensive [28]

•

The operational duty cycle range is wider than in the

case when this snubber is used in a boost converter

Disadvantage

•

High voltage stress on the transistor Vs pk

49

Reverse recovery of snubber diode

-

R'o

Co' +

Lm

V o'

-

R'o

D1

Do

+

L lkg

-

- +

Co' +

Lm

V o'

D1

Do

V in

+

L lkg

- +

-

V in

C

C

S

S

Resonant reset

Reverse recovery

-

R'o

Lm

Co' +

Do

+

L lkg

-

+ -

C

V in

L

D2

Linear discharge

• Loss of C charge

• C must retain a voltage of at least Vin for proper ZVS at

'turn-off'

50

Applying snubber SNB3 in a forward converter [40]

L1

Ro

+

Co

-

Vo

SNUBBER

D3

D4

D1

+

-

C

V in

L

S

D2

Same advantages and disadvantages as for the flyback

converter case:

- the snubber is simple and inexpensive

- high voltage stress Vs pk on transistor.

V s pk = V in +V Cp

where

V Cp=

Lm

Llkg

Im

I s pk

-

Lm I m 2+L lkg I Sp2

C

magnetizing inductance of the transformer

primary leakage inductance

magnetizing current of the transformer

switch current in the moment when the switch is

turned off

Experimental results [40]

1) Vin =17V; Pout=17W; D=2/3; Vs pk=52V

2) Vin =34V; Pout=36W; D=1/3; Vs pk=88V

51

A switch "turn-off" lossless snubber for a boost

converter [30]

(SNB4)

L

D1

A

C

Do

+

Lo

V in

Do

C

S

-

+ Vo

Co

Lo

Ro

Cc

S

D2

B

Snubber elements:

L

- the resonant inductor

C

- the resonant capacitor

D1, D2

- snubber diodes

No common ground !

Equivalent circuits for different time intervals

Lo

+V

o

+

Vin

-

S

i

Lo

t1-t2

Co

= is

ON

52

Ro

53

Do

+

+V

o

Lo

S

V in

C

+

-

iLo =i c

Co

-

Ro

D2

t2-t3 , snubbing

dvS iLo

dt = C

ZVS!

vDo(t) = vC(t)-V o

vC(t3) =V o

vDo(t3)=0

+

Lo

+V

o

Do

V in

Co

t3-t4

OFF

54

Ro

L

D1

+V

o

Lo

+

Vin

ic

iLo

S

is

Co

Ro

+

C

-

-

D2

t4-t5 , reset

V in

iL= iC = Z sin(ωr t)

r

vC(t4)=Vo

1

ωr =

LC

Zr =

L

C

V in

ISp=I Lo+ Z

r

vC(t5)=vD2(t5)=0

iS=iLo+i C

L

D1

+V

o

iL

+

V in

Lo

Co

S

-

D2

t5-t6, linear discharge

55

Ro

iL(t) = iD1(t) = iL(t5) -

V o-V in

(t-t5)

L

iL(t6)=iD1(t6)=0

56

A switch "turn-off" lossless snubber for a boost

converter [30]

(SNB4)

Advantages

•

Soft switching at turn off. Efficiency was reported to

increase by 5% to 97% [30] .

Disadvantage

• Reverse recovery problems of diodes Do, D1, and D 2

• High current stress of main switch during the interval t4 - t5

• No common ground between input and output

Chapter 5

SWITCH TURN-ON AND DIODE TURN-OFF SNUBBERS

57

SWITCH 'TURN ON' AND DIODE 'TURN OFF' SNUBBER

[35,39]

FLYBACK RESET SNUBBER (energy recovery via a catch

winding)

A

A

C

C

Lo Do

Lo Do

IA

IA

IS

D

1:N

L1

IS

L1

ID

S

Vg

1:N

D

ID

S

Vg

B

B

Version 1 (SNB5)

Version 2 (SNB6)

A

C

A

L o Do

Do

IA

Lo

IS

1:N

L1

Vg

Ls

S

S

B

B

Snubbing

58

C

A

C

Lo Do

I

IA

1:N

D

L

ID

Vg

S

Vs +

D

B

Reset

Practical Aspects (5)

A

C

Lo Do

IA

IS

1:N

L1

D

ID

Llkg

Vg

S

B

Beware of leakage inductance

Not practical for HF high power levels

59

2.0V

V gs

0V

v(pulse)

0.1KV

VD

-1.2KV

v(vd1,out)

4.0A

iD

0A

i(d1)

5.0A

is

0A

i(smain)

1.0KV

0V

488us

490us

v(drain)

Vs

492us

t0 t 1

494us

Time

496us

t2

498us

500us

t3

Waveforms of SNB5 (simulation)

Analysis: Version 1 (SNB5)

V CBt

iS= L

1

t1-to is found from the

Interval t o-t1

condition: iS(t1)=I A

from where

L1I A

t1-to= V

CB

V Do max=V CB(1+N)

I A V CB

iD= N - 2 (t-t2)

N L1

t3-t2 is found from the

Interval t 2-t3

condition: iD(t3)=0

I A L1N

t3-t2= V

; VS

CB

1

max =V CB(1+N)

60

t3-t2=\f(IA L1N,V CB) ; fs

1-Dmax

t3-t2

max =

1

V S max=V CB(1+N) ; VDo

max =V CB(1+N)

The lower N, the shorter is t3-t2 and hence the higher is the

upper limit of the switching frequency fs max. The lower N, the

higher is V S max. The voltage across the main diode Do is high

when N is high.

A major disadvantage of the converter is the leakage

inductance between the primary and secondary of the coupled

inductor : it will cause a large voltage spike across the switch.

Beware of reverse recovery problems of the auxiliary diode D.

FLYBACK RESET SNUBBER Version 1 (SNB5)

Typical Design

diS

Given: VCB, I A , ( dt )

, Dmin , Dmax

to-t1

V CB

L1I A

Dmin

1. L1 ≤ di

; 2. t1-0= V

; 3. fs ≤ t

S

CB

1-0

( dt )

to-t1

4. t2-3 ≤

1-Dmax

V CBt2-3

;

5.

N=

fs

L1I A

7. VDo max=V CB(1+N)

✔ Check points

61

;

1

6. VS max=V CB(1+N)

I pk(switch)

=

IA

V max (switch) = VCB (1+\f(1,N)) =VCB \b\bc(1+

IA

)

dis

toff min ( dt ) t0-t1

V max (diode) = V CB (1+N) =V CB \b\bc(1+ \f(toff

dis

min ( dt )t0-t1,I A ))

LOW STRESS 'TURN ON' SNUBBER (SNB7) [17, 24]

Lm

Dout

Ls

A

Lo

+

Iin

Cs

Vin

-

Do

Vout

Vgs

Q D1

Ls

D2

Co Ro

S

B

Q - Main switch

Dout - Main diode

D1,D2 - Auxiliary diodes

Ls, Cs - Resonant network

Basic waveforms of lossless snubber

Interval t 0-t1

62

C

Vgs

I (Dout)

I in

Irm

I in

I (D1)

I in

I (D2)

I (Ls)

Lm

+

Iin

Vin

-

Vgs

Dout

Ls

Cs

Q D1

Vout

IRR

D2

I in

V (Cs)

Co Ro

t0

t1

63

t2

t3 t4 t5

Time

t6

Interval t 1-t2

Vgs

I in

I (Dout)

Irm

I in

I (D1)

I in

I (D2)

I in

I (Ls)

Lm

+

Iin

Cs

Vin

-

Vgs

Dout

Ls

Vout

V (Cs)

V

+ Cs

Q D1

Co

D2

Ro

t0

t1

t3 t4 t5

Time

t2

t6

Interval t 2-t3

Vgs

I (Dout)

I in

Irm

I in

I (D1)

I in

I (D2)

I (Ls)

Lm

Dout

Ls

+

Iin

Vin

-

Vgs

Cs

Q D1

Vout

V

+ Cs

D2

I in

V (Cs)

Co Ro

t0

t1

64

t2

t3 t4 t5

Time

t6

Interval t 3-t4

Vgs

I in

I (Dout)

Irm

I in

I (D1)

I in

I (D2)

I in

I (Ls)

Lm

+

-

Iin

Vin

-

Dout

Ls

Vgs

Cs

Q D1

+

Vout

VC

s

D2

V (Cs)

Co Ro

t0

t1

t6

t3 t4 t5

Time

t2

Interval t 4-t5

Vgs

I (Dout)

I in

Irm

I in

I (D1)

I in

I (D2)

I (Ls)

Lm

Dout

Ls

+

Iin

Vin

-

Vgs

Cs

Q D1

Vout

V

+ Cs

D2

I in

V (Cs)

Co Ro

t0

t1

65

t2

t3 t4 t5

Time

t6

Interval t 5-t6

Vgs

I in

I (Dout)

Irm

I in

I (D1)

I in

I (D2)

I in

I (Ls)

Lm

+

Iin

Cs

Vin

-

Vgs

Dout

Ls

Vout

VC

s

Q D1

V (Cs)

D2

Co Ro

t0

t1

t2

t6

t3 t4 t5

Time

Practical requirement of peak reverse recovery current - Irm

If Irm < I in

Vgs

I in

I (Ls) Irm

Irm

V (Cs)

I (Dout)

I (D1) I in

Lm

+

Iin

Vin

-

Vgs

Dout

Ls

Cs

Q D1

Vout

I

I (D2) in

VC

s

D2

Co Ro

t1

t0

t2

To avoid the above undesired condition

I rm > Iin

66

t3

t4

Time

t5

The coupled inductor realization

1:n

+

Dout

L1 Ls Cs +

Lm

Vin

Q D1

- Vgs

Vout

D2

Co Ro

Dout - Main diode

D1, D2 - Auxiliary diodes

Ls , C s - Resonant network

Lm , L1 - Coupled inductors

n - turn ratio

Simplified equivalent circuits of the resonant elements with

coupling inductor

Vcpl on

+ Ls

C

Vcpl off

- +

Ls

s

D1

D1

V cpl on= nVin

n

V cpl off = 1+n (Vout - V in )

67

Cs

Basic waveforms of the lossless snubber

with coupling inductor

Vgs

I (Dout)

I in

Irm

I in

I (D1)

I in

I (D2)

I (Ls)

I in

V (Cs)

t0

t1

t2

t3 t4 t5

Time

t6

V Cs( t3) is larger and therefore t3-4 is smaller

68

Components Stress

Transistor

or diode

Current stress

Q

I in +I rm

Do

I in

I rm

I rm 2 +

D1

D2

V cpl on2Cs

Ls

I in

I rm =

Current

stress

Voltage stress

instance

or interval

Voltage

stress

instance

or interval

t1

t5-t6

t1

V out

V out +V Cmax

t3-t4

t2

t1<te<t2

V out -V cpl on

t0-t1

t3-t5

V out

t1-t2

(V out+V cpl on)trm

Ls

trm ≈ trr

formal reverse recovery time

V cpl on = nVin = n(1-D)Vout

ton

D= T

s

V Cmax = Irm

Ls

Cs sin(ωr t1-2)+V cpl on [1- cos(ωr t1-2)]

I rm

Ls

Cs

ωr t1-2 = tan-1(- V

) +π

cpl on

69

trr

=

An experimental 1kW Boost converter

1:n

+

- Vgs

Q - IRF460

Dout - MUR860

D1, D2 - MUR460

Ls - 3uH

Vout

L1 Ls Cs +

L0

Vin

Dout

Q D1

D2

Co Ro

trr = 60nsec.

Cs - 100nF

n=1/7

Operational conditions

Fs - 100KHz

Pout - 1000W

V in - 200V

Vout - 400V

I in - 5.8A

D - 0.5

Typical waveforms of the experimental Boost converter

Vgs

ID1

ID2

IDo

Vertical scales: 10V/div, 5A/div

Horizontal scale: 2µSec/div

70

Smaller reverse recovery current of Do

Power dissipation

60

Pdissipated (W)

48.81

calibration

curve

29.21

estimated

conduction

losses

6.75

4.54

16

with

snubber

26 30

no

snubber

∆T(0C)

o DC calibration points

Power dissipation dropped by 19.6W

Additional Comments

✔ The main advantages of the lossless snubber:

• ZCS in turn-on

• Smaller reverse recovery current

✔ The preferred embodiment is coupled inductors

✗ The main disadvantage of the snubber is limitation of the

duty cycle range

71

✔

The overall efficiency of the experimental Boost

converter

was found to increase by 1%-2%

The snubber can be adopted to other PWM topologies

Implementation in Buck converter

Vgs

Q

+

V in

-

L1 n : 1 Lo

Ls

Cs

+ -

V out

D1

Co Ro

D2

Do

Proven to increase efficiency by ≈ 2%

Implementation in a buck-boost converter

72

V gs n : 1

+

Do

Ls

+

L1

Cs D1

V in

- Vou t

D2

Co

Lm

-

73

Ro

Implementation in APFC

1:n

Dout

L1 Ls Cs +

Lm

Vin(ac)

Q D1

DRIVER

•

Vout

D2

Co Ro

PF

controller

Simple implementation

Watch D onmin

Proven to increase efficiency by ≈ 2%

RMS current of the snubber inductor

in a boost converter implemented in APFC

Two ways of snubber inductor (Ls ) connection:

Lm

Do

Lm

+ Vo

V in (ac)

Ls

i in

Co

Ro

Ls

Do

+V

o

V in (ac)

i in

S

Co

Ro

S

(a)

(snubber elements except Ls are not shown)

74

(b)

RMS current of the snubber inductor

in a boost converter implemented in APFC

Main assumptions

1.

The duration of transient processes after the switch S

is

turned on and after S is turned off are neglected.

2.

The input inductance Lm is sufficiently large that

their

current iin is practical constant during one

high

frequency switching cycle T s .

Under these conditions the current iLs of the snubber inductor

has a rectangular waveform during one high frequency

switching cycle Ts .

Vgs

t

iLS(Fig. a)

iin

t

iLS(Fig. b)

iin

ton

toff

Ts

For one switching cycle Ts (high frequency period)

I Ls rms hf (Fig. a) = i in D

75

t

I Ls rms hf (Fig. b) = iin 1-D

ton

where D = T

s

(hf - high frequency)

RMS current of the snubber inductor

in a boost converter implemented in APFC

Ideal APFC

Vo

v in

v in

i in

i in

Vo

I in m

V in m

ϑ

D

1.0

Dmin

ϑ

π/2

π/2

π

vin = V in m sinϑ

iin = I in msinϑ

where

ϑ =2πflft

(flf =50 or 60 Hz)

V o = const

In boost converter

76

(lf - low frequency)

Vo

1

vin = 1-D

where

Dmin =1-

-> D=1-(1-Dmin )sinϑ

V in m

Vo

RMS current of the snubber inductor

in a boost converter implemented in APFC

Ideal APFC (cont.)

RMS current for low frequency period

π

I Ls rms lf (Fig. a) =

1

I in m 2[sin2ϑ-(1-Dmin )sin3ϑ]dϑ =

π 0∫

= I in m

I Ls rms lf (Fig. b) =

4

0.5- (1-Dmin )

3π

π

1

I in m 2(1-Dmin )sin3ϑdϑ =

π 0∫

4

= I in m

(1-Dmin )

3π

77

I

LS rms lf

I in m

0.7

Fig. a

0.6

0.5

0.4

Fig. b

0.3

0.2

0.1

0.2

0.4

0.6

0.8

1

D min

Conclusion: Fig. a is preferable if Dmin <0.4 and Fig. b is

preferable if

Dmin >0.4.

78

Chapter 6

TURN-ON AND TURN-OFF SINGLE SWITCH SNUBBERS

79

TURN-ON AND TURN-OFF SINGLE SWITCH SNUBBERS

Possible Realizations:

LCC - one resonant inductor and two resonant capacitors

[10, 16, 22, 31, 32, 34, 39, 46]

LLC -two resonant inductors and one resonant capacitor

[1, 23, 29, 45]

LC - one resonant inductor and one resonant capacitor

[2, 22, 36, 41]

Generic LCC 'turn-off' & 'turn-on' snubber topology

(see also [32])

S type 'on'

Do

C1

A

Lo

D1

Ls

C

D3

D2

C2

D type 'off'

S type 'off'

L type 'off'

D type 'on'

S

B

B

• Snubber analysis is identical for all connections

80

TURN-ON AND TURN-OFF SINGLE SWITCH SNUBBERS

Boost converter with LCC snubber: D type 'on' and S type 'off'

(SNB8) [22, 31, 32]

(Modified turn-on snubber SNB7)

Lm

Do

Ls

+

Vin

S D1 +

C2 -

Vgs

-

+

+

C1

Iin

Vo

D2

Co Ro

D3

S - main switch

Do - main diode

D1, D2, D3 - auxiliary diodes

Lm

Ls

+

Do

Is

Iin

Vgs

Lm

+

+

Vin

-

Vo

Co

S

Ro

Ls

Iin

Vgs

S

t0 -t1

Vo

C1

Iin

Vin

-

Vgs

S D1

D2

Co

Ro

t1 -t2

Ls

+

+

C2 -

+

+

Vin

-

Lm

Vo

C1

D2

+

Co Ro

Lm

+

+

Vo

Iin

Vin

Co Ro

S

-

t2-t3

Vgs

t3 -t4

81

+

Lm

Lm

+

Vo

+

Iin

Iin

Vin

D1

-

Vin

Co Ro

+

Ls

C2 -

C1

D1

Lm

Vin

Iin

D3

C2

Co Ro

t5-t6

Ls

D1

+

+

-

ID1

-

t4 -t5

+

Vo

+

Vo

ILs

+

C

+ 1

D2

-

Lm

+

D3

Ls

Vo

+ C1

Iin

Vin

Co Ro

D3

-

t6-t7

t7-t8

Lm

Do

Ls

Vo

+

Iin

Vin

Co Ro

-

t8 -t9

Simulation

82

+

Co Ro

+

+

2.0V

Vgs

0V

8.0A

v(pulse)

iDo

-0.0A

25A

i(dout)

iD1

-5A

20A

i(d1)

iLs

-20A

500V

i(ls)

Vs

0V

25A

v(drain)

-5A

398us

400us

i(smain)

t1 t 2

is

402us

t3

404us

Time

406us

408us

t4 t5t 6 t

7

t8

Ts

t0

410us

t9

Interval t 0-t1

Vo

is = L t

s

ZCS!

dis V o

dt = Ls

iDo=I in -is

t1-to is found from the

condition: iDo(t1)=0

I in Ls

t1-to = V

o

vC1=0 ; vC2=V o

83

Interval t 1-t2

is =I in +i Ls

iLs =iC1=iC2=iD2=

Vo

sin[ωr12(tLs

C12

t1)]

where

C1C2

1

C12=C +C ; ωr12=

1

2

Ls C12

C2

vC1=V oC +C {1-cos[ωr12(t-t1)]}

1

2

vC2= C2

C1

vD1=V oC +C {1+C cos[ωr12(t-t1)]}

1

2

2

t2-t1 is found from the condition:

vD1(t2)=0

C2

1

t2-t1=

cos -1(-C ) = Ls C12cos -1(1

ωr12

C2

C1)

iDo=iD1=iD3=0

84

Interval t 2-t3

is =I in

V C1(t2)

iLs =iC1=iD1=iD2=sin[ωr1(t-t2)]+i Ls (t2)cos[ωr1(tLs

C1

t2)]

where

1

Ls C1

t3-t2 is found from the condition:

iD1(t3)=iD2(t3)=0

Ls

iLs (t2) C

C1-C2

1

1

1

t3-t2= tan-1( v (t ) ) =

tan-1(

C2 )

C1 2

ωr1

ωr1

Ls

vC1=vC1(t2)cos[ωr1(t-t2)]+i Ls (t2) C sin[ωr1(t1

t2)]=

C2

C2(C1=V oC cos[ωr1(t-t2)]+V o

1

C2)),C1)sin[ωr1(t-t2)]

C2

vC1(t3)=Vo C

1

Interval t 3-t4

is =I in

iDo=iD1=iD2=iD3=0

vDo=-Vo

C2

vC1=vC1(t3)=Vo C

1

(C2<C1)

vC2=0

Interval t 4-t5

is =0

iD1=I in

I in (t-t4)

dvs I in

vs =vC2= C

dt = C2

2

ωr1=

ZVS!

85

C1=vC1(t3)=V o

C2

C1

vD3=vC2+vC1-V o

t5-t4 is found from the condition:

vD3(t5)=0

V oC2(1t5-t4=

I

C2

C1)

in

Interval t 5-t6

is =0; iDo=iD2=0

C1 C2

iD1=I in C +C {C +cos[ωr12(t-t5)]}

1

2

1

C2

I in

C1

vC2=V o(1- C )+

{ωr12(t-t5)+ C sin[ωr12(t-t5)]}

1 ωr12(C 1+C 2)

2

Two operating modes are possible. They depend on the

condition at t6 of the interval t5-t6:

Mode 1 will prevail if :

(vC2)t6 = V o

(iD1)t6 > 0

Mode 2 will prevail if :

(iD1)t6 = 0

(vC2)t6 < V o

Vo

C2

Necessary condition for Mode 1: I

Ls < kC

in

C2

C1 2

1

where :

kC=

[cos -1(-C )+ (C ) -1]

1

2

C2

C1

(1+C ) C +1

1

2

86

3.5

3.0

kC

2.5

2.0

1.5

1.0

0

2

4

6

C1/C2

8

10

12

C1

The dependence of kC on C

2

Vo

C2

• For Mode 1: I

Ls < kC

in

87

t6-t5 is found from the condition: vD2(t6)=0; vC2(t6)=Vo

Interval t 6-t7 ,

Mode 1,

is =0; vs =V o

iD3=I in

iD1=iD2=I in -iLs

V C1(t3)

iLs =

sin[ωr1(t-t6)]

Ls

C1

t7-t6 is found from the condition:

iD1(t7)=iD2(t7)=0

t7-t6=\f(1,ωr1)sinLs

Ls

I in C

I in C

1

1

2

1(

-1

vC1(t3) ) =ωr1sin ( V o )

Interval t 7-t8 ,

Mode 1,

is =iDo=iD1=iD2=0; iD3=I in

vC1=vC1(t7) -

I in (t-t7)

C1

t8-t7 is found from the condition:

vC1(t8)=0

vC1(t7)C1

t8-t7= I

in

vs ≈ V o-vC1

88

Interval t 8-t9 ,

Mode 1,

is =iD1=iD2=iD3=0;

iDo=I in

vs ≈V o ;

vC1=0 ; vC2=V o

LOSSLESS TURN-ON AND TURN-OFF SNUBBER (SNB8)

Mode 2. Time interval before the switch Q is turned on

Lm

+

Iin

D1

Vin

-

Vgs

Do

Ls

S

ILs

Vo

C1

D2 ID

D3

Co Ro

• Three auxiliary diodes are conducting

• Hard switching

• Coupling will help to avoid Mode 2.

TURN-ON TURN-OFF SNUBBER (SNB8)

Typical Design

diS

dvS

Given: Vo, Iin , ( dt )

, ( dt )

, Dmin , Dmax

t0-t1

t4-t5

89

+

Vo

1. Ls ≥ di

S

( dt )

t0-t1

3. kC

>

I in

2. C2 ≥ dv

S

( dt )

t4-t5

Vo

I in

C2

Ls

> 1

C1

4. Select C1/C 2 using the plot kC=ϕ(C ).

2

I in Ls

5. ton min = V +

o

V C

6. toff min ≈ o 2 [1+

I in

7. Dmin =

C2

Ls C12cos -1(-C ) + Ls C1tan-1(

C1-C2

C2 )

1

I in 2Ls

C1

C2(1-V o2 C2)] +

Ls C1sin -1(

(ton min ) fs ; Dmax =(1 - toff min ) fs

8. Current stress of the switch S

C12

Is pk=I in +V o

Ls

9. Voltage stress of the switch S

Vs pk = V o

Apply iteration to approach desired design goals

90

Ls

C2

Vo )

I in

91

Some Additional Recent Turn-On & Turn-Off

Passive Lossless LCC Snubbers

Do

S type 'on'

D3

C1

D2

A

Lo

C

D1

Ls

D type 'off'

S type 'off'

L type 'off'

C2

D type 'on'

S

B

B

• Generic LCC 'turn-off' & 'turn-on' snubber topology

SNB8 discussed above (drawn differently)

Boost converter with LCC snubber: D type 'on' and S type 'off'

Do

Vo

C1

D3

D1

D2

Lr

Vin Lin

+

-

Vgs

S

C2

92

Co

Ro

Moving the connection point to main inductor

Boost converter with LCC snubber: S type 'on'

and S type 'off' (SNB9) [16, 32, 39]

Do

+

Lin

Vin

-

Cr

Lr

Vgs

D1

S

Vo

D3

D2

Co

Ro

C1

Topologies similar to SNB8 and SNB9

with different capacitor C2 connections [31, 32, 34, 46]

Lm

+

Do

Ls

C1

Iin

+

Vin

-

Vgs

S D1 +

C2 -

D2

Original

93

Vo

D3

Co Ro

+

SNB10: D type 'on' and D type 'off' [34, 46]

Lm

Do

Ls

+

+

C1 -

k

D1

V in

D2

S

V gs

-

+V

o

D3

- +

Co

Ro

C2

b

C2 connected to output

Ripple to output

SNB11: D type 'on' and L type 'off' [32]

Lm

+

Do

Ls

D1

+

C

- 2

V in

+

k

C1 D2

+Vo

D3

S

-

Co

V gs

b

C2 connected to input

94

Ro

Ripple stired to input

95

SNB12: D type 'on' and L type 'off' [31]

Lm

Do

+

Ls

+C

- 1

D3

V in

S

V gs

-

D2

- +

+Vo

D1

Co

C2

Ro

b

C2 connected to switch

Stirs ripple to output

Generic LCC 'turn-off' & 'turn-on' snubber topology

with improved reset

S type 'on'

Do

D3

Vres

D2

D1

C2

C

C1

A

Lo

Ls

D type 'off'

S type 'off'

L type 'off'

D type 'on'

S

B

B

96

• V res accelerates the reset phase

97

Turn-on and turn-off snubber for single switch

converter

Improved Williams snubber SNB13 [10]

C

Do

D3

D4

A

Lo

C1

L1

D2

D1

S

C2

B

Operating process is based on a dual energy recovery

circuit, improvement on SNB9.

• V res replaced by transformer

Claimed to have:

1. Lower peak current in the switch S.

2. Shorter discharge time is needed for the capacitor C1 at

low load . Hence, wider operation range of load current and

higher switching frequency.

Reset through transformer (leakage and reset problems ?)

See also snubbers with recovery transformers

[11-13]

98

Boost converter with LLC-type snubber (SNB14)

[1, 23, 45]

Lr1

D1

Vo

+

L1

Lr2

D2

L2

D4 Co

Cr

Vin

-

D3

Ro

S

Vgs

Coupled inductor

2.0V

0V

Vgs

v(pulse)

50V

Vc

r

10V

v(vcr,drain)

7.0A

-0.0A

iL r1

i(lr1)

7.0A

-0.0A

iL r2

i(lr2)

50V

0V

Vs

v(drain)

7.0A

-0.0A

492us

i(smain)

is

494us

496us

498us

Time

Basic waveforms of SNB14

99

500us

SNB14 Features

Pro

1. Soft switching at turn-on and turn-off in a wide load range

without high current and voltage stresses.

2. Coupling decreases the minimal needed value of turn-off

time of the switch.

Con

1. The resonant circuit L1Cr is fed from the input voltage

V in . Hence, the peak capacitor's voltage cannot be higher

2V in . Consequently, when Vo>2V in => hard switching.

Buck converter with LC type snubber (SNB15) [2, 36]

(one inductor and one capacitor)

Lr

S

+

D1

Vin Vg

-

Cr

Do

Cf

Ro

D2

Lf

Io

• No common ground !

See boost converter with LC type snubber in [41]

100

Vo

2.0V

0V

2.0A

0A

Vg

v(pulse)

iL r

i(lr)

70V

Vcr

-40V

2.0A

0A

100V

v(vcr)

is

i(smain)

Vs

0V

488us

490us

v(in)-v(in2)

492us

494us

496us

498us

500us

Time

Waveforms of SNB15

{'Turn-on'}, {'turn-off'} and {'turn-on' - 'turn-off'}

snubbers

Can parasitic elements be used ?

1. 'Turn on'

A

Do

C

Lo

Ls

S

B

dI

• Ls relatively large inductance to lower dt and hence

diode peak reverse current and trapped energy

• Need a mechanism for recovering trapped energy

Impractical to obtain by stray inductance such as

interconnections

Can be part of transformer or flyback coupled inductor

101

2. 'Turn off'

A

C

Do

Lo

Cc

S

B

dV

• Cc significant inductance to lower dt

• Cc is mainly needed while voltage on switch is low

Switch output capacitance would be helpful and

sometime sufficient

2. 'Turn off' - cont.

If internal capacitance is used:

•

fast gate 'turn off'

•

high sink current

•

low source inductance "fast switch"

Look up new MOSFET generations (APT V)

102

Output Capacitance of MOSFETs

A study by Simulation

• Nested AC analysis

• V 1 is swept from 0V to 100V

• I ac is set to 1A (not to worry, used after linearization)

• Capacitance is calculated from:

1

C out = 2 π frequency v

ds

'frequency' -> PSPICE variable

C out

V DS

C out

Upper trace: Cout as a function of VDS

Lower trace: Cout as a function of frequency for various VDS

values.

• About 1 nF at 50V

• For significant improvement added snubber capacitance >

1nF

103

Simulating Snubbing Effects

'turn-off'

• Transient analysis

• C is swept 0nF - 10nF

C=0

Drain clamped to 100V

Drain clamped to 20V

• Drain current reflects charging of internal capacitor

C V2

• Part of energy stored as

--> losses at 'turn-on' !

2

• Not all of {I D*V DS} at 'turn off' duration is lost to heat

104

C = 0 & 1nF

• Small part of current channeled to snubbing capacitor

C = 0 &10nF

• Current channeled to 10nF capacitor

• Internal capacitor still charges to the same voltage !

105

106

Chapter 7

RECTIFIER DIODES LOSSLESS SNUBBERS

PHASE SHIFTED PWM (PSPWM) [18, 19, 27]

ZVS of main switches

+

Q

1

Vin A

Q2

-

C1

C4

L1

Q4

B

C2

Q3

C3

Cc

T

Lo

Co Ro Vo

Basic Phase Shifted PWM Stage

• Leading and lagging legs (bridge non-symmetrical)

• Coupling capacitor Cc needed to block current

• Asymmetry of control (+noise !)

• Can be eliminated by applying peak current mode

control

107

+

Q

1

Vin

C1

Q2

-

C2

L1

C4

Q4

C3

Q3

Do1

T

Lo

Lm

Do2

Co Ro Vo

Stage 1 - Powering

+

Q

1

Vin

Q

2

-

C1

L1

C2

C4

Q

C3

Q3

T

4

Do1

Lo

Lm

Do2

Co Ro Vo

Stage 2 - Power to toff transition - capacitor charge

108

+

Q

1

Vin

C1

Q2

-

C2

L1

C4

Q

C3

Q3

T

4

Do1

Lo

Lm

Do2

Co Ro Vo

Stage 3 - Power to toff transition - Diode catch

+

Q

1

Vin

C1

Q2

-

C2

L1

C4

Q4

C3

Q3

T

Do1

Lo

Lm

Do2

Co Ro Vo

Stage 4 - toff (circulating current)

109

+

Q

1

Vin

C1

Q2

-

L1

C2

C4

Q4

C3

Q

3

Do1

T

Lo

Lm

Do2

Co Ro Vo

Stage 5 - toff to Power Transition

+

Q

1

Vin

C

1

Q2

-

C2

L1

C4

Q

C3

Q

3

4

Do1

T

Lo

Lm

Do2

Co Ro Vo

Back to Power Mode

t off

VAB

IL 1

td

ID

o1

ID

o2

t0

t1

t 2 t 3 t4

t5

t 6 t7 t 8

t

Waveforms

✎ Two rectifier diodes are conducting during toff

110

PSPWM DESIGN OVERVIEW

Basic Conventional Phase Shift PWM design equations

2 L

Ioff

r

(CA + CB )V 2BUS

2

2

CA +C B = total leg capacitance

≥

or:

Ioff

Lr

> V BUS ==> Ioff Zr > V BUS

C A + CB

where the characteristic impedance is defined as usual:

Zr =

Lr

C A + CB

The transition time (need to be larger than 1/4 of the resonant

period

td ≥

2π Lr (C A + CB )

4

In the conventional scheme, L1 need to be relatively

large to store sufficient energy at low load current .

This can be somewhat improved by making the primary

current larger (lower Lm transformers magnetization

inductance) .

If the short circuit ( two diodes conducting) during toff

is avoided (only one diode conducts ) L1 can be small

since the energy comes from the secondary

111

+

Q

1

Vin

C

1

Q

2

-

C2

L1

C4

Q

C3

Q3

4

Do1

T

Lo

Lm

Do2

Co Ro Vo

Stage 5 - toff to Power Transition - two diodes conducting

+

Q

1

Vin

C1

Q

2

-

C2

L1

C4

Q

C3

Q3

T

4

Do1

Lo

Lm

Do2

Co Ro Vo

Stage 5 - toff to Power Transition - one diode conducting

If only one diode conducting ==> L1 id not needed

112

RESIDUAL ISSUES IN PSPWM

1. Circulating Current

Circulating Current Losses

Primary current

• Thermal design of power stage for duty cycle D ==>1

=>The circulating current at D < 1 not a major

problem

• Possible Solution

Apply the 'One Way' capacitor to block primary current at toff

+

Q

1

Vin

Q2

-

C

1

L1

C4

Q4

C3

Q3

C2

T

Lm

Do1

L o

Do2 Ds2

Cs2

L r D s1 C

s1

Co Ro Vo

Ds3 D o3

Lossless output snubber SNB16 [18]

• L r and C s form a resonant circuit

113

+

Q

1

Vin

Q2

-

C

1

L1

C4

Q4

C3

Q3

C2

T

Do1

L o

Lm

Do2 Ds2

Cs2

L r D s1 C

s1

D o3 Co Ro Vo

Ds3

Modified lossless output snubber SNB17 [19]

Resonant inductor can be moved to primary

Bridge

voltage

Primary

current

Rectifier diode

current

Rectifier diode

current

Basic waveforms of SNB17 (Simulation)

• Suitable for IGBT (zero current at toff combats current tail)

114

RESIDUAL ISSUES IN PSPWM

2. Rectifier's diodes reverse recovery

Llkg

1

+

Llkg

2

CO

Leakage inductance at secondary

Diode voltage

Voltage at input to

filter inductor

Experimental waveforms

• Greatly influenced by transformer leakage

115

RO

RESIDUAL ISSUES IN PSPWM

2. Rectifiers' diodes reverse recovery

• Possible Remedy -> Saturable reactor (SR) [7, 8, 9, 14,

43]

B

Operating

point

∆B

H

V=-400v

L sr

I=5A

150

MUR860 R

s

D

Cs

0.5nF

Simulation Circuit

• Using fast diode

• Current source establishes the forward current and abrupt

change

• L sr emulate "large" back inductance

116

0.1KV

Diode voltage

SEL>>

-1.0KV

v(dd)

7.0A

Current source

0A

i(ipulse)

6.0A

Diode current

-5.0A

0s

i(dout)

100ns

200ns

300ns

400ns

500ns

Time

Exit

File

Add_trace Remove_trace

X_axis

Macros

Hard_copy Cursor Zoom

Y_axis

Label

Plot_control

Display_control

Simulation waveforms (Lsr = 50µH)

RESIDUAL ISSUES IN PSPW

2. Rectifiers' diodes reverse recovery

• Design equations overview

Magnetic flux swing (one sided)

VT

∆B = 2 n A

c

VT = volt-second across SR

A c = core effective cross section area

n= number of turns

For Amorphous Alloy 2714AF (Allied):

Core Losses : Pcore (W/Kg, mW/gr)) = 10-6 (fs )1.73 (∆B)1.88

B = Magnetic flux (T) ; fs = Switching frequency (Hz)

∆B=(Pcore/(10-6 (fs )1.73))(1/1.88)

117

Amorphous Alloy 2714AF (Allied)

CORE LOSS (W/Kg, mW/g)

103

350KHz

300KHz

250KHz

200KHz

150KHz

100KHz

100

50KHz

10.0

1.00

0.100

0.0100

0.01

0.1

∆Β

1

[Τ]

Extrapolated from Allied's data (originally given up to

200KHz)

RESIDUAL ISSUES IN PSPWM [42, 43]

2. Rectifiers' diodes reverse recovery

• Implementation in PSPWM

Q

1

C1

C3

Q4

Q2

C2

C4

Q3

Vin

T

Co Ro Vo

PSPWM with SR at output (SNB18)

118

RESIDUAL ISSUES IN PSPWM

2. Rectifiers' diodes reverse recovery

• Implementation in PSPWM

T

SR1

Vc

Io

I1

Ic

SR2

n:1

Situation at first commutation instance (power to toff )

SR1

n2 C

Co

- V2

SR2

Equivalent circuit during toff

RESIDUAL ISSUES IN PSPWM

• Theoretical considerations

SR1

Vc

I

I1

I2

c

Io

SR2

n:1

toff

T

Vc

I

SR1

I1

I2

c

Io

SR2

n:1

toff release

119

Ro

T

_

Vc

I1

I2

Ic

+

SR1

Io

SR2

n:1

toff to Power transition

T

_

I1

I2

Ic

+

SR1

Io

SR2

n:1

Transition end (SR1 blocks reverse recovery current)

Do1

Current

Voltage

across SR1

Voltage

across SR2

Current through rectifier leg and voltage across SR

120

VT across SR1 (1 VuS/div)

Voltage across SR1

Current of Do1

Volt Second of SR

Design Guidelines

1. Choose SR to keep core losses low say : 50 mW/gr

2. Estimate VT

Example:

Diode reverse voltage 100V

trr ≈ 100 nSec

=> V T ≈ 10 VµS

For Amorphous Alloy 2714AF (Allied):

Pcore (W/Kg, mW/gr)) = 10-6 f1.73 ∆B1.88

Assume Pcore = 50 mW/gr; f = 270KHz

121

Amorphous Alloy 2714AF (Allied)

103

CORE LOSS (W/Kg, mW/g)

350KHz

300KHz

250KHz

200KHz

150KHz

100KHz

100

50KHz

10.0

1.00

0.100

0.0100

0.01

0.1

∆Β

1

[Τ]

From loss equation => ∆B = 0.125T

VT

From ∆B = 2 n A

=> Ac = 0.4 cm 2

c

Using MP1906P-4AF (Allied):

OD = 21mm; ID = 10mm; Ac = 0.16 cm2; n=1; 6.1 gr

Need at least 3 units per leg

Effective frequency is much higher than switching

frequency

Being a small body (small surface area), might get

very hot. 4 units per leg were used in experimental

converter.

Experimental PSPWM Converter

Transformer: Payton 3000W T250-12-4C

Nominal Operating frequency = 350KHz

Input Voltage = 360 -390 Volt

Max. VT = 864 VµS

122

Primary to half secondary 6:1

Primary Max rms current: 11 Amp

Dielectric strength (primary to secondary) 2500 Vrms

Dielectric strength ( secondary to core ) 500 Vdc

Estimated power loss 65W (@ 600C base plate)

Estimated hot spot 1100C

Mechanical dimensions 88*65*30(h) mm

123

+

Q

1

2250µF

2x

0.047 µF

Q4

Vin

Q2

Q3

L s1

T1

Do1

Lo

3.6µH

T250DC-12-4C

L s2

Do2

Co2

C o1

10µF 220µF

L s1 , Ls2 - 4 x MP1906P-4AF

Experimental power stage

124

Ro

Experimental Results

Primary current (upper) and leg voltages (lower)

Bridge output

voltage

Transformer

primary

voltage

Primary current

SR Voltage

Rectifier diode

current

Primary

current

In circuit SR Performance`

Rectifier diode

voltage

SR Voltage

Rectifier diode

current

Leg voltage

SR VT

( 10 V µ S/Div)

SR Voltage

Leg voltage

125

Experimental Results

Diode voltage

Voltage at input to

filter inductor

Experimental waveforms (no SR snubber)

Rectifier diode voltage (upper trace) and current (lower)

with amorphous core

• Some overshoot due to energy stored in SR

126

Improved magnetic snubber for rectifier diodes

in DC/DC converters

+

Cin1

C1 D1

Cin2

C2 D2

Q1

Vin

-

Q2

T1

SR1

D5

SR2

L1

D3

D4

Lo

Co

• Basic solution [42,43]

127

Ro

Vo

Dependence on L - Simulation

Idiode

Idiode

Diode reverse recovery switching waveforms

Actual reverse recovery time is a function of series

inductance

B

Operating

point

∆B

H

Long reverse recovery time will increase core losses

128

Improved magnetic snubber for rectifier diodes

in DC/DC converters [44]

+

Cin1

C1 D1

Cin2

C2 D2

Vin

-

Q1

Q2

T1

SR1

D5 L1

C3

L2

D3

SR2

D6

D4

C4

Lo

Do

Co

Ro

Vo

Added elements: C3, C 4, Do, L1 D5 & L2 D6

-> Extra resonant circuit to sweep out stored charge

D5

C3 +

D3

L1

L2

iL

iL

1

2

D6

D4

-

C4

+

Do

Do

The stored charge of the diode D3 (D4) is pulled out rapidly ;

therefore (trr ) D3 and (trr ) D4 desrease and hence core losses

in SR1 and SR2 also reduce.

129

Chapter 8

COMBINING SNUBBER AND POWER SUPPLY

FUNCTIONS

Turn-off snubber with energy recovery

back to the input bus or into a local power supply

(SNB20) [39]

Vin

Load

D0

C

+ S

D2

L

SMPS

Vin

+ Co

D1

just after S is turned off

just after S is turned on

C = Snubber capacitor

Co = Filter capacitor

Negative polarity of voltage across Co !

• The main purpose of the device: turn-off snubber

• Additional appointment: local power supply

Watch for power level (in PS applications), might be

too high

130

A local power supply with turn off snubber features

[47]

Lin

Do

+

Cgd

Vin

Q

C

- gs

C1

Cds

Vo

L

Co

D2

C2

VS

DZ RS

Ro

D1

LPS

LPS - local power supply

Rs - load resistance

C2 >> C1; DZ - Zener diode

• Positive polarity of output voltage V s

• The main purpose of the device: A local power supply.

Secondary objective: turn-off snubber

A local power supply with turn off snubber features

Main assumptions of analysis

1. Ideal diodes and ideal transistor. Parasitic capacitences of

MOSFET are taken into account. It is assumed that

these capacitences are linear.

2. Lin, Co and C 2 are infinitely high

131

Equivalent circuits

Iin

Do

+

C1-

Ic

+

-

D2

CQout

C2

Vo

RS

DZ

• t0-t1: energy injection into LPS

Equivalent circuits

Iin

Do

+

-

C2

Vo

RS

DZ

• t1-t2: no interconnection between the processes in the LPS

and in the converter

132

Equivalent circuits

C1

+

-

L

IL

C2

RS

D1

DZ

t2-t3: energy transfer from the capacitor C1 to the inductor L

L

D2

IL

C2

RS

D1

DZ

• t3-t4: energy transfer from the inductor L to the C2 - D2 - Rs

circuit

Current and voltage waveforms

vC1

400V

-15V

t

iQ

11A

0A

t

iDo

11A

0A

t

IC1m

4A

-6A

6A

0A

VS

Vo-VS

t

4

iC1 ILm

iL

8

12

Time

t0 t1

t2 t3

133

t4

t

[µS]

Proposed Local Power Supply (LPS) connected in

a boost converter

Main relationships

Energy injected to LPS during one switching period

C V2

E = 1 o = Vs (Is + I Z )T s

2

V2

I s + I Z = f sC1 o

2V s

V2

I s max = f sC1 o

2V

s

(when IZ=0)