Original Input Stage – frequency response

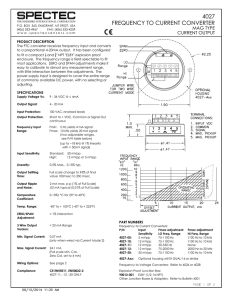

advertisement

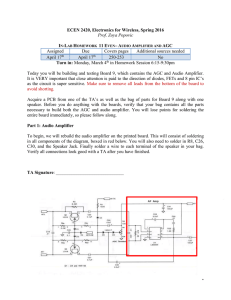

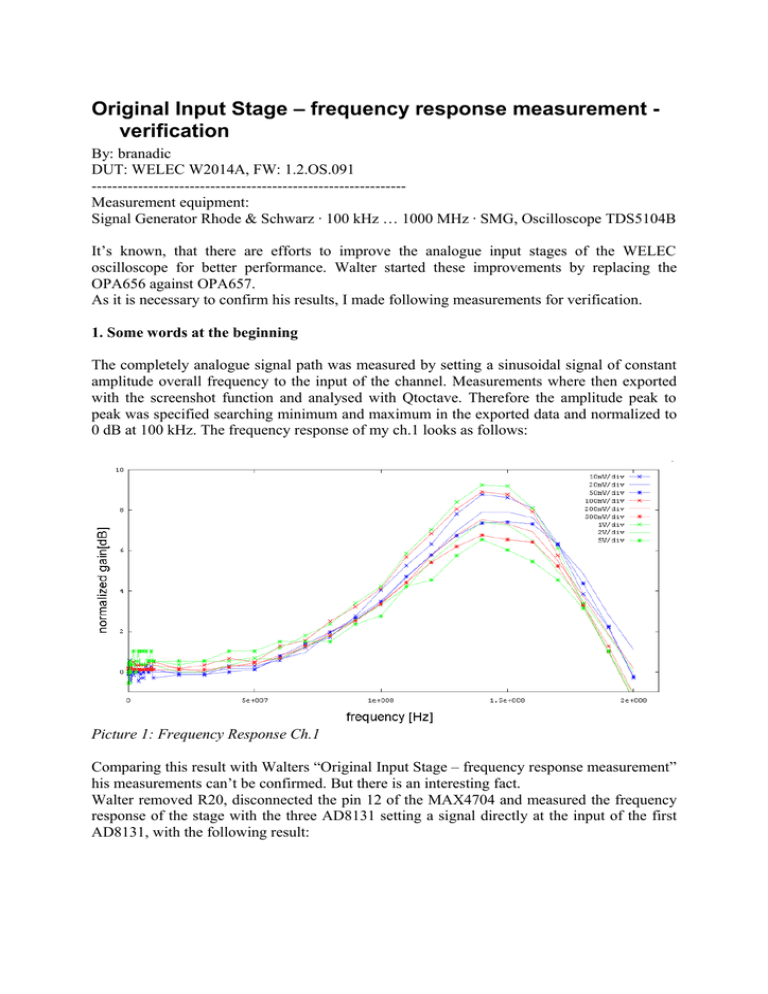

Original Input Stage – frequency response measurement verification By: branadic DUT: WELEC W2014A, FW: 1.2.OS.091 ------------------------------------------------------------Measurement equipment: Signal Generator Rhode & Schwarz · 100 kHz … 1000 MHz · SMG, Oscilloscope TDS5104B It’s known, that there are efforts to improve the analogue input stages of the WELEC oscilloscope for better performance. Walter started these improvements by replacing the OPA656 against OPA657. As it is necessary to confirm his results, I made following measurements for verification. 1. Some words at the beginning The completely analogue signal path was measured by setting a sinusoidal signal of constant amplitude overall frequency to the input of the channel. Measurements where then exported with the screenshot function and analysed with Qtoctave. Therefore the amplitude peak to peak was specified searching minimum and maximum in the exported data and normalized to 0 dB at 100 kHz. The frequency response of my ch.1 looks as follows: Picture 1: Frequency Response Ch.1 Comparing this result with Walters “Original Input Stage – frequency response measurement” his measurements can’t be confirmed. But there is an interesting fact. Walter removed R20, disconnected the pin 12 of the MAX4704 and measured the frequency response of the stage with the three AD8131 setting a signal directly at the input of the first AD8131, with the following result: Picture 2: Frequency Response of AD8131 stage measured by Walter As you can see, the characteristic looks nearly the same as above. In further measurements, after replacing the OPA656 against OPA657, Walter showed the influence of a ~50 kHz signal which was superimposed on his measured input signal. I could find out that this signal comes from the inverter part of the TFT-LCD. Both wires (pink/white) radiate and an influence by capacitive coupling can’t be excluded. More probably this result is an influence of inductive coupling. Walter removed the shielding of channel 1. Close to this channel are two inductances and a bulky circuit path of the inverter. Measurements with a DIY sampling probe for magnetic fields showed radiations that could couple into the input stage and influence the signal dramatically. For the validation of Walter’s improvement I decided to make all measurements on channel 3, because first measurements on all channels showed, that ringing by the value of the adc_change12_reg in FW1.2.OS.091 is still present on channel 4. Channel 3 is furthermore far away enough from the influence of the inductance and easy to reach for modification. 2. Complete signal path of Channel 3 – original input stage First of all, I characterized the completely analogue signal path of the channel, to see what is “The base of operations”. Measurements were made with a 50 ohms load resistor at the input of channel 3 for matching the output of the signal generator. Picture 3: Frequency Response Ch.3 3. Reduced signal path of Channel 3 – original input stage After removing R20 and disconnecting the MAX4704 - I found it easier to disconnect the input pin 8 of the AD 8131 from the rest of the circuit, to isolate it and set the signal directly to this pin instead of cutting the signal path to the MAX4704 or to de-solder the pin 12 of the MAX4704 - measurements were repeated setting the sinus signal of constant amplitude through a coax cable directly to the input of the first AD8131. In the following graphic the frequency response of the AD8131 stage can be seen. Picture 4: Frequency Response of the AD8131 stage This result is similar to the results of Walter's measurements. The frequency response is probably an effect of the used analogue switches NC7SBU3157P6X forming filters in the different gain stages. A device depending effect is hereby excluded. Scale factor OPA656 1st AD8131 2nd AD8131 3rd AD8131 Complete gain 50mV/500mV/5V 1,25 2 1 1 2,5 20mV/200mV/2V 1 2 1 2 4 10mV/100mV/1V 1 2 2 2 8 4. Noise So the question is, what about noise? To better assess the results, take a look at the table above. Together with the values for the input signal noise can be discussed. input signal: range 1 → 5.01mV (amplitude of Ueff) = 2·sqrt(2)·5.01 mV ≈ 14.17 mVpp range 2 → 10mV (amplitude of Ueff) = 2·sqrt(2)·10 mV ≈ 28.28 mVpp range 5 → 35.1mV (amplitude of Ueff) = 2·sqrt(2)·35.1 mV ≈ 99.28 mVpp resulting signal at ADC: range 1 → 14.17 mVpp·2·2·2 ≈ 113.36 mVpp range 2 → 28.28 mVpp·2·2·1 ≈ 113.14 mVpp range 5 → 99.28 mVpp·2·1·1 ≈ 198.56 mVpp Picture 5: readout of the device memory (8k) Noise can be extracted by searching for min and max in the data. With the following expression the digital bit values are converted to analog voltage values: analogue_voltage = (255 – digital_value -128) · 0.625 / 256 The first part of the expression (255 – digital_value) mirrows the digital values, because while data correction signal is mirrowed in the memory. The – 128 sets the signal around zero line. The last expression converts the data into analogue voltage. Extracted voltage peak-peak: range 1 → 129.39 mVpp range 2 → 122.07 mVpp range 5 → 202.637 mVpp If we now subtract the resulting signal at ADC from the extracted voltage peak-peak we get the noise in mVpp by the AD8131 gain stage. Noise: range 1 → 129.39 mVpp - 113.36 mVpp = 16.03 mVpp range 2 → 122.07 mVpp - 113.14 mVpp = 8.93 mVpp range 5 → 202.637 mVpp – 198.56 mVpp = 4.077 mVpp 5. Result The frequency behaviour and noise of the AD8131 stage shows that further improvement without touching the AD8131 gain stage makes no sense and gives different options: − no more touching the hardware, just improving firmware and VHDL − piggyback board with optimised gain stage − further, a complete new analogue/FPGA board The last both option necessitate that optimisation starts at the AD8131 gain stage, before the OPA656 can finally be replaced by OPA657. This stage could be replaced by a programmable amplifier, such as LMH6515 or AD8670. Therefore a separate board needs to be designed. Replacing the OPA656 by OPA657 is still necessary, because the first stage should have maximum gain, to increase SNR. OPA657 could be set fixed to gain = 10. At least there are three usable control wires, one at the OPA656 switching between gain = 1 and gain = 1,25 and two at the switches of the AD8131 gain stage. This control wires could be used, supported by the firmware, to control the gain of a programmable amplifier. branadic