2-Port USB 3.0 Hub Reference Design

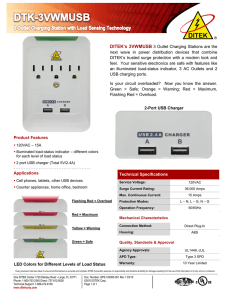

advertisement

TI Designs TIDA-00287 2-Port USB 3.0 Hub Reference Design TI Designs Design Features TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help you accelerate your time to market. TPD6E05U06 TUSB8020B TPS2553 IEC ESD Protection Diodes 2-Port USB Hub Power Distribution Switch The TIDA-00287 is a fully functioning 2-port USB 3.0 hub: • Supports individual port power control • ESD protection on both upstream and downstream ports • Operates as a bus-powered device (all power being supplied by the upstream host or hub) • Supports operation as a USB 3.0 and USB 2.0 device TLV70033 LM3674 LDO Linear Regulator 600-mA Buck Converter Featured Applications ASK Our Analog Experts WEBENCH® Calculator Tools • • • • Design Resources Computer systems Docking stations Monitors Set-top boxes 3.3 V spacer1 spacer1 spacer1 spacer1 spacer1 spacer1 spacer1 spacer1 spacer2 spacer3 spacer4 spacer5 1.1 V spacer1 spacer1 spacer1 spacer1 spacer1 spacer1 spacer1 spacer1 spacer2 spacer3 spacer4 spacer5 An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information. All trademarks are the property of their respective owners. TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 1 Circuit Description 1 www.ti.com Circuit Description The USB 3.0 Hub Design is a two-port USB 3.0 compliant hub. It provides simultaneous SuperSpeed and high-speed/full-speed connections on the upstream port and provides SuperSpeed, high-speed, fullspeed, or low-speed connections on the downstream ports. The hub design provides power control for each downstream port and overcurrent protection 2 Theory of Operation A block diagram of the design in Figure 1 shows a USB 3.0 Hub with a Type A plug upstream port and two USB 3.0 Type A downstream ports. Power for the design is shown as well as ESD protection elements on the upstream and downstream sides of the hub. Downstream port current limiting is provided by two TPS2553 (Adjustable Current-Limited Power-Distribution Switch) devices. 3.3 V 1.1 V Figure 1. TIDA-00287 Functional Block Diagram 2.1 TUSB8020B The TUSB8020B is a two port USB 3.0-compliant hub device. It provides SuperSpeed and high/full speed connections on the upstream port. It also supports SuperSpeed, high/full speed or low-speed connections on the downstream ports. When the upstream port is connected to an environment that supports only high-speed or full-speed/low-speed connections, SuperSpeed is disabled on the downstream ports. When the upstream port is connected to an environment that supports only full-speed/low-speed connections, SuperSpeed and high-speed are both disabled on the downstream ports. The hub supports overcurrent protection and battery charging as well as either ganged switching or per port power switching. The USB 3.0 hub is configured with the de-assertion of RESET. Refer to Table 1 for the default values. Table 1. TUSB8020B Power-on Reset Settings 2 TUSB8020B Function Status Downstream port power management Enabled Power control signal polarity Signals are active high Power port control Ganged Power control supported TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback Theory of Operation www.ti.com 2.2 System Power The main power on the board is 5 V and is supplied by the upstream USB port. Figure 2 shows the configuration of the board’s power system. The 5 V coming from the upstream USB port is regulated down to 3.3 V through a TLV70033 LDO regulator. An LM3674 switching regulator is used to supply 1.1-V power for the core voltage to the TUSB8020B. The 5-V power is also passed to the TPS2553 currentlimiting switches that supply power to the down-stream ports. +3.3 V +1.1 V Figure 2. Power Subsystem 2.3 Downstream USB Power Delivery USB power for downstream ports is provided by two TPS2553 (Adjustable Current-Limited PowerDistribution Switch). These switches are controlled by the USB hub chip, and have adjustable current limits on the outputs. This design is set for a current limit of 901.5 mA (typical). BOARD_5V C50 0.1uF 0402 C45 4.7uF 0402 U17 1 2 [P3] EN_PORT1 3 EN_PORT1 ACTIVE HIGH ENABLE: R27 47K 0402 IN OUT GND ILIM EN FAULT# TPS2553 SOT23_6 6 VBUS_OUT_PORT_1 VBUS_OUT_PORT_1 [P4] 5 4 FLT_PORT1# R28 28.7K 0402 FLT_PORT1# [P3] C49 22uF 0603 THIS SETS THE CURRENT LIMIT TO 901.5mA (TYP) Figure 3. Downstream Power Delivery 3 Component Selection All components contained in this design are chosen to provide a low-cost solution when purchased in large quantities, while minimizing component count and maintaining performance to satisfy the design criteria. 3.1 Hub Selection The TUSB8020B was chosen as a low cost 2 port USB 3.0 hub. It supports both USB 3.0 and USB 2.0 for both upstream and downstream ports. Battery charging can be supported as can be per-port or ganged power switching. An OTP ROM is included for custom 3rd party VID/PID and device configuration. There are no special drivers required for this hub. TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 3 Component Selection 3.2 www.ti.com Downstream Power Switches This design uses two TPS2553 current-limited power distribution switches. These parts have adjustable current limits that can be set by an external resistor. Both ports have been designed to deliver ~900 mA. It should be noted that some USB 3.0 ports can supply far in excess of the minimum 900-mA current. If the upstream USB 3.0 port that the hub is plugged into can provide in excess of 1.8 A, then both downstream ports will support the full 900 mA of current. 3.3 ESD Components ESD protection for all USB ports is supplied by the TPD6E05U06 devices. This part provides ESD protection for 3 differential pairs at data speeds of up to 6GBps and has low capacitance of 0.5 pF. Each USB port uses one of these parts to protect the port. The package allows for straight through routing and is placed as close to the USB connector as possible. Application of ESD protection is recommended. 3.4 2-Port Power The main power for the board is +5 V. This is supplied from the upstream USB port only. The voltages for the hub are generated from 2 different regulators. U21 (TLV70033) takes the BOARD_5V and regulates it down to 3.3 V (refer to Figure 4). The TLV70033 is an LDO that is capable of supplying 200 mA. U22 (LM3674) generates the 1.1-V power rail used for the TUSB8020B core voltage. Figure 5 shows schematics of the power supply circuitry for the hub. The circuit was designed using TI’s Webench Design Tool, and selected for the small PCB footprint and low component cost. BOARD_5V BOARD_5V BOARD_3P3V 3.3V LDO - 200mA R30 10K 0402 1 3 C56 0.1uF 0402 VIN VOUT EN GND 3.3V @100mA 5 2 C52 1.0uF 0402 4 NC C51 1.0uF 0402 U21 TLV70033 SC70-5 Figure 4. TUSB8020B Power Supply (TLV70033) BOARD_5V BOARD_5V BOARD_1P1V R31 10K 0402 3 C53 2.2uF 0402 C57 0.1uF 0402 L3 U22 1 2 VIN SW EN FB 5 4 1.1V @ 450mA 2.2uH@1.3A IND_1008 GND C54 15pF 0402 R32 237K 0402 C55 10uF 0603 LM3674 SOT_23_5 R33 200K 0402 Figure 5. TUSB8020B Power Supply (LM3674) 4 TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback PCB Design www.ti.com 4 PCB Design The PCB stack-up design was chosen to accommodate the 90-Ω impedance of USB 3.0 signal traces. A trace width of 4.4 mils and differential pair spacing of 5 mils is used with this layout. All USB 3.0 traces are routed on the top side of the board and references a solid ground plane that is layer 2. Layer 3 is the power layer and includes the 5- and 1.1-V supplies. The bottom side, layer 4, is where the 3.3-V supply is routed as well as all other traces. To simplify the assembly process, all components are placed on the top side of the board. Figure 6 through Figure 11 show the layout for all 4 layers as welll as the silk screens Figure 6. Top Layer – USB 3.0 Routes TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 5 PCB Design www.ti.com Figure 7. Layer 2 – Ground Plane Figure 8. Layer 3 – Power Plane (+5 V and +1.1 V) 6 TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback PCB Design www.ti.com Figure 9. Bottom Side - +3.3-V Power and Routing Figure 10. Top Side Silk Screen TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 7 PCB Design www.ti.com Figure 11. Bottom Side Silk Screen 4.1 Layout Guidelines All USB 3.0 and USB 2.0 lines must be routed as controlled impedance, high-speed differential pairs. Minimize the use of vias and 90 degree corners in the routing of the high-speed lines. Assure the highspeed lines reference a solid ground plane and the plane is void of cuts and splits to prevent impedance discontinuities. ESD connection points need to be placed in-line with the high-speed signal traces to reduce reflections caused by routing discontinuities. 4.2 PCB Stack-up Figure 12 shows the PCB stack-up used for the TIDA-00287 reference design. Figure 12. PCB Stack-up 8 TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback Verification and Measured Performance www.ti.com 5 Verification and Measured Performance 5.1 Compliance Testing 5.1.1 USB 2.0 – Downstream Port 1 Figure 13. USB 2.0 Downstream Signal Quality Eye Diagram - Port 1 Figure 14. USB 2.0 Downstream Signal Quality Plot - Port 1 TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 9 Verification and Measured Performance 5.1.2 www.ti.com USB 2.0 – Downstream Port 2 Figure 15. USB 2.0 Downstream Signal Quality Eye Diagram - Port 2 Figure 16. USB 2.0 Downstream Signal Quality Plot - Port 2 10 TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback Verification and Measured Performance www.ti.com 5.1.3 USB 2.0 – Downstream Port 1 without ESD Protection Figure 17. USB 2.0 Downstream Signal Quality Eye Diagram - Port 1 Without ESD Protection Device Figure 18. USB 2.0 Downstream Signal Quality Plot - Port 1 Without ESD Protection Device TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 11 Verification and Measured Performance 5.1.4 www.ti.com USB 2.0 – Downstream Port 2 without ESD Protection Figure 19. USB 2.0 Downstream Signal Quality Eye Diagram - Port 2 Without ESD Protection Device Figure 20. USB 2.0 Downstream Signal Quality Plot - Port 2 Without ESD Protection Device 12 TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback Verification and Measured Performance www.ti.com 5.1.5 USB 3.0 – Downstream Port 1 Figure 21. USB 3.0 Downstream CP1 Eye Diagram - Port 1 Figure 22. USB 3.0 Downstream CP0 Eye Diagram - Port 1 TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 13 Verification and Measured Performance 5.1.6 www.ti.com USB 3.0 – Downstream Port 2 Figure 23. USB 3.0 Downstream CP1 Eye Diagram - Port 2 Figure 24. USB 3.0 Downstream CP0 Eye Diagram - Port 2 14 TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated TIDU428 – November 2014 Submit Documentation Feedback Design Options www.ti.com 6 Design Options This section discusses different design options that were evaluated for this project to give the designer flexibility to modify the design. 6.1 ESD Protection We chose the TPD6E05U06 part to provide ESD protection on this design. It was also chosen due to its small size, capability to provide protection of up to 3 differential pairs, and low capacitance. The package allows for flow-through routing. Another option is using 3 single package parts for each USB connector (TPD2EUSB30). This allows more flexibility in board routing. 6.2 TUSB8020B Options The TUSB8020B has an interface for an optional I2C EEPROM or SMBUS host. This can be used for storing vendor information and other start-up parameters. An I2C EEPROM like the AT24C04 or a SMBUS host can be connected to the serial interface for this purpose, but is not a design requirement. In this design a 24-MHz fundamental frequency crystal was used to generate the clock (CTS Frequency Controls #445C25D24M00000). Optionally, a 24-MHz oscillator can be used and connected to XI pin (pin 38). Table 2 lists the options for the TUSB8020B that are set at the rising edge of the Grst# pin (pin 11). Table 2. Power-on Reset Options Signal Name (Pin #) Default Condition SMBUSz/SS_DN2 (pin 22) Pull-Up 0 = SMBbus enabled FPMGT/SMBA1/SS_UP (pin 36) Pull-Up PWRCTL_POL/SS_DN1 (pin 21) Pull-Down GANGED/SMBA2/HS_UP (pin 35) Pull-Up PWRCTL/BATEN(pins 4 and 6) Pull-Down 1 = I2C enabled 0 = downstream power switching supported 1 = downstream power switch not supported 0 = PWRCTL polarity is active high 1 = PWRCTL polarity is active low 0 = Individual port power control supported 1 = Ganged power control supported 0 = Battery charging not supported 1 = Battery charging supported 6.3 Power Delivery Options TI has many options for providing power to downstream USB ports. In the reference design, the TPS2553 is used to reduce component count. This part has an adjustable current limit that is controlled by an external resistor. R28 is used to set the current limit on downstream port 1, and R25 for port 2. The equation used to calculate the current limit is as follows: 23950 V IOSnom (mA) RILIM0.977k: (1) 6.4 Power Options The TUSB8020B requires 1.1 V for core logic and 3.3 V for I/O logic. The current requirements can be seen in the datasheet (SLLSEF6), and TI has many power solutions. Since 3.3 V has a low-power requirement, a low-cost, low-component-count LDO was used to step down the BOARD_5V to 3.3 V. The 1.1-V power rail is generated by an LM3674 – step down switching regulator. TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 15 Schematic 7 www.ti.com Schematic Figure 25 through Figure 30 illustrate the electrical schematics for the TUSB8020B. TUSB8020B BLOCK DIAGRAM Page 5 5V VBUS_OUT_1 TPS2553 Page 4 VBUS_OUT_1 Page 3 PORT 1 DOWNSTREAM PORT 1 DOWNSTREAM PORT 2 Page 2 Page 4 VBUS_OUT_2 UPSTREAM USB PORT USB3.0 TUSB8020B VBUS_IN Page 5 PORT 2 5V VBUS_OUT_2 TPS2553 Page 6 REGULATORS VBUS_IN Figure 25. Schematic (1 of 6) 16 TIDA-00287 2-Port USB 3.0 Hub Reference Design TIDU428 – November 2014 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated Schematic www.ti.com UPSTREAM CONNECTOR 1 2 3 4 6 7 USB3.0 TYPE-A GND5 GND10 D3+ D3- UQFN_14_142X57_20 5 10 D2+ D2- D1+ D1- NC1 NC2 NC3 NC4 NC6 NC7 U16 TPD6E05U06 9 8 220 @ 100MHZ, 2A C1 0603 0.1uF 0402 USB 3.0 TYPE-A PLUG CONNECTOR (RIGHT ANGLE) 12 11 FB1 14 13 BOARD_5V J1 VBUS DM DP GND SSTXN SSTXP GND1 SSRXN SSRXP SHIELD0 SHIELD1 1 2 3 4 5 6 7 8 9 10 11 DM_UP [P3] VBUS_PUP_FB DP_UP [P3] SSTXM_PUP SSTXP_PUP C2 0201RND 0.1uF C3 SSTXM_UP [P3] 0.1uF SSTXP_UP [P3] 0201RND USB3_PLUG CON_SMRT_USB3A_M KEEP CAPS CLOSE TO CONNECTOR SSRXM_UP [P3] SSRXP_UP [P3] ROUTE THESE LINES ON THE TOP SIDE ONLY Figure 26. Schematic (2 of 6) TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 17 Schematic www.ti.com TUSB 2 PORT USB3.0 HUB XTAL_2_SM_197X126 Y1 BOARD_3P3V 24MHz C4 18pF 0402 C5 18pF 0402 R2 R24 DNI 0402 DNI,1M 0402 C6 1uF 0402 UPSTREAM PORT R1 DNI 0402 [P2] SSTXP_UP [P2] SSTXM_UP [P2] SSRXP_UP [P2] SSRXM_UP [P2] DP_UP [P2] DM_UP U1-1 38 39 11 29 28 32 31 26 27 24 9 XI XO GRST# SSTXP_UP SSTXM_UP SSRXP_UP SSRXM_UP DP_UP DM_UP USB_R1 USB_VBUS_UP XI XO GRST# USB_SSTXP_UP USB_SSTXM_UP USB_SSRXP_UP USB_SSRXM_UP USB_DP_UP USB_DM_UP USB_R1 USB_VBUS BOARD_5V 2 3 22 36 21 35 I2C_SCL I2C_SDA PWR_MGMT_EN# PWRCTL_POL GANGED SCL/SMBCLK SDA/SMBDAT SMBUSz/SS_DN2 FPMGT/SMBA1/SS_UP PWRCTL_POL/SS_DN1 GANGED/SMBA2/HS_UP 10 TEST USB_SSTXP_DN1 USB_SSTXM_DN1 USB_SSRXP_DN1 USB_SSRXM_DN1 USB_DP_DN1 USB_DM_DN1 PWRCTL1/BATEN1 OVERCURZ1 USB_SSTXP_DN2 USB_SSTXM_DN2 USB_SSRXP_DN2 USB_SSRXM_DN2 USB_DP_DN2 USB_DM_DN2 PWRCTL2/BATEN2 OVERCURZ2 43 44 46 47 41 42 4 5 SSTXP_DN1 SSTXM_DN1 SSRXP_DN1 SSRXM_DN1 DP_DN1 DM_DN1 EN_PORT1 FLT_PORT1# SSTXP_DN1 [P4] SSTXM_DN1 [P4] SSRXP_DN1 [P4] SSRXM_DN1 [P4] DP_DN1 [P4] DM_DN1 [P4] EN_PORT1 [P5] FLT_PORT1# [P5] 16 17 19 20 14 15 6 8 SSTXP_DN2 SSTXM_DN2 SSRXP_DN2 SSRXM_DN2 DP_DN2 DM_DN2 EN_PORT2 FLT_PORT2# SSTXP_DN2 [P4] SSTXM_DN2 [P4] SSRXP_DN2 [P4] SSRXM_DN2 [P4] DP_DN2 [P4] DM_DN2 [P4] EN_PORT2 [P5] FLT_PORT2# [P5] DOWNSTREAM PORTS TEST TUSB8020B QFP_48_284X284_20_THMPAD R5 90.9K 0402 BOARD_1P1V R6 9.53K 0402 R7 10K 0402 R8 4.7K 0402 R9 4.7K 0402 R4 4.7K 0402 BOARD_3P3V R3 4.7K 0402 U1-2 1 12 18 30 34 45 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD33_1 VDD33_2 VDD33_3 VDD33_4 VDD33_5 VDD33_6 VDD33_7 VDD33_8 PAD 7 13 23 25 33 37 40 48 49 TUSB8020B BOARD_1P1V QFP_48_284X284_20_THMPAD C7 .01uF 0402 C8 0.1uF 0402 C9 0.1uF 0402 C10 0.1uF 0402 C63 .01uF 0402 C11 .01uF 0402 C12 10uF 0402 C64 0.1uF 0402 C65 0.1uF 0402 BOARD_3P3V C13 .01uF 0402 C14 .01uF 0402 C15 0.1uF 0402 C16 0.1uF 0402 C17 10uF 0402 C18 .01uF 0402 C19 .01uF 0402 C60 0.1uF 0402 C61 0.1uF 0402 C62 .01uF 0402 Figure 27. Schematic (3 of 6) 18 TIDA-00287 2-Port USB 3.0 Hub Reference Design TIDU428 – November 2014 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated Schematic www.ti.com GND5 GND10 NC1 NC2 NC3 NC4 NC6 NC7 1 2 3 4 6 7 DOWNSTREAM USB PORTS 1&2 SINGLE USB 3.0 CONNECTOR D3+ D3- U19 TPD6E05U06 UQFN_14_142X57_20 5 10 9 8 D2+ D212 11 220 @ 100MHZ,2A 0603 14 13 VBUS_OUT_PORT_1 [P5] C34 0.1uF 0402 PORT 1 D1+ D1- FB4 J4 12 13 VBUS DM DP GND SSRXN SSRXP GND SSTXN SSTXP SHIELD0 SHIELD1 SHLD2 SHLD3 1 2 3 4 5 6 7 8 9 10 11 DM_DN1 [P3] VBUS_P1_FB DP_DN1 [P3] SSRXM_DN1 SSRXP_DN1 HUB_SSTXM_P1 SSRXM_DN1 [P3] HUB_SSTXP_P1 SSRXP_DN1 [P3] USB3_TYPEA_CONNECTER CON_THRT_USB3A_F3 KEEP CAPS CLOSE TO CONNECTOR C40 0201RND 0.1uF C32 0.1uF SSTXM_DN1 [P3] SSTXP_DN1 [P3] GND5 GND10 D3+ D3- U20 TPD6E05U06 UQFN_14_142X57_20 5 10 D2+ D2- 9 8 VBUS_OUT_PORT_2 [P5] 12 11 FB5 14 13 D1+ D1- NC1 NC2 NC3 NC4 NC6 NC7 1 2 3 4 6 7 0201RND 220 @ 100MHZ,2A C43 0603 0.1uF 0402 PORT 2 SINGLE USB 3.0 CONNECTOR J5 12 13 SHLD2 SHLD3 VBUS DM DP GND SSRXN SSRXP GND SSTXN SSTXP SHIELD0 SHIELD1 1 2 3 4 5 6 7 8 9 10 11 DM_DN2 [P3] VBUS_P2_FB DP_DN2 [P3] SSRXM_DN2 SSRXP_DN2 HUB_SSTXM_P2 SSRXM_DN2 [P3] HUB_SSTXP_P2 SSRXP_DN2 [P3] USB3_TYPEA_CONNECTER KEEP CAPS CLOSE TO CONNECTOR CON_THRT_USB3A_F3 C44 0201RND 0.1uF C42 0.1uF SSTXM_DN2 [P3] SSTXP_DN2 [P3] 0201RND Figure 28. Schematic (4 of 6) TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 19 Schematic www.ti.com USB POWER DELIVERY BOARD_5V C50 0.1uF 0402 C45 4.7uF 0402 U17 1 2 [P3] EN_PORT1 3 EN_PORT1 ACTIVE HIGH ENABLE: R27 47K 0402 IN OUT GND ILIM EN 6 VBUS_OUT_PORT_1 VBUS_OUT_PORT_1 [P4] 5 4 FAULT# FLT_PORT1# TPS2553 R28 28.7K 0402 SOT23_6 FLT_PORT1# [P3] C49 22uF 0603 THIS SETS THE CURRENT LIMIT TO 901.5mA (TYP) BOARD_5V C48 0.1uF 0402 C46 4.7uF 0402 U18 1 2 [P3] EN_PORT2 3 EN_PORT2 ACTIVE HIGH ENABLE: R19 47K 0402 IN OUT GND ILIM EN FAULT# TPS2553 SOT23_6 6 VBUS_OUT_PORT_2 VBUS_OUT_PORT_2 [P4] 5 4 FLT_PORT2# R25 28.7K 0402 FLT_PORT2# [P3] C47 22uF 0603 THIS SETS THE CURRENT LIMIT TO 901.5mA (TYP) Figure 29. Schematic (5 of 6) 20 TIDA-00287 2-Port USB 3.0 Hub Reference Design TIDU428 – November 2014 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated Schematic www.ti.com BOARD_5V BOARD_5V R30 10K 0402 BOARD_3P3V 3.3V LDO - 200mA U21 TLV70033 1 3 C56 0.1uF 0402 EN 3.3V @100mA 5 VOUT 2 GND C52 1.0uF 0402 4 NC C51 1.0uF 0402 VIN BOARD_5V BOARD_5V BOARD_1P1V R31 10K 0402 3 C57 0.1uF 0402 L3 U22 1 C53 2.2uF 0402 SC70-5 2 VIN SW EN FB GND 5 1.1V @ 450mA 2.2uH@1.3A IND_1008 4 C54 15pF 0402 R32 237K 0402 C55 10uF 0603 LM3674 SOT_23_5 R33 200K 0402 BOARD_5V LED BOARD_5V R29 180 0402 D4 LED Blue 0603 Vf=3.3V@20mA Figure 30. Schematic (6 of 6) TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 21 Bill of Materials 8 www.ti.com Bill of Materials Table 3 lists the BOM for this reference design. Table 3. Bill of Materials Item Qty Reference Value Part Description Manufacturer Manufacturer Part Number PCB Footprint 1 16 C1,C8,C9,C10,C15,C16,C34,C43,C 48,C50,C56,C57,C60,C61,C64,C65 0.1uF cap 0402, 0.1uF, +/- 10%, X7R, 16V TDK Corporation C1005X7R1C104K 0402 2 6 C2,C3,C32,C40,C42,C44 0.1uF cap 0201, 0.1uF, +/- 20%, X5R, 6.3V TDK Corporation C0603X5R0J104M030BC 0201RND 3 2 C4,C5 18pF cap 0402, 18pF, +/- 5%, COG (NPO), 50V Murata Electronics North America GRM1555C1H180JZ01D 0402 4 3 C6,C51,C52 1uF cap 0402, 1uF, +/- 10%, X5R, 10V Taiyo Yuden LMK105BJ105KV-F 0402 5 8 C7,C11,C13,C14,C18,C19C62,C63 .01uF cap 0402, 0.1uF, +/- 10%, X7R, 50V Murata Electronics North America GRM155R71H103KA88D 0402 6 2 C12,C17 10uF cap 0402, 10uF, +/- 20%, X5R, 6.3V Samsung CL05A106MQ5NUNC 0402 7 2 C45,C46 4.7uF cap 0402, 4.7uF, +/- 10%, X5R, 6.3V TDK Corporation C1005X5R0J475K 0402 8 2 C47,C49 22uF cap 0603, 22uF, +/- 20%, X5R, 6.3V TDK Corporation C1608X5R0J226M 0603 10 1 C53 2.2uF cap 0402, 2.2uF, +/- 20%, X5R, 6.3V TDK Corporation C1005X5R0J225M 0402 11 1 C54 15pF cap 0402, 15pF, +/- 5%, COG, 50V Venkel C0402COG500-150JNE 0402 12 1 C55 10uF cap 0603, 10uF, +/- 20%, X5R, 6.3.V TDK Corporation C1608X5R0J106M080AB 0603 13 1 D4 LED - Blue LED BLUE, 0805, 104MCD, 20mA Lite-On Inc. LTST-C170TBK 0805 15 3 FB1,FB4,FB5 220 @ 100MHZ,2A EMI Filter Beads, 220 Ohms, 25% MuRata BLM18EG221SN1D 0603 16 1 J1 USB3_PLUG USB 3.0 - A Type R/A Assmann A-USB/3-A-LP/SMT-R CON_SMRT_USB3A_M 17 2 J4,J5 USB3_TYPEA_CONNECTOR Connectors USB 3.0, Super Speed USB - A, Receptacle FCI 10117835-002LF USB - A, Receptacle 18 1 L3 2.2uH@1.3A INDUCTOR 2.2UH 20% 1.3A 1008 Murata LQM2HPN2R2MG0L IND_1008 19 2 R1,R24 DNI DNI DNI DNI 0402 20 1 R2 DNI,1M DNI DNI DNI 0402 21 3 R7,R30,R31 10K RES 0402, 10K, +/- 1%, 1/10W Panasonic Electronic Components ERJ-2RKF1002 0402 22 4 R3,R4,R8,R9 4.7K RES 0402, 4.7K, +/- 1%, 1/16w Vishay Dale CRCW04024K70FKED 0402 23 1 R5 90.9K RES 0402, 90.9K, +/- 1%, 1/16W Yageo RC0402FR-0790K9L 0402 24 1 R6 9.53K RES 0402, 9.53K, +/- 1%, 1/16w Vishay Dale CRCW04029K53FKED 0402 25 2 R19,R27 47K RES 0402, +/- 1%, 1/10W Panasonic Electronic Components ERJ-2RKF4702X 0402 26 2 R25,R28 28.7K RES 0402, 28.7k, +/- 1%, 1/16w Venkel CR0402-16W-2872FT 0402 27 1 R29 180 RES 0402, 180, +/- 1%, 1/16W Panasonic Electronic Components ERJ-2RKF1800X 0402 28 1 R32 237K RES 0402, 237K, +/- 1%, 1/10W Panasonic Electronic Components ERJ-2RKF2373X 0402 29 1 R33 200K RES 0402, 200K, +/- 1%, 1/16W Panasonic Electronic Components ERJ-2RKF2003X 0402 30 1 U1 TUSB8020B Two-Port USB Hub TEXAS INSTRUMENTS TUSB8020B QFP_48_284X284_20_THMPAD 31 3 U16,U19,U20 TPD6E05U06 IEC ESD protection diodes TEXAS INSTRUMENTS TPD6E05U06RVZ UQFN_14_142X57_20 32 2 U17,U18 TPS2553 Power Distribution Switch TEXAS INSTRUMENTS TPS2553DBV SOT23_6 33 1 U21 TLV70033 LDO linear regulator TEXAS INSTRUMENTS TLV70033DCK SC70-5 34 1 U22 LM3674 600 mA Buck Converter TEXAS INSTRUMENTS LM3674MF-ADJ/NOPBTR-ND SOT_23_5 35 1 Y1 24MHz 24 MHz Crystal CTS Freq Controls 445C25D24M00000 XTAL_2_SM_197X126 22 TIDA-00287 2-Port USB 3.0 Hub Reference Design TIDU428 – November 2014 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated Acknowledge and References www.ti.com 9 Acknowledge and References 1. USB 3.0 Electrical Compliance Test Specification 2. Agilent DSA91304A USB 3.0 Receiver Testing TIDU428 – November 2014 Submit Documentation Feedback TIDA-00287 2-Port USB 3.0 Hub Reference Design Copyright © 2014, Texas Instruments Incorporated 23 IMPORTANT NOTICE FOR TI REFERENCE DESIGNS Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers (“Buyers”) who are developing systems that incorporate TI semiconductor products (also referred to herein as “components”). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer’s systems and products. TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design. TI may make corrections, enhancements, improvements and other changes to its reference designs. Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI. TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER’S USE OF TI REFERENCE DESIGNS. TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed. TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguards. Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions. Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer’s safety-critical applications. In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms. No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use. Only those TI components that TI has specifically designated as military grade or “enhanced plastic” are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have not been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.IMPORTANT NOTICE Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated