Multivibrators

advertisement

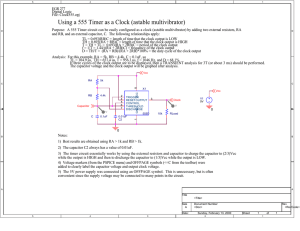

EGR 278 Digital Logic Lab File: N278L9A Lab # 9 Multivibrators A. Objective The objective of this laboratory is to introduce the student to the use of bistable multivibrators (flip-flops), monostable multivibrators (one-shots), and astable multivibrators (clock generators). Switch debouncing is also investigated. B. Materials Breadboard 5V Power Supply Oscilloscope 555 Timer IC 7476 Dual JK Flip-flop Assorted AND, OR, NAND, NOR, XOR, and INVERTER IC’s Assorted resistors and capacitors available in lab C. Introduction Multivibrators A multivibrator is a circuit whose output oscillates between logic HIGH and LOW states, either automatically or due to some input. There are three types of multivibrators: 1) Bistable multivibrators (flip-flops) - These devices have two stable states (Q = 0 and Q = 1). They can easily be switch from one stable state to the other. 2) Monostable multivibrators (one-shots) - These devices have one stable state, but they may enter another unstable state for a certain period of time. 3) Astable multivibrator (clock generator) - These devices oscillate between two unstable states, forming a clock (square wave generator). Flip-Flops A flip-flop is the simplest type of memory cell. Its output, Q, does not depend solely upon its inputs, but also depends on the order in which they are applied. Thus, the flip-flop is not a combinational circuit, but is a sequential circuit. The flip-flop is the key building block of most synchronous sequential circuits. There are four common types of flip-flops. The symbol and truth table for each is shown below. SR flip-flop: S Q R Q CK JK flip-flop: J Q K Q D CK S R Q(t+1) 0 0 1 1 Q(t) 0 1 -- 0 1 0 1 (no change) (reset) (set) (illegal) D flip-flop: Q CK J K Q(t+1) 0 0 1 1 0 1 0 1 Q(t) 0 1 Q(t) T flip-flop: T CK Q (no change) (reset) (set) (toggle) Q Q D Q(t+1) T Q(t+1) 0 1 0 1 0 1 [or Q(t+1) = D] Figure 1: Four common types of flip-flops Q(t) Q(t) (no toggle) (toggle) Page 2 Flip-flops are synchronous devices meaning that the output responds to the synchronous inputs (S, R, J, K, D, or T) only on certain clock edges. There are three main types of triggering: 1) positive-edge triggering - the output Q can only change on the positive (rising) edge of the clock (due to the values of the synchronous inputs). 2) negative-edge triggering - the output Q can only change on the negative (falling) edge of the clock (due to the values of the synchronous inputs). 3) master-slave triggering - the synchronous inputs are “read” on the positive edge of the clock, but the output Q does not respond until the negative edge of the clock. The type of triggering is sometimes indicated by the symbol. Shown below in Figure 2 are JK flip-flops with all three types of triggering. Positive-edge triggered: J Negative-edge triggered: Q CK J Q CK K Master-slave triggered: CK Q K Q J Q C K Q Figure 2: JK Flip-flops with different types of triggering Flip-flops often have asynchronous inputs available also. These inputs are not synchronized with the clock, therefore, the output may respond immediately to changes in these inputs. There are two types of asynchronous inputs commonly used: 1) PRESET (also called SET) - used to preset the output Q to 1 2) CLEAR (also called RESET) - used to clear the output (set Q to 0) Asynchronous inputs are often active-LOW. Therefore, they are typically tied HIGH for normal flip-flop operation. The PRESET or CLEAR may be momentarily set LOW to initialize the flipflop to some desired initial value. The symbol for a flip-flop often show the asynchronous inputs as indicated below in Figure 3. PR J Q CK K CL Q Figure 3: JK Flip-flops with asynchronous PRESET and CLEAR inpu Page 3 Debounced Switches If the input to a flip-flop or sequential circuit is applied with a switch, it is important that the switch is debounced so that only a single transition occurs when the switch is thrown such as is shown in Figure 4A. The contacts in a simple switch will bounce for several milliseconds before settling down allowing several transitions to occur such as is shown in Figure 4B. Since a negative-edge triggered flip-flop reacts to each falling edge of the input clock, the input in Figure 4A would “clock” the flip-flop only once, whereas the input in Figure 4B would clock the flipflop three times. switch thrown switch thrown HIGH HIGH LOW HIGH LOW HIGH LOW LOW t t Figure 4A - Debounced switch Figure 4B - Switch with contact bounce Figure 5 shows three circuits that can be used to debounce switches. 7400 output 7400 output PR J Q output Q output CK K CL Figure 5A: Debounced switch using a JK flip-flop output output Figure 5C: Debounced switch using inverters Figure 5B: Debounced switch using NAND gates Page 4 555 Timer The 555 timer circuit is a popular IC that can be used to implement astable and monostable multivibrator circuits as well as other circuits. The 555 is a linear IC (like an operational amplifier or a voltage regulator) rather than a digital IC, thus it does not necessarily use TTL voltage levels. In fact, the supply voltage for the 555 can range from 4.5V to 18V. If a 5V supply if used, it can easily interface with TTL circuits. A simplified equivalent circuit for the 555 timer is shown below in Figure 6. Vcc Reset 8 4 6 Threshold Upper Comparator _ 2V 3 cc Control 5 Voltage + _ 1V 3 cc + Lower Comparator Trigger 7 Discharge Q flipflop Output Driver 3 Output 2 1 Ground Figure 6: 555 Timer Simplified Block Diagram 555 Timer configured as an astable multivibrator The 555 timer configured as an astable multivibrator (clock generator) is shown below in Figure 7. The device operates essentially as follows: 1) The capacitor C charges until it reaches (2/3)Vcc causing the upper comparator to CLEAR the flip-flop (which sets the output LOW). 2) The capacitor C discharges until it reaches (1/3)Vcc causing the lower comparator to PRESET the flip-flop (which sets the output HIGH). Vcc R A 8 4 Vcc Reset 7 Discharge Output 3 R B 6 C Threshold Trigger 2 Control Voltage 5 Ground 1 0.01 uF Figure 7: 555 Timer connected as an astable multivibrator (clock generator) Page 5 Shown in Figure 8 are the capacitor and output waveforms for the astable multivibrator (clock generator). Capacitor Voltage 2 Vcc 3 Vcc [1 - e 2 3 2 V cc 3 -t/[(R + R )C] Vcc A B ] + 1 3 Vcc -t/( R BC) e 1 V cc 3 time 0 Output Voltage T Vcc T H T L time 0 Figure 8: Capacitor and output waveforms for an astable multivibrator (clock generator) The charge time is given by: TH = 0.693(R A + R B )C The discharge time is given by: TL = 0.693(R B )C The total period is given by: T = TH + TL = 0.693(R A + 2R B )C The frequency of oscillation is given by: f = And the duty cycle is given by: D = (R A 1.44 + 2R B )C TH RA + RB = x 100% T R A + 2R B Note that a 50% duty cycle can be almost achieved by picking RB >> RA . Example: If C = 0.1 µF, RA = 5 kΩ, and RB = 4.4 kΩ, then TH = 651.4 µs, TL = 304.9 µs, T = 956.3 µs, f = 1046 Hz, and D = 68.1 % 555 Timer configured as a monostable multivibrator A monostable multivibrator (one-shot) is a device that will output a HIGH pulse for a specified duration of time each time that the input is triggered. The 555 timer configured as a one-shot is shown below in Figure 9. The device operates essentially as follows: 1) An input trigger causes the lower comparator to SET the flip-flop which makes the output HIGH and turns OFF the transistor which allows the capacitor to begin charging. 2) The capacitor C charges until it reaches (2/3)Vcc causing the upper comparator to CLEAR the flip-flop which shorts out the capacitor and forces the output LOW. Page 6 Vcc R 8 4 Vcc 7 Discharge Reset Output output 3 C 6 Control Voltage 5 Threshold input trigger pulse Trigger 2 Ground 1 0.01 uF Figure 9: 555 Timer connected as a monostable multivibrator (one-shot) Shown in Figure 10 are the input trigger, capacitor, and output waveforms for the monostable multivibrator (one-shot). Input Trigger Voltage falling edge triggers the one-shot Vcc time 0 Capacitor Voltage Vcc [1 - e Vcc -t/(RC) ] 2 V cc 3 time 0 Output Voltage Vcc T time 0 Figure 10: Input trigger, capacitor, and output waveforms for a monostable multivibrator (one-shot) The width of the pulse is given by : (2/3)Vcc ) T = 1.1RC (solve for t when Vcc[1 - e -t/RC] = Example: If C = 0.1 µF and R = 47 kΩ, then T = 1.1(47 kΩ)(0.1 µF) = 5.17 ms. So, each time the one-shot is triggered, an output pulse with a duration of 5.17 ms is produced. Page 7 D. Preliminary Work 1. 2. E. Design a one-shot using a 555 timer that will generate an output pulse that is HIGH for A.BC seconds, where A, B, and C are the last 3 non-zero unique digits of your SSN in Hz. For example, if your SSN is 144-86-8443, then the output pulse should last for 8.43 seconds. Pick a capacitor value that is available in lab (see the list of available capacitor values in the Pinouts handout) or use a capacitor value that you have and use resistance values between 1kΩ and 1 MΩ. Generate full circuit documentation for the circuit. Include a debounced switch at the input and an LED at the output. Design a clock generator using a 555 timer that will generate a clock with a frequency equal to the last 3 non-zero digits of your SSN in Hz. For example, if your SSN is 144-86-8443, then the frequency is 843 Hz.. Use a duty cycle that is somewhat close to 50% (calculate its exact value). Pick a capacitor value that is available in lab (or one that you have) and use resistance values between 1kΩ and 1 MΩ. Generate full circuit documentation for the circuit. Laboratory Work 1. 2. 3. 4. Construct a debounced switch using 2 NAND gates as shown in Figure 5B. Test its operation (simply to see if it produces HIGH and LOW outputs as the switch is moved). Connect a JK flip-flop using a 7476 and test it to complete the truth table shown below. Use a debounced switch to clock the flip-flop. Were the results as expected? Q(t) J K Q(t+1) 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Connect the one-shot designed in step 1 of the Preliminary Work according to the wire table generated. Measure the exact value of all resistors and capacitors used. Record the designed values and the measured values in a table. Test the one-shot and record the duration of the output pulse and compare it to the designed value. Demonstrate proper operation of the circuit to the instructor. In your report, recalculate the expected time for the output using the measured component values and compare the time to measured using a stop watch in lab. Connect the clock generator designed in step 2 of the Preliminary Work according to the wire table generated. Measure the exact value of all resistors and capacitors used. Record the designed values and the measured values in a table. View and accurately sketch the output clock pulse and the capacitor voltage. Measure values for TH, TL, T, D, and f from the oscilloscope. Compare these to calculated values using measured component values. Demonstrate proper operation of the circuit to the instructor. Page 8 5. Connect the output of the clock generator in the previous step to the clock input of a JK flip-flop in the toggle mode as shown in Figure 11. View the output of the clock generator and the output of the flip-flop simultaneously (the clock output near the top of the screen and the flip-flop output near the bottom) and accurately sketch the results. From the sketch can you tell if the flip-flop is positive or negative edge triggered? Discuss how the frequency of the flip-flop output compares with the frequency of the clock output. A JK flip-flop in the toggle mode is sometimes called a divide-by-2 circuit. Why? 555 timer clock generator output 1 J Q 1 K Q Figure 11: 555 clock generator and JK flip-flop in the toggle mode (J = K = 1)