Lecture 6: Universal Gates - Computer Science and Engineering

advertisement

Lecture 6: Universal Gates

CSE 140: Components and Design Techniques for

Digital Systems

Spring 2014

CK Cheng, Diba Mirza

Dept. of Computer Science and Engineering

University of California, San Diego

1

Combinational Logic: Other Types of

Gates

§ Universal Set of Gates

§ Other Types of Gates

1) XOR

2) NAND / NOR

3) Block Diagram Transfers: Converting a

circuit to an equivalent circuit

2

Universal Set

Universal Set: A set of gates such that every switching

function can be implemented with gates in this set.

Ex:

{AND, OR, NOT}

{AND, NOT}

{OR, NOT}

3

Universal Set

Universal Set: A set of gates such that every Boolean

function can be implemented with gates in this set.

Ex:

{AND, OR, NOT}

{AND, NOT} OR can be implemented with AND &

NOT gates a+b = (a’b’)’

{OR, NOT} AND can be implemented with OR &

NOT gates ab = (a’+b’)’

{XOR} is not universal

{XOR, AND} is universal

4

iClicker

Is the set {AND, OR} (but no NOT gate)

universal?

A. Yes

B. No

5

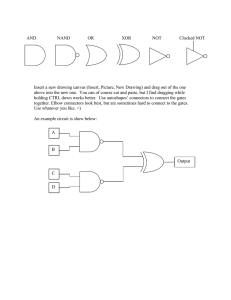

Universal Set

{AND, NOT} combined into a single gate:

{OR, NOT} combined into into a single gate:

6

Implementing NOT, AND and OR using NAND gates

1. Implementing NOT using NAND

2. Implementing AND using NAND

3. Implementing OR using NAND

7

Implementing NOT, AND and OR using NOR gates

1. Implementing NOT using NOR

2. Implementing OR using NOR

3. Implementing AND using NOR

8

Universal gates {XOR, AND}

1. Implementing NOT using XOR

1

X

1 = X.1’ + X’.1 = X’ if constant “1” is available.

2. Implementing OR using XOR and AND

Same as implementing OR using AND and NOT except NOT is

implemented using XOR as shown above

9

Universal Set

Remark: Universal set is a powerful

concept to identify the coverage of a

set of gates afforded by a given

technology.

10

Other Types of Gates

1) XOR

X Y = XY’ + X’Y

X

XY’

Y

X’Y

(a) Commutative X Y = Y

X

(b) Associative (X Y) Z = X

(Y Z)

(c) 1

X = X’

0

X = 0X’ + 0’X = X

(d) X X = 0,

X

X’ = 1

11

e) if ab = 0 then a b = a + b

Proof: If ab = 0 then

f) X

XY’

X’Y

a = a (b+b’) = ab+ab’ = ab’

b = b (a + a’) = ba + ba’ = a’b

a+b = ab’ + a’b = a b

(X + Y)

X = ??

To answer, we apply Shannon’s Expansion.

12

Shannon’s Expansion (for switching functions)

Formula: f (x,Y) = x * f (1, Y) + x’ * f (0, Y)

Proof by enumeration:

If x = 1, f (x,Y) = f (1, Y) : 1*f (1, Y) + 1’*f(0,Y) = f (1, Y)

If x = 0, f(x,Y) = f (0, Y) : 0*f (1, Y) + 0’*f(0,Y) = f(0, Y)

13

Back to our problem…

X

XY’

Þ X

X’Y

(XY’)

(X + Y)

X=?

(X’Y) (X + Y)

If X = 1, f (1, Y) = 1

If X = 0, f (0, Y) = 0

X = f (X, Y)

Y’ 0 1

0 Y Y

1=Y

0=0

Thus, f (X, Y) = XY

14

XOR gates

iClicker: a+(b

A. Yes

B. No

c) = (a+b) (a+c) ?

15

2) NAND, NOR gates

NAND, NOR gates are not associative

Let a | b = (ab)’

(a | b) | c ≠ a | (b | c)

16

3) Block Diagram Transformation

a) Reduce # of inputs.

ó

ó

17

b. DeMorgan’s Law

ó

(a+b)’ = a’b’

ó

(ab)’ = a’+b’

18

c. Sum of Products (Using only NAND gates)

ó

ó

Sum of Products (Using only NOR gates)

ó

ó

19

d. Product of Sums (NOR gates only)

ó

ó

20

NAND, NOR gates

Remark:

Two level NAND gates: Sum of Products

Two level NOR gates: Product of Sums

21

Part II. Sequential Networks

Memory / Timesteps

Clock

Flip flops

Specification

Implementation

22

Reading

[Harris] Chapter 3, 3.1, 3.2

23