Current Testing

advertisement

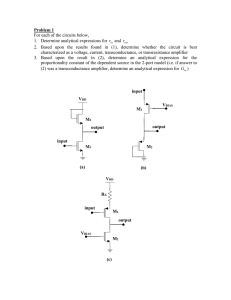

Outline Digital Testing: Current Testing Based on text by S. Mourad "Priciples of Electronic Systems" 1/22/2005 Why current testing Effect on propagation delays Measurement of current Test pattern generation Subthreshold current Effect of deep submicron Fab. 2, 2001 Copyrights(c) 2001, Samiha Mourad 2 Current Testing Basics What is Current Testing CMOS circuits operate with normally negligible static current (power) Also called IDDQ Testing Measurement of the supply, VDD, quiescent current the sum of all off-state transistors Useful only for CMOS circuits Limitation due to shrinking technology But, a defect that causes an appreciable static current can be detected by measuring the supply current, IDDQ Technique used since inception of CMOS technology Limitation due to shrinking technology IDDQ Testing IDD --- Current flow through VDD Q --- Quiescent state IDDQ Testing --- Detecting faults by monitoring IDDQ Fault effect is easy to detect Many realistic faults are detectable VDD IDD Inputs CMOS circuit Advantages of IDDQ Testing Outputs ATPG is relatively simple Test length is shorter Built-in current sensing is possible Normal IDDQ: ~10-9Amp. Abnormal IDDQ: >10-5Amp. 1 Calculation of Defect Likelihood Inductive Fault Analysis (IFA) Defect spot • A systematic method to generate realistic fault lists • Taking into account —Circuit fabrication technology —Defect statistics —Physical layout Extra conductance Missing insulator Whether a fault presents depends on 1. Size of spot (defect statistics) 2. Distance of two conductors (layout) 3. Fabrication process IDDQ Distribution How Does it Work? Frequency Good Defective Mg Md Apply a test pattern Wait for the transient to settle down Measure the current Needed: IDDQ (Md - Mg) should be an easily measurable quantity Dynamic Current How to generate the patterns How to measure the current But, first current characteristics Inverter: Good and Faulty IDDQ Vout VOH Vi n Vout CL VOL t I t 2 Current for the NAND Tree A NAND Tree s a z b c d Measurement requires the current settling down Circuit to show the effect of the delays shown on the next slide External Measurement IDDQ Measurement Measurement may interfere with the measured current V A successful measurement should be: easily placed between the CUT and the bypass Capacitor of the power pin Capable of measuring small currents Non intrusive, no drop of VDD Fast measurement few ns per pattern V dd CUT Power Supply R Two types: on- and off-chip ∆t (a) (b) t BICS Based on Bipolar Transistor Current Sensing Structures R and Differential Amplifier (Maly, ICCAD '88) VDD Power Supply CUT VDD CMOS R VR V Shorts causing struck -at faults Shorts causing bridging faults & oxide pinholes Junction leakages NO defect (c) Virtual Ground Switching circuit When large IDDQ exists, V>VR and Fail flag is set. VDD-GND Shorts Power Supply C bp CMOS Module V I GND (b) CUT φ1 VR + - φ2 φ1 Module (a) R Pass/Fail Flag V NO defect VR The switching circuit may switch off a faulty module to prevent large power consumption Defect 3 Internal Measurement Analysis of a Short I Z = AB + C A B VDD-GND Shorts Z A Vdd C B (a) (b) Vdd Bridging Faults IC Vdd Vdd Vdd IDDQ Gate oxide pinholes DUT Vref A=B=0 VGND (a) A=1 B=0 A=1 B=1 For the shorted pMOS transistor, find: a path form V DD to G ND through this transistor, then AB = 11 is needed to detect this short using I DDQ VGND No defect GND A=0 B=1 (c) Floating gates & junction leakages V.drop Comparator No defect (b) Defect Vref Detecting Short Faults Test Pattern Generation (TPG) Mainly two methods: B A based on switch level using graph representation as for layout based on leakage fault models C C Z Z A B (a) (b) Graph or Switch Based TPG NAND Gate sg Z A Leakage Fault Model Vdd A Vdd B Z A Z A C B bs B A dg C B A Z bg B bd sd C GND B GND n-graph p-graph (a) (b) The combined graph (c) Path A,A,B to test shorts on A transistors Path B,A,B to test shorts on B transistors IO bg bd bs ds gd 00 0 0 0 0 0 01 n y n n y 10 y n n n y 11 0 0 0 0 0 gs 0 n y 0 N 00 22 43 00 Assuming all possible shorts between the four nodes,bulk, source, gate, and drain results in 6 tuples The pattern is the conjunction of In & out, IO Some combinations are impossible: 00, 11 To simplify, the 6 tuples are represented in octal number as shown in column N of the table The notation is used to characterize a 2-input NAND For instance for I/O=10 transistor fault code is N=438 =100011 and represents the following faults: bg, gd, gs 4 Characterizing a NAND Impact of Deep Submicron B P1 P2 Z O N1 A C N2 B N1 0 22 0 26 0 70 43 0 N2 P1 0 0 0 43 0 0 43 43 0 0 26 0 43 26 0 0 Deep submicron transistors work at lower Vt The lower Vt the higher IDDQ The discrepancy between the faulty and non-faulty IDDQ is narrowing P2 0 43 0 0 0 43 26 0 (b) I/O octal code, eg.: 6=110=>A=1,B=1,O=0 (a) 10-6 10-8 I off 10-10 I off 10-12 -0.5 0 0.5 1.0 Gate-Source voltage (V GS ),V 1.5 Change of Current with Body bias and Temperature Controlling IDDQ Reverse biasing the substrate Cooling the devices Using dual threshold voltage Partitioning the circuit to manageable IDDQ 1.E+01 Normalized IDDQ to IDDQ of 0.18um Gate at 150C without Body Bias A K 0 1 2 3 4 5 6 7 Drain Current (I ), A D Octal fault vector code for each transistor 1.E+00 Inverter with input state of 0 Lg=.18u @150C Lg=.25u @150C Lg=.18u @25C Lg=.25u @25C Lg=.18u @-50C Lg=.25u @-50C 150C 1.E-01 25C 1.E-02 1.E-03 -50C 1.E-04 -3.5 -2.5 -1.5 -0.5 0.5 Vbs (V) Source or Drain Break Faults D C1 Stuck-open Faults B C3 G C3 C4 G C2 C2 Cgb 1 B x C y T1 = 1 1 1 1 0 T2 = 0 0 0 1 ? O Cgb May drift to intermediate voltage S A B C D O D A C4 d1 In a gate B C1 d3 A B D C When T2 is applied, charge sharing among x, y and o occurs, hence may draw a large current in the inverter. 5 Other Faults That Can Be Detected Circuit Constraints • Gate-oxide short (Hawkins ITC85, D&T 86) • Most stuck-at faults (Fritzmeyer ITC-90) To ensure IDDQ detectability, two conditions must be satisfied: • Latch -up • Delay faults 1. Normal IDDQ must be small • Any other fault due to extra conductor, missing isolating layer, excess well/substrate leakage, etc. 2. Faults must result in large IDDQ A Good Circuit That May Be Identified As Being Faulty A BF That Cannot Be Detected By IDDQ B=110 x=11? large current z=x0? a 0 A=011 Φ x x y y Φ Sel=0 if AB=10 Φ 1 1 MUX 0 Output When the third pattern AB=10 is applied, change sharing between x, z occurs, and a large current may exist in the inverter. However the output is still correct. b Φ Φ Φ Φ=1: a=0, b=1 Φ=1: Eventually x=y (as one signal will dominate), no big current Problem due to feedback loop Problem due to high impedance node Problems with Dynamic Logic φ o Transistor Group a φ Output O p x Inputs y G3 G2 Transistor group (TG) --"Channel -connected component" A φ b Connections between two TGs are unidirectional B G1 Problems: 1. Large current in normal circuits due to charge sharing 2. Very few faults are detected because of the precharge property (no direct path VDD-GND) 3. Fault masking of BF(a, b) due to BF(o, p) C E Control direction or loop can be defined D 6 A Minimum Set of Design & Test Rule for IDDQ Testing (Lee FCAD'92) A1. Gate and drain (or source) nodes of a transistor are not in the same TG. A2. No conducting path exists from VDD to GND during steady state. A3. Each output of a TG is connected to VDD or GND during steady state. A4. No control loops among TGs exist. A5. The bulk (or well) of an n-(p-)type transistor is connected to GND (VDD). A6. During testing, each PI is controlled by a monitored power source. Fault Simulation 1. Fault models --- Bridging, break, stuck-open, stuck-at ? 2. Fault list generation --- need inductive fault analysis 3. Fault coverage ? 4. Easy for bridging and stuck-on faults Results of Design & Test Rules Theorem 1: All irredundant single BFs in a circuit satisfying A1- A6 can be detected using IDDQ testing. Theorem 2: For a circuit satisfying A1-A6, a test detecting a single BF f also detects all multiple BFs that contain f. Theorem 3: If any one of A1-A6 is removed, then circuits exist for which IDDQ testing cannot give correct test results. Strategies for dealing with circuits not satisfying each rule are required to ensure IDDQ detectability. Fault simulation for BFs If A1- A6 are satisfied, then fault simulation is quite simple 1. Perform a good circuit simulation for the given test pattern. 2. Any BF between a node with logic 1 and a node with logic 0 is detected. 5. Difficult for break and stuck-open faults No simulation on faulty circuit is needed. 6. Stuck-at faults may or may not be modeled as short to VDD or GND No fault list enumeration is needed. Test Generation 1. Conventional test generation for stuck-at faults can be modified to detect BFs. Test generator for BFs Again, assume A1 - A6 are satisfied 2. No fault propagation. 3. Must make sure the faults result in a conducting path between VDD and GND. Switch level test generation may be necessary. 4. Break and stuck-open faults are difficult to detect. 1. For the BF (a, b) to be detected, add an XOR gate with its inputs connected to a and b. 2. The test generator work is simply to set the output of the XOR gate to be 1. No Fault propagation. 7 Current monitoring Techniques External Devices (Hawkins 86, 89) TEST POWER SUPPLY ATE ATE RM Current Supply Monitor S (STROBE) VDD BICS DUT DUT CUT External monitoring Test Fixture Built-In Current Sensor VDD pin N I DD CN Transistor conducts in normal mode and is open in test mode DUT Problems: VSS pin 1. Current resolution is limited. 2. Test equipment must be modified. 3. Current cannot be measured at the full speed of the tester. 4. Cannot partition circuit . Built-in Current Sensors (BICSs) QTAG IDDQ Monitor (Baker, ITC '94) VDD VDD Test VDD MON Vref VDD PSU Power Supply Unit ATE VDD DUT Inputs VDD VDD Pullup Pullup Pulldown Pulldown Pass /Fail t VDD VDD VDD Pullup Pullup Pullup inputs Normal : t = 1 Test :t = 0 tout = 1 if no fault = 0 if fault exists ... Pulldown Pullup ... Pulldown Pulldown Pulldown ... ... MT Gnd t MT ... MTD Gnd BICS Test Improvement on Favalli's design Favalli (JSSC-90) MT Outputs Sometimes called ISSQ testing BICS Based on Logic Threshold inputs CUT Vss Current sensing in the interface VDD CUT Outputs Inputs DUT IDDQ MONITOR Di Pass /Fail OR Ip Bypass Do BICS tout MTD MTD Gnd MT tout Merge all MT and MTD respectively MTD Gnd 8 BICS Based on Integrators Improvement on Favalli's Design VDD VDD Pullup Pullup VDD Pullup inputs Pulldown TVDD MP7 CMOS Logic Circuit ... Pulldown level translator converts the input high (low) voltage V to a logic 0 (logic 1) atx Miura & Kinoshita (ITC -92) VDD Pulldown MP1 MP3 MP8 MP2 X V ... MN2 MN1 MP4 MN4 MN3 Y Tout MP5 MN4 MN8 Tmode MN7 MT I tout Using BiCMOS design N GND GND MTD I-V Translator Level Translator BICS Based on Dual Power Supply & Operational Amplifier Verhelst's BICS Patent VDD '=5V VDD ' I2 A1 O1 M + IDD I1 Vref In Virtual Short + Io CUT Z Iref VDD' ~ VDD I DD ~ I0 O2 Iz V'DD=5V Current Conveyor Ix VDD Vin=3V Vout+ VoutI DD VSS CMP VDD IRS II+ VDD=3V Threshold detector CUT output O1 of the op-amp. A1 adjusts the gate voltage of Ts. IDD is mirrored to T1 for current comparison in CMP BICS Based on Current Conveyor Virtual Short RS - SPC Ts T1 Vss Virtual Short Current Mirror Integral Circuitry Fault effect can be accumulated through several clock cycles Gnd CMS MP6 MN6 Fault indication Virtual short VDD~Vin Infinite input impedance of OP I -=0 and IRS=IDD Advantages of Built-In Current Sensors (BICS) • Higher test rate compared to external devices Iy • Easier to partition circuits Threshold Detector Fail/Pass CUT • Easier to control current resolution • Suitable for mixed -mode circuits • Built-In self test capability achievable • Lower test equipment cost Virtual short Current Conveying VDD ~ VDD' Iy ~ Ix • On-Line testing possible 9 Disadvantages of BICS • Impact on circuit performance • Reliability of itself • Area overhead • Power consumption 10